Р§ЫЕFPGAСЌди13ЃКСщЛюЖЈжЦЁЊЁЊХфжУЕчТЗ

ЗЂВМЪБМфЃК2016-7-27 16:30

ЗЂВМепЃКrousong1989

|

Р§ЫЕFPGAСЌди13ЃКСщЛюЖЈжЦЁЊЁЊХфжУЕчТЗ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1c0nf6Qc

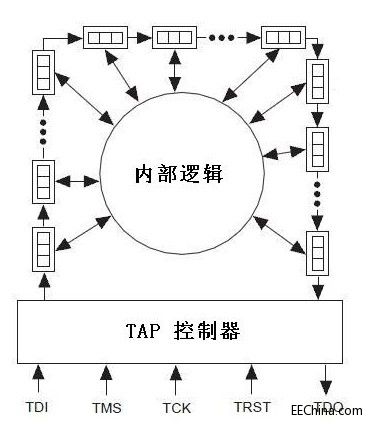

ЩЯЪРМЭАЫЪЎФъДњЃЌСЊКЯВтЪдааЮЊзщжЏЃЈJoint Test ActI/On GroupЃЌМђГЦJTAGЃЉжЦЖЈСЫжївЊгУгкPCBКЭICЕФБпНчЩЈУшВтЪдБъзМЁЃИУБъзМгк1990 ФъБЛIEEE ХњзМЮЊIEEE1149.1-1990 ВтЪдЗУЮЪЖЫПкКЭБпНчЩЈУшНсЙЙБъзМЁЃЫцзХаОЦЌЩшМЦКЭжЦдьММЪѕЕФПьЫйЗЂеЙЃЌJTAGдНРДдНЖрЕФБЛгУгкЕчТЗЕФБпНчЩЈУшВтЪдКЭПЩБрГЬаОЦЌЕФдкЯпЯЕЭГБрГЬЁЃ FPGAЦїМўЖМжЇГжJTAGНјаадкЯпХфжУЃЌJTAGБпНчЩЈУшЕФЛљБОдРэШчЭМ2.7ЫљЪОЁЃдкFPGAЦїМўФкВПЃЌБпНчЩЈУшМФДцЦїгЩTDIаХКХзїЮЊЪ§ОнЪфШыЃЌTDOаХКХзїЮЊЪ§ОнЪфГіЃЌаЮГЩвЛИіКмДѓЕФвЦЮЛМФДцЦїСДЁЃЖјJTAGЭЈЙ§ећИіМФДцЦїСДЃЌПЩвдХфжУЛђепЗУЮЪFPGAЦїМўЕФФкВПТпМзДЬЌЛђепИїИіI/Oв§НХЕФЕБЧАзДЬЌЁЃ

ЭМ2.7 JTAGБпНчЩЈУшдРэ дкетРяЮвУЧВЛЙ§ЖрЕФбаОПJTAGЕФдРэЁЃЖдгкЕчТЗЩшМЦРДЫЕЃЌJTAGЕФЫФИіаХКХTCK/TMS/TDI/TDOЃЈTRSTаХКХвЛАуПЩвдВЛгУЃЉвдМАЕчдДЁЂЕиСЌНгЕНЯТдиЯпМДПЩЁЃ ЫЕЕНFPGAЕФХфжУЃЌетРяВЛЕУВЛЬсвЛЯТЫћУЧКЭCPLDФкВПДцДЂНщжЪЕФВЛЭЌЁЃCPLDгЩгкДѓЖМЪЧЛљгкPROMЛђFlashРДЪЕЯжПЩБрГЬЬиадЃЌвђДЫЖдЫћУЧНјаадкЯпБрГЬЪБОЭвбНЋХфжУЪ§ОнСїЙЬЛЏКУСЫЃЌжиаТЩЯЕчКѓЛЙФмЙЛдЫааЙЬгаЕФХфжУЪ§ОнЁЃFPGAДѓЖМЪЧЛљгкSRAMРДЪЕЯжПЩБрГЬЬиадЃЌЛЛОфЛАЫЕЃЌЭЈЙ§JTAGЪЕЯждкЯпБрГЬЪБЃЌдкБЃГжВЛЖЯЕчЕФЧщПіЯТЃЌFPGAФмЙЛе§ГЃдЫааЃЌЖјвЛЕЉЕєЕчЃЌSRAMЪ§ОнЖЊЪЇЃЌFPGAдђвЛЦЌПеАзЃЌЮоЗЈМЬајдЫааШЮКЮМШЖЈЙІФмЁЃвђДЫЃЌFPGAЭЈГЃашвЊЭтЙввЛИігУгкБЃДцЕБЧАХфжУЪ§ОнСїЕФPROMЛђFlashаОЦЌЃЌЮвУЧЭЈГЃГЦжЎЮЊЁАХфжУаОЦЌЁБЃЌCPLDдђВЛашвЊЁЃ вђДЫЃЌЖдгкFPGAЦїМўЃЌЮвУЧШєЯЃЭћЫќВњЦЗЛЏЃЌПЩвдЭбЛњЃЈPCЛњЃЉдЫааЃЌФЧУДОЭБиаыдкАхМЖЩшМЦЪБПМТЧЫќЕФХфжУЕчТЗЁЃвВВЛгУЬЋЕЃаФЃЌЦфЪЕFPGAГЇЩЬЕФЦїМўЪжВсРявВЛсИјГіЭЦМіЕФХфжУаОЦЌКЭВЮПМЕчТЗЃЌДѓЖрЧщПіЯТвРКљТЋЛЦАБуПЩЁЃЕБШЛСЫЃЌАхМЖЩшМЦЛЙЪЧТэЛЂВЛЕУЕФЃЌгаМИИіЗНУцЪЧашвЊзЂвтЕФЃК Ёё ХфжУаОЦЌОЁСПППНќFPGAЁЃ Ёё ПМТЧХфжУаХКХЕФЭъећадЮЪЬтЃЌБивЊЪБдіМгзшПЙЦЅХфЕчзшЁЃ Ёё ВПЗжХфжУв§НХПЩвдБЛИДгУЃЌЕЋЪЧвЊНїЩїЪЙгУЃЌвдУтгАЯьЦїМўЕФЩЯЕчХфжУЙ§ГЬЁЃ FPGAХфжУЕчТЗЕФЩшМЦЪЧЗЧГЃживЊЕФЃЌЯрЙиаХКХв§НХЭЈГЃЖМЪЧЙЬЖЈВЂЧвзЈгУЕФЃЌашвЊВЮПМЙйЗНЭЦМіЕчТЗНјааСЌНгЁЃ |

ЭјгбЦРТл