电子行业人士带你入行之纳米制程小白篇

发布时间:2016-6-29 10:16

发布者:芯易网

|

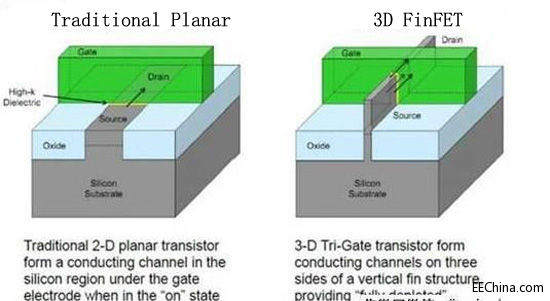

这些年,英特尔、三星、台积电在制程上的恩恩怨怨,堪比武侠小说中恩怨情仇。这些大厂的争斗均是围绕14纳米和16纳米,那么问题来了,这个14纳米和16纳米有什么好争的?下面芯易网就来简单做一下介绍。 纳米到底有多小 想要了解纳米,我们来看看芯易网对它的定义:纳米(nm)又称毫微米,1纳米=10-9米(度娘说),到底有多小呢?以我们的指甲厚度为例,一般的指甲厚度为0.1毫米,也就是将指甲横向切成10份,那么每份也就差不多1纳米。 了解纳米过后,我们再来看看缩小制程的意义。众所周知,缩小电晶体的最主要目的,是为了让往里面塞更多的芯片,防止因芯片的增加而让电晶体变大。此外,还可以增加CPU的运算速率、降低能耗。简单的说,这也符合未来轻薄化的趋势。 纳米制程是什么 纳米制程是指芯片中的线能缩小到的尺寸,举个例子,长得跟下图一样的传统电晶体,L代表着我们期望缩小的闸极长度,从Drain 端到 Source 端,电路可以节省更多的路径,以达到减少耗电量的目的。

要想判断电晶体的电流是否在流通,可以给绿色的方块(Gate端)供给电压,正常情况电流会从Drain端流动到Source段(没电压供给的话电流是不会动的)。这样可以表示1和0(电脑也是以0和1做运算的),至于为什么要用1和0表示,可以去查阅布林代数。 制程缩小也会有物理的限制 当然,纳米制程并非说缩小就能缩小的,当电晶体缩小到20纳米的时候,就会出现漏电的量子物理问题。这个时候就要导入FinFET(Tri-Gate)来改善这个问题。导入这项技术后,电晶体漏电的问题就会减少(并非是完全消除)。 此外,FinFET(Tri-Gate)还可以增加下层和Gate 端接触的面积。一般来说接触面有且只有一个平面,但采用该技术后接触面将变得立体化,进而轻而易举地增加接触的面积。从而在保持一样的接触面积的情况下,缩小Source-Drain 端,这对于设计者和制造者们来说至关重要。 想要理解缩小制程的难度,可以参考芯易网(https://www.xinyiic.com/)这个小实验:用100个小珠子在桌子上以10X10的比例排列成正方形,再在上面盖一张相同尺寸的纸。紧接着用笔刷掉旁边的小珠子,使其最后形成一个10X5比例的长方形。从这个实验不难看出,要达成这个目标非常不容易,由此可以了解到,各大厂面临的困境有多么艰难。 三星和台积电都在完成14 纳米、16 纳米 FinFET 的量产,并以此为资本争夺下一代iPhone的芯片代工业务,随着电子行业的竞争升级,我们将能看到更多省电又轻薄的手机。 比如目前全球领先芯片制作商都在追的10nm线程,不仅如此,厂商们还把目光投向7纳米甚至是5纳米,相信不久的将来会有更精湛的产品呈现在我们面前。敬请期待吧! |

网友评论