基于嵌入式系统的隔离硬件设计

发布时间:2010-7-25 00:00

发布者:conniede

|

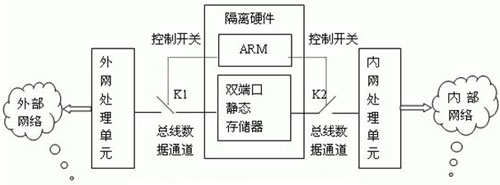

Internet的迅猛发展使信息共享的程度进一步提高,因而信息安全的问题也日益突出,这时唯一的解决方法只能是主动解决信息安全和网络安全问题。 1 引言 目前国内外采用最多的、最普遍的网络安全措施是使用防火墙类软件,但是防火墙类软件本身存在两大先天缺陷:其一是防火墙隔离的网络还是基于TCP/IP协议来进行信息交换的,而TCP/IP 协议存在漏洞,它无法防止协议本身的漏洞;其二是防火墙的运行离不开操作系统,操作系统和防火墙软件都存在漏洞,因而不能阻止由这些漏洞而引起的网络安全问题[1]。因此,开发相应的应用系统是必要的。本文在对已有的防火墙技术及物理隔离技术进行分析的基础上,提出了带缓冲区的双通道实时开关技术,通过该技术所设计出的网络隔离器能满足实时数据的传输,同时本文提出了一种物理隔离环境下数据安全转发的技术构思,该方案使得网络隔离器有很好的安全性能。 2 物理隔离技术原理 2.1 简介 物理隔离是指内部网络不得直接或间接地连接外部网络即互联网[2]。物理隔离技术通过中断内部网络与外部网络的连接,不支持TCP/IP 协议,不依赖于操作系统,解决了目前网络安全存在的根本性问题,即由于操作系统漏洞和TCP/IP 协议漏洞所带来的安全问题,有效地防止了恶意代码、病毒以及网络入侵的发生,满足了网络安全的机密性、完整性、可用性、可控性和可审查性要求。 2.2 物理隔离技术 目前,国内外普遍采用的物理隔离技术有: 单硬盘物理隔离卡和双主板物理隔离技术。 2.2.1 单硬盘物理隔离卡 这种技术是将计算机的单个硬盘从物理层上分割为公共和安全两个分区,每个分区各自安装一套操作系统。在操作中,用户工作在安全状态和公共状态两个互相排斥的操作系统环境下,从而实现内外网的安全隔离。这种技术的缺点是不能传输实时数据。 2.2.2 双主板物理隔离技术 两块主板之间通过非网络方式的一个双端口RAM 进行数据的传输,双端口RAM 分为两个区,第一个区是内网客户端向外网服务器单向传输数据的通道。第二个区是外网客户端向内网服务器单向传输数据时的通道。在平时内外网是断开的,双端口RAM处于断开状态。当有数据要传输时,内外网才通过双端口RAM 进行数据传输[3]。 3 网络隔离器技术原理 目前网络隔离器的实时开关实现方式主要有基于SCSI 的开关技术和基于总线的开关技术两种。 基于总线的实时开关技术的网络隔离器采用双端口静态存储器(Dual Port SRAM)配合基于独立的ARM的控制电路,双端口各自通过开关与独立的计算机主机连接,如图1所示。ARM作为独立的控制电路保证双端口静态存储器的每一端口上存在一个开关,且两个开关不能同时闭合即K1×K2=0。 基于SCSI 开关技术的网络隔离器和图1相似,只是数据通道换为SCSI 硬盘接口,而存储介质使用的是SCSI 硬盘,控制单元使用专门设计的硬件电路板实现。  图1 基于总线实时开关技术的网络隔离器示意图 该系统的数据交换原理如下:以数据由外部网到内部网的传递为例,首先外部主机将由外部网接收到的数据进行TCP/IP 协议和应用协议的剥离,将其还原为原始数据,同时对数据进行完整性和安全性的审查;审查通过后,将安全的数据传递给交换设备,然后内部主机接收到这批数据,在对它们进行TCP/IP协议和应用协议的封装后,把它们发送到内部网。反之亦然。 以内网接收电子邮件为例,当外网需要有数据到达内网的时候,外部的服务器立即发起对隔离设备的非TCP/IP 协议的数据连接,隔离设备将所有的协议剥离,将原始的数据写入存储介质。根据不同的应用,可能有必要对数据进行完整性和安全性检查,如防病毒和恶意代码等。 一旦数据完全写入隔离设备的存储介质,隔离设备立即中断与外网的连接。转而发起对内网的非TCP/IP 协议的数据连接。隔离设备将存储介质内的数据推向内网。内网收到数据后,立即进行TCP/IP 的封装和应用协议的封装,并交给应用系统。 这个时候内网电子邮件系统就收到了外网的电子邮件系统通过隔离设备转发的电子邮件。在控制台收到完整的交换信号之后,隔离设备立即切断隔离设备于内网的直接连接。 如果这时,内网有电子邮件要发出,隔离设备收到内网建立连接的请求之后,建立与内网之间的非TCP/IP 协议的数据连接。隔离设备剥离所有的TCP/IP 协议和应用协议,得到原始的数据,将数据写入隔离设备的存储介质。必要的话,对其进行防病毒处理和防恶意代码检查。然后中断与内网的直接连接。控制台收到信息处理完毕后,立即中断隔离设备与外网的连接,恢复到完全隔离状态。 每一次数据交换,隔离设备经历了数据的接受,存储和转发三个过程。由于这些规则都是在内存和内核里完成的,因此速度上有保证,可以达到100%的总线处理能力[4]。 |

网友评论