ЛљгкADV202ЕФЧЖШыЪНЪгЦЕбЙЫѕЯЕЭГШэгВМўЩшМЦ

ЗЂВМЪБМфЃК2010-7-23 00:38

ЗЂВМепЃКconniede

|

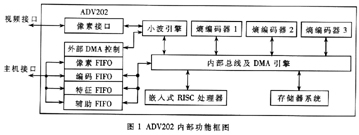

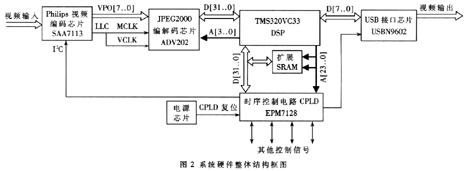

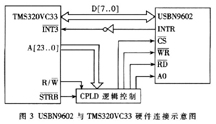

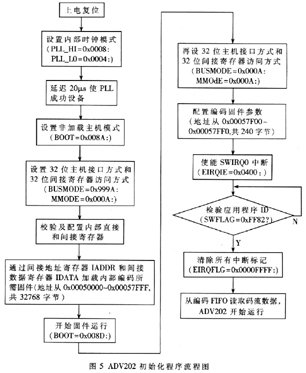

ЙњМЪБъзМЛЏзщжЏISOКЭЙњМЪЕчаХСЊУЫITUгк2000Фъ12дТе§ЪНЭЦГіСЫJPEG2000БъзМЃЌИУБъзМВЩгУвдРыЩЂаЁЖЩБфЛЛЮЊжїЕФЖрНтЮіБрТыЗНЗЈЃЌОпгааэЖргХСМЕФЬиадЃЌШЛЖјвЛжБЮДЛёЕУЙуЗКЕФгІгУЁЃADЙЋЫОгк2004ФъЭЦГіСЫФмЪЕЪБбЙЫѕКЭНтбЙЫѕИпжЪСПдЫЖЏЭМЯёКЭОВжЙЪ§зжЭМЯёЕФJPEG2000БрНтТыаОЦЌADV202ЁЃБОЮФЛљгкADV202ЩшМЦвЛИіЭъећЕФЧЖШыЪНЪгЦЕбЙЫѕЯЕЭГЃЌЦфжаАќРЈгВМўЕчТЗЩшМЦКЭШэМўСїГЬЩшМЦЃЌИУЯЕЭГОпгаUSBНгПкЃЌжЇГжШШВхАЮЃЌЮоашжїЛњПижЦЁЃ 1 ADV202аОЦЌНщЩм ADV202ЪЧУРЙњADЙЋЫОаТНќЭЦГіЕФвЛПюгУгкЪгЦЕКЭИпДјПэОВжЙЭМЯёбЙЫѕЕФЕЅЦЌIPEG2000(ISOЃЏIECl5444-1ЭМЯёбЙЫѕБъзМ)БрНтТыаОЦЌЃЌЪЧЕБНёЪаГЁЩЯЮЉвЛОпгаЪЕЪБбЙЫѕКЭНтбЙЫѕБъзМ(SD)ЪгЦЕаХ КХКЭИпЧхЮњЖШ(HDTV)ЪгЦЕаХКХЕФаОЦЌЃЌзЈРћЕФПеМфИпаЇЕнЙщТЫВЈ(SURF)ММЪѕЪЙЦфОпгаЕЭЙІКФКЭЕЭГЩБОЕФаЁВЈбЙЫѕЁЃЫќЬсЙЉЕФзЈгУЪгЦЕНгПкПЩвдЮоЗьСЌНгЕНЩОITU.R-BT656ЃЌSMPTE125MЁЂSMPTE293M[525p]ЕШБъзМЕФЪ§зжЪгЦЕНгПкЃЌСщЛюЕФвьВНSRAMЗчИёЕФжїЛњНгПкдЪаэЮоЗьСЌНгЕНДѓЖрЪ§16ЃЏ32ЮЛЕФЮЂПижЦЦїКЭASICЦїМўЁЃ ADV202ЕФФкВПЙІФмПђЭМШчЭМ1ЫљЪОЃЌЪфШыЕФЪгЦЕЛђЭМЯёЪ§ОнНјШыЪгЦЕНгПкКѓОЙ§НтНЛДэДЋЪфЕНаЁВЈБфЛЛв§ЧцжаЁЃдкаЁВЈв§ЧцжаЃЌУПжЁЭМЯёЛђУПИіЭМПщЭЈЙ§5ЃЏ3Лђ9ЃЏ7ТЫВЈЦїЗжНтГЩаэЖрзгДјЃЌЩњГЩЕФаЁВЈЯЕЪ§аДШыФкВПМФДцЦїжаЁЃьиБрТыЦїНЋЭМЯёЪ§ОнБрТыЮЊЗћКЯJPEG2000БъзМЕФЪ§ОнЁЃФкВПDMAв§ЧцЬсЙЉДцДЂЦїжЎМфЕФИпДјПэДЋЪфвдМАИїФЃПщКЭДцДЂЦїжЎМфЕФИпадФмДЋЪфЁЃФкВПFIFOЬсЙЉЯёЫиЪ§ОнЁЂТыСїЪ§ОнЁЂЬиеїЪ§ОнКЭИЈжњЪ§ОнЕФДцДЂПеМфЃЌМШПЩгЩЭтВПжїЛњЭЈЙ§БъзМЕижЗЖСаДжмЦкжБНгЗУЮЪЃЌвВПЩвдВЩгУDREQЃЏDACKавщЭЈЙ§DMAЗНЪНЗУЮЪЛђзЈгУгВМўЮеЪжЛњжЦЗУЮЪЁЃжїЛњНгПкЬсЙЉ16ЃЏ32ЮЛЕФПижЦзмЯпКЭ8/16/32ЮЛЕФЪ§ОнДЋЪфзмЯпЃЌгУгкЖдФкВПМФДцЦїЕФХфжУЁЂПижЦКЭзДЬЌДЋЕнвдМАбЙЫѕЪ§ОнСїЕФДЋЪфЁЃ  2 ЪгЦЕбЙЫѕЯЕЭГгВМўЩшМЦ 2ЃЎ1 ЯЕЭГгВМўећЬхЙЙМм ЯЕЭГгВМўећЬхПђМмШчЭМ2ЫљЪОЃЌРДздЕчЪгЛњЛђЩуЯёЛњЕФЕЅТЗPAL/NTSCжЦЪНЕФЪгЦЕаХКХЃЌОЙ§SAA7n3БрТыЮЊSAV/EAVФЃЪНЁЂITUЃЎRЁЊBT656 YUV4ЃК2ЃК2ИёЪН(8ЮЛ)ЕФЪгЦЕаХКХЃЌгЩVPO[7..0]ДЋЪфЕНADV202ЕФЪгЦЕНгПкЁЃдкADV202ФкВПЃЌЪгЦЕаХКХОЙ§гВМўБрТыВњЩњЃЎjp2ИёЪНЕФЪгЦЕаХКХЃЌгЩжїЛњНгПкD[31..0]ЪфШыЕНTMS320VC33 DSPЁЃОDSPбЙЫѕКѓЕФЪгЦЕаХКХгЩUSBНгПкаОЦЌUSBN9602зЊЛЛКѓЭЈЙ§USBПкЪфГіЁЃСэЭтЃЌDSPЛЙЭЈЙ§Ъ§ОнзмЯпD[31..O]КЭЕижЗзмЯпA[3..]ЖдADV202ФкВПжБНгМАМфНгМФДцЦїНјааХфжУЃЌМгдиADV202БрТыФЃЪНЫљашЕФЙЬМў(гЩADЙЋЫОЬсЙЉ)ЃЌЖдADV202БрТыЪ§НјааЩшжУЁЃUSBПкжЛзїЮЊбЙЫѕЪ§ОнСїЕФЪфГіПкЃЌгЩDSPЭъШЋПижЦЁЃ  2ЃЎ2 DSPаЁЯЕЭГ ГігкЖдЯЕЭГвзЪЕЯжадКЭадМлБШЕФПМТЧЃЌDSPаОЦЌбЁдёЂђЙЋЫОЕФ32ЮЛИпадФмЪ§зжаХКХДІРэЦїTMS320VC33ЁЃTMS320VC33ЙЄзїдк75MlkжїЦЕЪБЃЌдЫЫуФмСІПЩДя150MFLOPSЃЌПЩвдЗУЮЪЕФзмДцДЂПеМфЮЊ16MЁС32bitЃЌГЬађПеМфЁЂЪ§ОнПеМфКЭIЃЏOПеМфЖМАќКЌдкећИі16MЁС32bitПеМфжаЃЌЧвЭГвЛБржЗЁЃЦЌФкЬсЙЉСЫ34KЁС32bit SRAMЃЌПМТЧЕНЯЕЭГДІРэЖдЯѓЪЧЪгЦЕаХКХЃЌвЊЧѓНЯДѓЕФГЬађПеМфКЭЪ§ОнПеМфЃЌЦЌФкRAMЭЈГЃВЛФмТњзуЯЕЭГвЊЧѓЃЌвђЖјдкDSPЦЌЭтвЊНјааДцДЂЦїРЉеЙЁЃ DSPЭтВПРЉеЙСЫСНЦЌCY7C1041V33 (256KЁС16bit)SRAMКЭ1ЦЌSST39VF400A(256KЁСl6bit)FLASHЁЃСНЦЌCY7C1041V33АДееЪ§ОнЮЛРЉеЙЗНЪНРЉеЙГЩЮЊ256KЁС32bitЕФЪ§ОнДцДЂПеМфЃЌгУгкДцДЂбЙЫѕКѓЕФЪгЦЕЪ§ОнЁЃDSPЙЄзїдкЮЂМЦЫуЛњЃЏв§ЕМФЃЪН(MCBL/MP=1)ЯТЃЌSST39VF400AгУгкДцДЂDSPЕФв§ЕМГЬађЁЃ 2ЃЎ3 ЯЕЭГЪБађПижЦЕчТЗ ЯЕЭГЪБађПижЦЕчТЗгЩвЛЦЌAltera EPM7128 CPLDаОЦЌЙЙГЩЃЌЭъГЩЕФжївЊЙІФмгаЃК (1)НЋDSPЭЈгУIЃЏOв§НХаХКХXFlЁЂXF0РЉеЙЮЊI2CзмЯпЫљашЕФSCLЁЂSDAаХКХЃЌЭъГЩDSPЖдSAA7113ЕФГѕЪМЛЏЩшжУЃЛ (2)ВњЩњADV202ЕФЦЌбЁаХКХCSКЭИДЮЛаХКХRESETЃЌНЋDSPЕФЖСаДаХКХR/WРЉеЙЮЊADV202ЕФЖСаХКХRDМАаДаХКХWEЃЛ (3)ВњЩњDSPЭтРЉДцДЂЦїSRAMКЭFLASHЕФНгПкаХКХЃКЕижЗвыТыбЁЭЈаХКХCEЁЂаДТіГхаХХWEЁЂЖСаХКХOEЕШЃЛ (4)ВњЩњUSBN9602ЕФНгПкаХКХЃКЦЌбЁаХКХCSЁЂЖСаХКХRDЁЂаДаХКХWRЁЂЕижЗв§НХаХКХA0ЁЃ 2ЃЎ4 USBНгПкЩшМЦ USBN9602ЪЧУРЙњЙњМвАыЕМЬхЙЋЫОЭЦГіЕФвЛПюзЈгУUSBНгПкаОЦЌЃЌжЇГжUSBlЃЎ1БъзМЁЃФкВПОпгаНЯДѓЕФFIFOЃЎПЩвдЛКДцДѓСПЪ§ОнЃЌДгЖјМѕЧсДІРэЦїЕФИКЕЃЁЃдкБОЯЕЭГжаЃЌUSBN9602ЭЈЙ§ВЂааНгПкгыTMS320VC33ЯрСЌЃЌНгПкаХКХгЩCPLDПижЦЃЎЙЄзїгкЗЧзмЯпИДгУФЃЪН(MODE0=OЃЌMODEl=0)ЃЌСЌНгЪОвтЭМШчЭМ3ЫљЪОЁЃUSBN9602ВйзїЪБађЪЧЯШЭљЕижЗМФДцЦїжааДШыЕижЗЃЌШЛКѓЭЈЙ§Ъ§ОнЪфШыМФДцЦїКЭЪ§ОнЪфГіМФДцЦїЖСаДЪ§ОнЃЌЖјЕижЗМФДцЦїКЭЪ§ОнМФДцЦїЕФбЁдёдђЪЧЭЈЙ§AOЪЕЯжЕФЁЃ  2ЃЎ5 ЪБжгаХКХЕФЩшМЦ БОЯЕЭГбЁгУ3ЦЌОЇеёЃЌЦфжа24ЃЎ576MHzОЇеёЬсЙЉSAA7113ЫљашЕФЭтВПЪБжгЃЌLLCВњЩњЕФ27MHzЪБжгЪфГіаХКХЬсЙЉИјADV202БрТыаОЦЌЪЙгУЃЛ5VЙЉЕчЕФЁЃ15MHzОЇеёЬсЙЉИјCPLDЃЌВЂОЙ§CPLDМфНгЬсЙЉИјDSPЪЙгУЁЃДгЖјНтОі СЫВЛЭЌЕчЦНжЎМфЕФЦЅХфЮЪЬтЃЌDSPФкВПЫјЯрЛЗЪЙгУЁС5ФЃЪН(CLKMDO=CLKMDl=1)ЃЌЙЄзїжїЦЕЮЊ75MHzЃЛ48MHzОЇеёЬсЙЉUSBN9602ЫљашЕФЪфШыЪБжгЁЃдкЕчТЗАхЩшМЦжаЃЌЪБжгаХКХгІОЁПЩФмНгНќЯргІЪфШыв§НХЁЃ 2ЃЎ6 ЕчдДМАЯЕЭГИДЮЛЕчТЗЕФЩшМЦ БОЯЕЭГашвЊЫФжжЕчдДЙЉЕчЃК5VЁЂ3.3VЁЂ1.8VКЭ1.5VЁЃЦфжаЃЌ5VгЩЯЕЭГЭтВПЕчдДЬсЙЉЃЌ3.3VЁЂ1.8VКЭ1.5VгЩTIЙЋЫОЕФЕчдДаОЦЌTPS767D301ЭЈЙ§5VБфЛЛЬсЙЉЁЃ TPS767D301ПЩНЋ5VЕФЕчдДЪфШызЊЛЛЮЊ3.3VЕФЙЬЖЈЕчдДЪфГіКЭ1.5~5.5VЕФПЩБфЕчдДЪфГіЃЌЭЌЪБВњЩњCPLDЕФИДЮЛаХКХЁЃ 3 ЪгЦЕбЙЫѕЯЕЭГШэМўЩшМЦ 3ЃЎ1 ЯЕЭГШэМўСїГЬщъзмЬхЩшМЦ БОЯЕЭГЕФШэМўЩшМЦжївЊЗжЮЊDSPГѕЪМЛЏГЬађ(dspinit.c)ЁЂI2CЦїМўSAA7113ГѕЪМЛЏГЬађ(iicЃЎc)ЁЂADV202ГѕЪМЛЏГЬађ(init202ЃЎc)ЁЂDSPжїПижЦГЬађ(dspetlЃЎc)вдМАuSBЭЈбЖШэМўЕФЩшМЦЁЃаЉГЬађШЋВПдкDSPЩЯЭъГЩЁЃгУCгябдПЊЗЂDSPГЬађПЩвдЫѕЖЬПЊЗЂжмЦкЃЌЬсИпГЬађПЊЗЂЕФаЇТЪЃЌвВПЩвдЪЙГЬађЕФПЩЖСадЁЂПЩвЦжВадДѓДѓЬсИпЃЌВЂЧвФмЮЊЯЕЭГЕФИФНјКЭЩ§МЖЛЛДњДјРДМЋДѓЕФБуРћЃЛЖдгкCгябдБраДЕФДњТыЃЌВЩгУгХЛЏБрвыЦїЩњГЩИпаЇТЪЕФЛуБрДњТыЃЌПЩЬсИпГЬађЕФдЫааЫйЖШЃЌМѕЩйФПБъДњТыЕФЖШЁЃЙЪдкЯЕЭГШэМўЕФзмЬхЩшМЦЩЯЃЌВЩШЁСЫвдЩЯЗНЗЈЁЃЯЕЭГШэМўСїГЬЭМШчЭМ4ЫљЪОЁЃ  3.2 жївЊГЬађЪЕЯжОйР§ ADV202ГѕЪМЛЏГЬађ(init202ЃЎc)жївЊЭъГЩвдЯТЙІФмЃК (1)аЃбщКЭХфжУADV202ФкВПжБНгМФДцЦїКЭМфНгМФДцЦїЃЛ (2)МгдиБрТыФЃЪНЯТADV202ЫљашЕФЙЬМўГЬађЃЛ (3)ЖдЙЬМўХфжУМФДцЦїНјааХфжУЃЌЩшжУЦфЙЄзїзДЬЌЃЛ (4)МьбщгІгУГЬађIDЃЛ (5)ЧхГ§жаЖЯБъМЧЃЌЪЙADV202НјШыдЫаазДЬЌЁЃ ADV202ГѕЪМЛЏСїГЬЭМШчЭМ5ЫљЪОЁЃ  БОЯЕЭГОпгаЬхЛ§аЁЁЂЪЕЪБадКУЁЂбЙЫѕаХКХвзЛжИДЕШгХЕуЃЌПЩвдЙуЗКгІгУгкЗЧЯпадБрМЯЕЭГЁЂдЖГЬБеТЗМрЪгЯЕЭГЁЂЪгЦЕаХКХВЩМЏЯЕЭГЁЂЭМЯёКЭЪгЦЕЕЕАИЯЕЭГЁЂИпжЪСПЪгЦЕЛсвщЯЕЭГЕШЁЃЫцзХADV202ЕФЙуЗКгІгУЃЌJPEG2000ММЪѕБиНЋГЩЮЊвЕНчЭМЯёЪгЦЕбЙЫѕЕФжїСїММЪѕжЎвЛЁЃ |

ЭјгбЦРТл