恒比定时甄别器(CFD)电路具体实现探讨

发布时间:2016-3-10 09:55

发布者:designapp

|

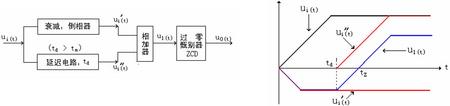

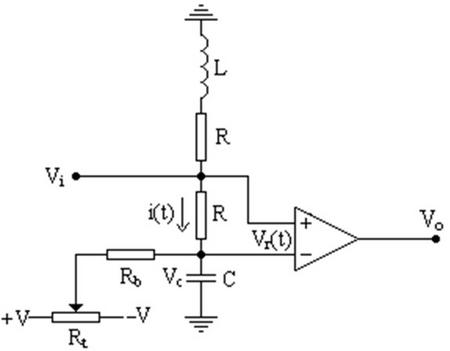

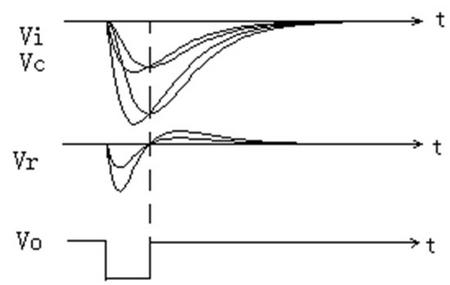

介绍PET系统中定时方法时有介绍到目前大部分使用到的是CFD方法,CFD是Constant Fraction Discriminator的缩写。 这里对CFD具体方法概念,不再赘述,本文笔者个人带着学习的态度来给大家介绍下该方法电路的具体实现。为了介绍方便,我们还是将CFD的实现框图摆出来,如图1所示。  图1:CFD原理框图 因为需要精确定时,所以在前面博文中,笔者详细介绍了,当图1中的输入信号的幅度不同时,如果采用双阈值检测,那么会出现时间晃动,在上述链接博文的图2和图3有非常形象的展示。 而上述图1就可以非常理想的避免这个问题,我们看到不管输入信号的幅度怎么变化,图1右侧的tz时刻(即过零时刻)都会保持固定,这就是我们所需要的,即每次hit我们都能进行精确的定时。(这里,大家一定要看懂右侧图,首先输入信号为黑线,上面红线表示经过延迟后的输入,下面红线是经过衰减并倒相的输入,最后蓝线就是上述二者相加得到的结果,蓝线和横轴相交产生了过零点) 有了这原理框图,那么剩下的就是具体实现,图1左侧中,分别有衰减、倒相、延迟、加法器以及过零检测等主要电路模块,后面我们将对它们一一进行详细的具体实现介绍。 双极性信号成形方法 如图2所示,输入信号Vi直接连到比较器的同相输入端,比较器的反相输入端信号Vc是Vi的低通滤波输出,它在时间上比输入信号滞后。比较器的同相、反相输入端之间的电压差为: Vr(t)=Vi(t)-Vc(t)=R*i(t)=RCdVc(t)/dt  图2:双极性成形电路 在电容器上的电压达到峰值之后,积分电阻上的电流方向改变,引起比较器输出翻转。由于电阻电容组成的是一个线性网络,Vr(t)的过零与输入信号的幅度无关,从而实现了恒比定时功能。  图3:CFD输出 注:图1中反相可以通过图2中的放大器实现一个减法器来实现;而RC滤波器来实现一个延时,这样在整个CFD电路中就实现了所谓的无延迟线的CFD。 |

网友评论