FPGA研发之道(8)架构设计漫谈(三)时钟和复位

发布时间:2016-2-29 14:10

发布者:designapp

|

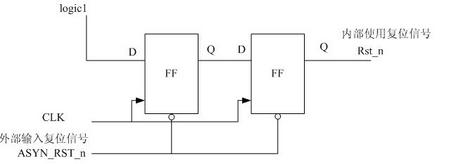

接口确定以后,FPGA内部如何规划?首先需要考虑就是时钟和复位。 时钟:根据时钟的分类,可以分为逻辑时钟,接口时钟,存储器时钟等; (1)逻辑时钟取决与逻辑的关键路径,最终值是设计和优化的结果,从经验而不是实际出发:低端FPGA(cyclone spantan)工作频率在40-80Mhz之间,而高端器件(stratix virtex)可达100-200Mhz之间,根据各系列的先后性能会有所提升,但不是革命性的。 (2)接口时钟,异步信号的时序一般也是通过FPGA片内同步逻辑产生,一般需要同步化,即接口的同步化采样。某些接口的同步时钟一般是固定而精确的,例如下表所示,如SERDES的时钟尽量由该BANK的专用时钟管脚输入,这样可保证一组SERDES组成的高速接口时钟偏斜一致。  (3)外部存储器时钟:这里时钟主要为LPDDR/DDR2/DDR3等器件的时钟,一般来说FPGA的接口不用工作在相应器件的最高频率。能够满足系统缓存数据的性能即可,但是一般这些IP的接口都规定了相应的最小时钟频率,因为这些接口状态机需不停进行外部器件的刷新(充电),过低的频率可能会引起刷新的问题,造成数据丢失或者不稳定。 (4)另外一些需要输出的低速时钟,例如I2C、MDIO、低速采样等操作,可以通过内部分频得到。不用通过PLL/DCM产生所需时钟。在XILINX的FPGA中,禁止PLL产生的时钟直接输出到管脚上,而ALTERA的器件可以如此操作。解决此类问题的方法可通过ODDR器件通过时钟及其180度相位时钟(反向)接入的时钟管脚分别采样0、1逻辑得到。 因为有了DCM/PLL这些专用产生时钟的器件,似乎产生任意时钟输出都是可能是,但实际例化的结果,时钟的输出只能选取某些范围和某些频率,取决于输入时钟和分频系数,CLK_OUT = CLK_IN *(M/N) 。这些分频系数基本取整数,其产生的频率也是有限的值。 复位:根据复位的分类,FPGA内部复位可以分为硬复位,逻辑复位、软复位等; 硬复位:故名思议,即外部引脚引入的复位,可以在上电时给入,使整个FPGA逻辑配置完成后,能够达到稳定的状态,这种复位重要性在于复杂单板上除了FPGA外,可能还有多个器件(CPU、DSP),其上电顺序不同,在未完成全部上电之前,其工作状态为不稳定状态。这种复位引脚可以通过专用时钟管脚引入,也可通过普通I/O引入,一般由单板MCU或者CPLD给出。 逻辑复位:则是由FPGA内部逻辑产生,例如可以通过计数产生,等待一段时间开始工作,一般等待外部某些信号准备好,另一种FPGA内部逻辑准备好的状态信号,常见的有DCM/PLL的LOCK信号;只有内部各逻辑准备好后,FPGA才能正常工作。另外FPGA内部如设计逻辑的看门狗的话,其产生的复位属于这个层次。 软复位:严格的说,应属于调试接口,指FPGA接收外部指令产生的复位信号,用于复位某些模块,用于定位和排除问题,也属于可测性设计的一部分。例如FPGA通过EMIF接口与CPU连接,内部设定软复位寄存器,CPU通过写此寄存器可以复位FPGA内部单元逻辑,通过写内部寄存器进行软复位,是复杂IP常用的功能接口。调试时,FPGA返回错误或无返回,通过软复位能否恢复,可以迅速定位分割问题,加快调试速度。 复位一般通过与或者或的方式(高电平或、低电平与),产生统一的复位给各模块使用。模块软复位信号,只在本模块内部使用。 问题:同步复位好、还是异步复位好? XILINX虽然推荐同步复位,但也不一概而论,复位的目的是使整个系统处于初始状态,这根据个人写代码经验,这些操作都可以,前提是整个设计为同步设计,时钟域之间相互隔开,复位信号足够长,而不是毛刺。下面推荐一种异步复位的同步化方式,其电路图如下:  时钟和复位基本上每个模块的基本输入,也是FPGA架构上首先要规划的部分,而不要用到才考虑,搞的整个设计到处例化DCM或者输出LOCK进行复位,这些对于工程的可维护性和问题定位都没有益处。《治家格言》说:“宜未雨而绸缪,毋临渴而掘井。这与FPGA时钟和复位的规划是同一个意思。 |

网友评论