逻辑分析仪我也DIY(三)—PLL后复位问题

发布时间:2016-2-19 09:04

发布者:designapp

|

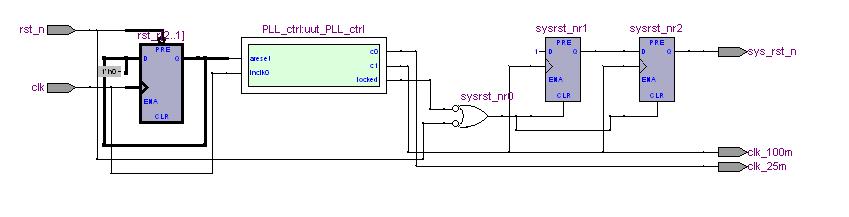

关于M4K的问题还没有结束。主要问题在于想利用M4K来存储要显示到VGA屏幕上的字模数据,而昨天为了方便开了一个很大位宽的M4K,结果就照成了M4K的利用率大大下降,原来不到8K的数据居然占用了7个M4K块,感觉不爽。所以今天绞尽脑汁是想出了解决办法,同时也为其他字符的显示方法开了绿灯。 具体方法不在此讨论,不过现在原来占用7个M4K的字模改成了32位宽*224,规规矩矩的占用了2个M4K块。此外把常用的8*16的ASCII字符字模数据都存到了M4K初始化ROM里了,这全都是体力活,耗费了不少精力。主要问题是字模软件和altera提供的标准ROM初始化文件的格式没法搞成一致。400多个字数据都是手工编号,小指头现在还隐隐作痛。不过显示的技术难点解决了,感觉还是蛮开心的。 其次,对于采样频率(采样周期)做了细化,不再是原来单一的只能为100MHz的采样率,现在可以有10档可调的采样频率。因为采样率设置后的显示还没有继续搞定,所以暂时不做进一步的测试。 因为这个工程里的两个时钟都是用的PLL产生的,所以有必要探讨一下使用了PLL输出时钟作为系统工作时钟时的复位逻辑设计。特权同学的一点愚见,愿抛砖引玉,期待高手指点。 以前的很多博文里都谈过异步复位、同步释放等等的问题,那么在系统复位后PLL时钟输出前,即系统工作时钟不确定的情况下,怎么考虑这个复位的问题呢?  上图是特权同学的这个工程里的复位设计,先用FPGA的外部输入时钟clk将FPGA的输入复位信号rst_n异步复位、同步释放处理一下,然后这个复位信号输入PLL,同时clk也输入PLL。我的设计初衷是在PLL输出时钟有效前,系统的其它部分都保持复位状态。PLL的输出locked信号在PLL有效输出之前一直是低电平,PLL输出稳定有效之后才会拉高该信号。所以这里就把前面提到的FPGA外部输入复位信号rst_n和这个locked信号相与作为整个系统的复位信号,当然了,这个复位信号也是需要让合适的PLL输出时钟异步复位、同步释放处理一下。 |

网友评论