Лљгкcyclone EP1C6 ЕФLEDДѓЦСЩшМЦЗНАИ

ЗЂВМЪБМфЃК2010-7-22 14:52

ЗЂВМепЃКvinda

|

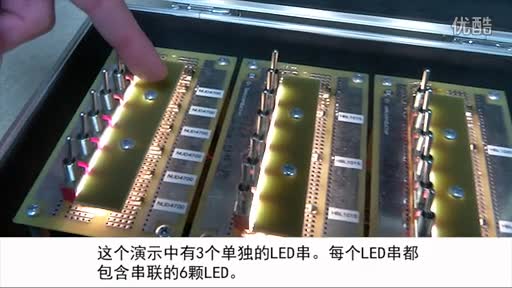

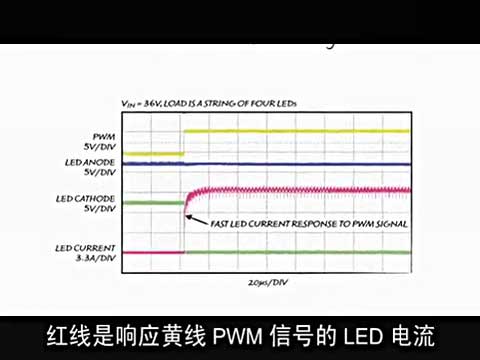

ФПЧАВЩгУЕФLEDДѓЦСФЛЯдЪОЯЕЭГЕФПижЦЕчТЗЃЌДѓЖргЩЕЅИіЛђЖрИіCPUМАИДдгЕФЭтЮЇЕчТЗзщГЩЃЌетжжЕчТЗЩшМЦЃЌЕЅЦЌЛњБрГЬБШНЯИДдгЃЌећИіЕчТЗЕФЕїЪдБШНЯТщЗГЃЌПЩППадКЭЪЕЪБадКмФбЕУЕНБЃжЄЁЃеыЖдетжжЧщПіЃЌНщЩмвЛжжЛљгкcyclone EP1C6ЕФLEDДѓЦСФЛЩшМЦЗНАИ,ИУЩшМЦЗНАИЮоаыЭтЙвFLASH ROMКЭRAMЃЌЮоаыШЮКЮЭтВПЙІФмЕчТЗЃЌЫљгаЙІФмОљгЩвЛЦЌcyclone EP1C6КЭвЛЦЌЕЅЦЌЛњSPCE061AРДЪЕЯжЃЌОпгаЪ§ОнДІРэЫйЖШПьЁЂПЩППадИпЕФЬиЕуЁЃЦфжаFPGAФкВПЫЋПкRAMЕФдЫгУЃЌЮЊВЛЭЌзмЯпМфЕФЪ§ОнЭЈаХЬсЙЉСЫвЛИіаТЕФНтОіЗНАИЁЃЁЁ 1 ЯЕЭГНсЙЙМАЙІФмИХЪі ЩшМЦЖдЯѓЪЧвЛПщОпга192ЁС128ИіКьЩЋLEDЕуеѓЕФЕчзгЦСЁЃећПщЕчзгЦСЪЧФЃПщЛЏЕФНсЙЙЃЌУП4Иі16ЁС16ЕФЕуеѓПщЮЊвЛИіЕЅдЊЃЌЙВ3ЁС8ИіетбљЕФЕЅдЊЁЃЦСЩЯвЊЧѓСЌајЯдЪО5ЦСФкШнЃЌЧвУПЦСОпгаЩЯЯТзѓгввЦЖЏЕШЖЏЛаЇЙћЃЌЪЕМЪгІгУжажїПижЦЪвОрРыЕчзгЦСдМЮЊ200УзЁЃНсКЯЩшМЦЖдЯѓЕФвЊЧѓКЭДѓЦСФЛЩшМЦЕФЬиЕуЃЌЯЕЭГНсЙЙПђЭМШчЭМ1ЫљЪОЁЃ  ЭМ1 ЯЕЭГПђЭМ LEDДѓЦСЩшМЦЯЕЭГгЩШ§ИіжївЊЕЅдЊзщГЩЃКЩЯЮЛЛњЭМЯѓ/ЮФзжБрМгыЗЂЫЭВПЗжЕЅдЊЁЂжїПиАхЕЅдЊЁЂLEDЕчзгЦСЁЃЯЕЭГЩЯЮЛЛњгЩвЛЬЈPCЛњРДПижЦЃЌжївЊЪЧБрМЁЂЗЂЫЭЭМЯѓ/ЮФзжаХЯЂЕНжїПиАхЃЌЖјжїПиАхЖдетаЉЪ§ОнНјааДІРэКѓЗЂЫЭЕНДѓЦСФЛЩЯЯдЪОГіРДЁЃ 2ЯЕЭГгВМўЩшМЦ ЯЕЭГгВМўЩшМЦжївЊЪЧЖджїПиАхЕФЩшМЦЃЌжїПиАхЕФжївЊЙІФмАќРЈЃКЪ§ОнЭЈбЖЁЂЪ§ОнДцДЂЁЂЪ§ОнДІРэЁЂЩЈУшПижЦЕШЁЃДЋЭГLEDДѓЦСЩшМЦгЩзїЮЊЪ§ОнДцДЂЦїЕФFLASH ROMКЭЪ§ОнДІРэЛКДцЦїЕФRAMЁЂCPUКЭПЩБрГЬТпМЦїМўFPGA/CPLDЁЂзїЮЊЪ§ОнЩЈУшЛКГхЧјЕФRAMзщГЩЃЌЦфНсЙЙШчЭМ2ЫљЪОЁЃ  ЭМ2 ДЋЭГLEDДѓЦСЩшМЦжїПиАхНсЙЙЭМ ДЋЭГжїПиАхгВМўЩшМЦашвЊНЯЖрЕФЭтЮЇЦїМўЃЈгаЕФЩшМЦжаЛЙВЛжЙвЛИіCPUКЭCPLDЃЉЃЌВЛНігВМўНсЙЙКЭСЌЯпИДдгЃЌЖјЧвЩшМЦГЩБОНЯИпЁЃДЫЭтЃЌгЩгкLEDДѓЦСФЛЪ§ОнСПКмДѓЃЌИїИіЗжСЂДцДЂЦїжЎМфЁЂЕЅЦЌЛњгыFPGA/CPLDжЎЧАЪ§ОнЪЕЪБПЩППЕФДЋЪфвВЪЧвЛИіЮЪЬтЁЃЮЊНтОіетаЉЮЪЬтЃЌжїПиАхгВМўЕчТЗЕФЩшМЦбЁгУвЛЦЌСшбєЕЅЦЌЛњSPCE061AКЭвЛЦЌFPGA cyclone EP1C6ЃЌЦфНсЙЙПђЭМШчЭМ3ЫљЪОЁЃ  ЭМ3 Лљгкcyclone EP1C6ЕФжїПиАхНсЙЙЭМ 2.1 cyclone EP1C6КЭSPCE061AМђНщ cyclone EP1C6ЪЧAlteraЭЦГіЕФвЛПюИпадМлБШFPGAЃЌЙЄзїЕчбЙ3.3VЃЌФкКЫЕчбЙ1.5VЁЃВЩгУ0.13ІЬmЙЄвеММЪѕЃЌШЋЭSRAMЙЄвеЃЌЦфУмЖШЮЊ5980ИіТпМЕЅдЊЃЌАќКЌ20Иі128ЁС36ЮЛЕФRAMПщЃЈM4KФЃПщЃЉЃЌзмЕФRAMПеМфДяЕН92160ЮЛЁЃФкЧЖ2ИіЫјЯрЛЗЕчТЗКЭвЛИігУгкСЌНгSDRAMЕФЬиЖЈЫЋЪ§ОнТЪНгПкЃЌЙЄзїЦЕТЪИпДя200MHzЁЃ SPCE061AЪЧСшбєПЦММЭЦГіЕФвЛПю16ЮЛЮЂПижЦЦїЃЌФкЧЖ32KзжFLASHКЭ2KзжSRAMЃЌВЂМЏГЩСЫICEЗТецЕчТЗНгПкЉpЭЈгУI/OЖЫПкЉpЖЈЪБЦї/МЦЪ§ЦїЉpжаЖЯПижЦЉpCPUЪБжгЉpФЃЪ§зЊЛЛЦїA/DЉpDACЪфГіЉpЭЈгУвьВНДЎааЪфШыЪфГіНгПкЁЂДЎааЪфШыЪфГіНгПкЉpЕЭЕчбЙМьВт/ЕЭЕчбЙИДЮЛЉpПДУХЙЗЕШЙІФмЁЃCPUзюИпПЩЙЄзїдк49MHzЕФжїЦЕЯТЃЌНЯИпЕФДІРэЫйЖШЪЙSPCE061AФмЙЛЗЧГЃШнвзЁЂПьЫйЕиДІРэИДдгЕФЪ§зжаХКХЁЃ 2.2 жїПиАхНсЙЙМАЙІФм жїПиАхНсЙЙШчЭМ3ЫљЪОЃЌЩЯЮЛЛњЗЂЫЭЕФЪ§ОнЭЈЙ§ЫЋНЪДЋЫЭЕНRS422НгЪеФЃПщ[2]ЃЌОзЊЛЛКѓЫЭжСЕЅЦЌЛњЃЌгЩЕЅЦЌЛњЕФIOB7ПквдUARTжаЖЯЕФЗНЪННгЪеЩЯЮЛЛњЗЂЫЭЕФЪ§ОнЁЃЕЅЦЌЛњНЋНгЪеЕФДЎПкЪ§ОнвдСНИізжНкЮЊЕЅЮЛж№вЛаДШыФкжУЕФFLASHжаЁЃЕЅЦЌЛњФкВПЕФ2KзжSRAMдкДЫзїЮЊвЛИіЛКДцЧјЃЌУПДЮЕЅЦЌЛњвЊЯђFPGAжааДвЛЦСаТЕФЪ§ОнЪБЃЌЯШАДЬиЖЈЕФЕижЗДгFLASHжаЖСГіЪ§ОнВЂДцЗХЕНSRAMжаЃЌдйНЋSRAMЕФЪ§ОнВЂаааДЕНFPGAЕФЫЋПкRAMжаЁЃ FPGAдкЦфФкВПХфжУвЛИіЫЋПкRAMЛКДцЕЅЦЌЛњаДШыЕФЪ§ОнЃЌЭЌЪБНЋетаЉЪ§ОнАДееДѓЦСЕФНсЙЙКЭЩЈУшЕчТЗЕФЬиЕуЃЌДгЫЋПкRAMжагабЁдёадЕиЖСГіЃЌВЂНЋЖСГіЕФЪ§ОнгЩВЂзЊДЎЃЌАДеевЛЖЈЕФЪБађЖдДѓЦСЕуеѓНјааЁЂСаЩЈУшЃЌетИіЪБађвВЪЧгЩFPGAВњЩњЕФЁЃЩЈУшЪ§ОнКЭЪБађПижЦаХКХДгFPGAЕФI/OПкЪфГіКѓЃЌОЙ§вЛИігЩ74LS245ЙЙГЩЕФИєРыЧ§ЖЏЕчТЗЫЭжСДѓЦСФЛЁЃ 2.3 ЛљгкFPGAЕФЫЋПкRAMЕФХфжУ ЛљгкFPGAЕФЫЋПкRAMЕФХфжУЪЧБОЩшМЦЕФЖРЬижЎДІЁЃRAMзїЮЊжаНщНЋЕЅЦЌЛњЫЭРДЕФЪ§ОндкLEDЕчзгЦСЩЯЯдЪОГіРДЃЌгЩгкЪ§ОнЯдЪОЪЧвЛжжЖЏЬЌЩЈУшЗНЪНЃЌШєВЩгУвЛИіRAM ЧјЃЌЕЅЦЌЛњдкаДRAM ЪБЃЌFPGAжЛФмДІгкЕШД§зДЬЌЃЌFPGAЖСRAMЪБЃЌЕЅЦЌЛњаДЪ§ОнвВЮоЗЈЭЌЪБНјааЃЌЕМжТЦСФЛЫЂаТЦЕТЪНЕЕЭЃЌЖЏЬЌЩЈУшВЛСЌајЃЌгАЯьЦСФЛЕФЯдЪОаЇЙћЁЃвђДЫЩшМЦСЫСНИіЭЌбљДѓаЁЕФRAM ЧјЃКAЧјКЭBЧјЁЃЕБЕЅЦЌЛњаДAЧјЪБЃЌ FPGAЖСBЧјЕФЪ§ОнЃЌЕЅЦЌЛњаДBЧјЪБЃЌFPGAЖСAЧјЕФЪ§ОнЁЃДЫЭтЃЌгЩгкFPGAЩЈУшФЃПщПЩвдДяЕНКмИпЕФЩЈУшЫйТЪЃЌЖјЕЅЦЌЛњЕФдЫааЫйТЪдђЯрЖдНЯЕЭЃЌЧвСНИіФЃПщМфгаДѓСПЕФЪ§ОнНЛЛЛЃЌЮЊДЫбЁдёИпЫйЫЋПкRAM,вЛЗНУцБЃжЄЕЅЦЌЛњКЭFPGAЭЌЪБЖСаДЪ§ОнЃЌСэвЛЗНУцБЃжЄСЫЪ§ОнЕФДІРэЫйЖШЁЃ cyclone EP1C6ЬсЙЉСЫ20ИіОпгавьВНЉpЫЋЖЫПкЉpДјМФДцЦїЪфШыПкЉpПЩбЁдёЕФДјМФДцЦїЪфГіПкЕФДцДЂФЃПщЁЊM4KФЃПщЃЌУПИіM4KФЃПщЕФДцДЂШнСПЮЊ4KbitЁЃдкQUARTUSШэМўжаНјааМђЕЅЕФЩшжУЃЌОЭПЩвдНЋM4KФЃПщХфжУГЩЫЋПкRAM,Ъ§ОнКЭЕижЗЕФЮЛПэПЩИљОнЪЕМЪашвЊНјаабЁдёЁЃБОЮФЩшМЦЕФRAMПЩШнФЩСНЦСЕФЪ§ОнЃЌЪ§ОнЮЛПэЮЊ16ЮЛЃЌЕижЗЮЊ12ЮЛЃЌЦфжаЕижЗЕФзюИпЮЛзїRAMЗжЧјгУЃЌУПИіЧјДцДЂвЛЦСЕФЪ§ОнЃЌСНЦСЖСаДЭЌЪБНјааЃЌЫЋПкRAMЕФХфжУШчЭМ4ЫљЪОЁЃ  ЭМ4 ЫЋПкRAMХфжУ ЦфжаwrenЪЧЕЅЦЌЛњЭљFPGAжааДШыЪ§ОнЕФаДЪЙФмаХКХЃЌwraddress[11..0]ЪЧаДЕФЕижЗаХКХЃЌ wrclockЪЧаДЪБжгЃЌdata[15..0]ЪЧаДЕФЪ§ОнЃЌrdaddress[11..0]ЪЧЖСЕФЕижЗаХКХЃЌrdclockЪЧЖСЪ§ОнЕФЪБжгаХКХЃЌq[15..0]ЪЧЖСГіЕФЪ§ОнЁЃ 2.4 ЛљгкFPGAЕФЖРСЂЩЈУшЕЅдЊ ЕуеѓФЃПщЪЧКьЩЋLEDЙВвѕФЃПщЃЌ4Пщ16ЁС16ЕуеѓФЃПщСЌНгГЩ64ЁС16ЕуеѓзїЮЊвЛИіЕЅдЊНјааПижЦЃЌећИіДѓЦСга3ЁС8ИіетбљЕФЕЅдЊЁЃНЋLEDЕФЙЋЙВНгПкзїЮЊааПижЦЃЌааЩЈУшаХКХЭЌЪБПижЦзХвЛаажаЖрИіLEDЕФЭЈЖЯЃЌвдУПИіLEDСїЙ§ЕФЕчСїЮЊ10mAМЦЫуЃЌвЛИіЕЅдЊга64Са,ааЩЈУшаХКХжСЩйЕУЬсЙЉ1AзѓгвЕФЕчСїЃЌвђДЫЃЌдкЩЈУшаХКХЫЭЕНLEDжЎЧАБиаыОЙ§вЛИіШ§МЋЙмвдЬсИпЧ§ЖЏФмСІЁЃШ§МЋЙмбЁгУИпЫйжаЙІТЪДяСжЖйЙмTIP127ЃЌЫќЕФМЏЕчМЋЮќЪеЕчСїзюДѓПЩДя5AЃЌБЃжЄааЧ§ЖЏФмСІЁЃгЩгкЕуеѓЕФУПааашвЊвЛИіШ§МЋЙмЧ§ЖЏЃЌЫљвдвЛИі64ЁС16ЕФЕЅдЊПщашвЊ16ИіTIP127ЁЃааЩЈУшЕчТЗВЩгУДјЫјДцЕФвЦЮЛМФДцЦї74LS595РДПижЦЃЌУПЦЌ74LS595ПижЦ 8ааЕуеѓЕФбЁЭЈгыЗёЁЃгЩгкВЩгУЕФЩЈУшЗНЪНЮЊУПИє8ааЪ§ОнЭЌЪБЩЈУшЃЌвЛЦЌ74LS595УПДЮжЛФмЕуССвЛааЕФЪ§ОнЃЌУПааЕуССЕФЪБМфЯрЕШМДеМПеБШЮЊ1/8ЃЌвђДЫЦСФЛССЖШЗЧГЃОљКтЁЃ СаЩЈУшЕчТЗЕФЙІФмЪЧАбвЊЯдЪОЕФааЖдгІЕФСаЪ§ОнЫЭЕНLEDЕФвѕМЋЃЌСаЩЈУшвВЪЧгЩ74LS595ПижЦЕФЁЃБОЮФЩшМЦЕФЦСФЛЕФгВМўНсЙЙЬиЕуЪЧЃКУП8ааLEDЕФвѕМЋЪЧСЌдквЛЦ№ЕФЃЌУПЦЌ74LS595ПижЦ8СаЪ§ОнЃЌУПИє8ааЭЌЪБЩЈУшЃЌЖдгквЛИі64ЁС16ЕФЕуеѓЕЅдЊЃЌЙВашвЊ8ЁС2Иі74LS595ПижЦЃЌУПааЩЯЕФ74LS595ЖМЪЧМЖСЊЦ№РДЕФЁЃУПЭъГЩвЛДЮСаЩЈУшЃЌFPGAЖМвЊЪфГівЛИіЫјДцаХКХИј74LS595вдЫјДцСаЪ§ОнЃЌНгзХЪфГіааЩЈУшаХКХЕуССЖдгІЕФааЃЌдйЖдааЩЈУшЪ§ОнНјааЫјДцЃЌШчДЫбЛЗЭљИДЪЕЯжећИіДѓЦСФЛЕФЖЏЬЌЪЕЪБЯдЪОЙІФмЁЃ гЩгкFPGAдкааСаЩЈУшжЎЧАвбОЖдЪ§ОнНјааВЂДЎзЊЛЛЃЌЪ§ОнЖМЪЧДЎааЪфГіЕФЃЌУПИє8ааЭЌЪБЩЈУшЃЌећИіЦСФЛааЩЈУшжЛашеМгУ1ИіI/OПкЃЌСаЩЈУшжЛашеМгУ16ИіI/OПкЃЌДгЖјДѓДѓМѕЩйСЫЖдI/OЕФеМгУЁЃВЩгУFPGAЩшМЦЩЈУшТпМЃЌЩЈУшЕФЙиМќВЛдкЪЧгВМўСЌНгЃЌЖјЪЧЖдаОЦЌзЪдДЕФХфжУЁЃ 3 ШэМўЩшМЦ ЯЕЭГЕФШэМўЩшМЦгЩШ§ВПЗжзщГЩЃКЩЯЮЛЛњЭМЯѓ/ЮФзжБрМгыЗЂЫЭШэМўЩшМЦЃЌЕЅЦЌЛњПижЦЕЅдЊШэМўЩшМЦЃЌFPGAПижЦЕЅдЊШэМўЩшМЦЁЃ 3.1 ЩЯЮЛЛњШэМўЩшМЦ ЩЯЮЛЛњЕФЭМЯѓ/ЮФзжБрМгыЗЂЫЭШэМўгЩVisual BasicБраДЃЌжЛаыдкНчУцжаНЋЦСФЛДѓаЁЩшжУЮЊ192ЁС128ЃЌДЎПкбЁдёCOM1ЛђCOM2ЃЌВЈЬиТЪЩшжУЮЊ9600ЃЌЩшжУУПЦСЦ№ЪМЕижЗКЭвЊЗЂЫЭЕФЦСЪ§ЃЌЕїШыАќКЌЯрЙиаХЯЂЕФЮФМўЃЌЕуЛїЁАЗЂЫЭЁБАДХЅМДПЩЁЃИУШэМўЪЪгУгкШЮКЮДѓаЁВЪЩЋ/ЕЅЩЋЦСЃЌЬсЙЉСЫЗсИЛЕФЭМаЮ/ЮФзжБрМЉpаоИФЙІФмЃЌвВПЩвджБНгЕїгУWINDOWSжаЕФ16ЩЋЛЭМЮФМўЃЈ*.bmpЃЉЁЃ 3.2 ЕЅЦЌЛњПижЦЕЅдЊШэМўЩшМЦ ЕЅЦЌЛњПижЦЕЅдЊЕФШэМўЩшМЦжївЊЪЕЯжШ§ДѓЙІФмЃКДЎааЪ§ОнНгЪеКЭДцДЂЁЂЪ§ОнЪфГіКЭЭМЯѓЯдЪОЗНЪНБфЛЛЁЃДЎааЪ§ОнНгЪеВПЗжжївЊЪЧЭЈЙ§UARTжаЖЯНгЪеВЂБЃДцЪ§ОнЁЃЭМЯѓЯдЪОЗНЪНБфЛЛВПЗжЪЕЯжЭМЯѓЕФБфЛЛШчЩЯвЦЁЂЯТвЦЁЂзѓвЦЁЂгввЦЕШвдЪЕЯжЗсИЛЖрВЪЕФЭМЯѓЯдЪОаЇЙћЁЃЕЅЦЌЛњШэМўЩшМЦЪЧдкСшбєПЦММЕФМЏГЩПЊЗЂЛЗОГunSP IDEЯТЭъГЩЕФЃЌжївЊгЩвЛИіCЮФМўКЭвЛИіASMЮФМўзщГЩЃЌCЮФМўАќРЈ5ЦСЪ§ОнЕФбЛЗЫЭЯдКЭЭМЯёЯдЪОЗНЪНБфЛЛЃЌЛуБрЮФМўАќРЈжаЖЯЗўЮёзгГЬађКЭЦфЫћКЏЪ§ЕїгУЕФзгГЬађЁЃ 3.3 FPGAПижЦЕЅдЊШэМўЩшМЦ FPGAПижЦЕЅдЊЕФЩшМЦЪЧдкQUARTUSIIЛЗОГЯТЭъГЩЃЌВЂгУгВМўУшЪігябдVHDLУшЪіЃЌжївЊЙІФмЪЧХфжУЫЋПкRAMЁЂЩшМЦЩЈУшПижЦЕчТЗЁЃИУЕЅдЊЕФШэМўЩшМЦФЃПщШчЭМ5ЫљЪОЁЃ  ЭМ5 FPGAПижЦЕЅдЊШэМўЩшМЦПђЭМ ЫЋЖЫПкRAMЕФХфжУЭъШЋЭЈЙ§дкQUARTUSЛЗОГжаЩшжУВЫЕЅЪЕЯжЃЌХфжУЭъГЩКѓНЋздЖЏЩњГЩвЛИіVHDLЮФМўЃЌУшЪіЫЋПкRAMЕФФкВПТпМЙІФмЃЌЫЋПкRAMдкећИіГЬађЩшМЦзїЮЊвЛИідЊМўЕїгУЁЃ ЛљгкFPGAЕФЩЈУшФЃПщЕФШэМўЩшМЦШчЯТЃКЪзЯШЖдFPGAзмЪБжгclkНјаа64ЗжЦЕЕУЕНclk1ЃЌclk1ЕФЕЭЕчЦНЦфМфFPGAЖСШЁЫЋПкRAMЕФЪ§ОнЃЌУП4ИіclkжмЦкЖСвЛИі16ЮЛЕФЪ§ОнЃЌЙВЖСГі16ИіЪ§ЁЃclk1ЕФИпЕчЦНЦкМфFPGAНјааСаЩЈУшЃЌУП2ИіclkжмЦкЭЌЪБЪфГі16ИіЪ§ЕФ1ЮЛЃЌЙВ32ИіжмЦкНЋет16ИіЪ§гЩВЂзЊДЎЪфГіЕН16ИљЪ§ОнЯпЩЯЃЌгЩгкЕЅЦЌЛњаДRAMЕФЫйЖШЕЭгкFPGAЖдЪ§ОнЕФДІРэЫйЖШЃЌЪЃЯТЕФ32ИіclkжмЦкгУгкЕШД§ЕЅЦЌЛњЭъГЩвЛИіЧјЕФаДВйзїЁЃ12Иіclk1жмЦкКѓЃЌвЛааЕФЪ§ОнШЋВПЩЈУшЭъБЯЃЌFPGAЪфГівЛИіСаЫјДцаХКХИј74LS595ЫјДцетаЉЪ§ОнЃЌЭЌЪБЪфГіааЩЈУшаХКХКЭааЫјДцаХКХЃЌНгзХЩЈУшЕкЖўааЃЌгЩгкВЩгУ16ИљЪ§ОнЯпНјааИє8ааЩЈУшЃЌећИіLEDЕчзгЦС128аажЛвЊЭъГЩ8ДЮааЩЈУшМДПЩЃЌЪБађШчЭМ6ЫљЪОЁЃ  ЭМ6 ЩЈУшЪБађЭМ |

ЭјгбЦРТл