ЩЯРЕчзшШЁжЕЮЪЬтЕФЬНЬж

ЗЂВМЪБМфЃК2016-1-27 08:10

ЗЂВМепЃКdesignapp

ЙиМќДЪЃК

ЩЯРЕчзш

|

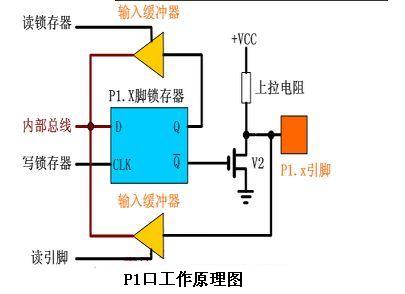

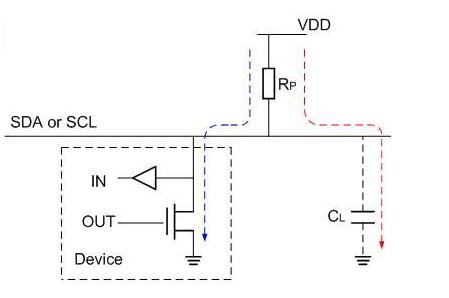

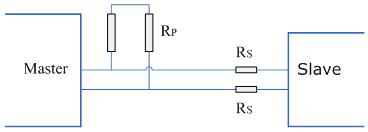

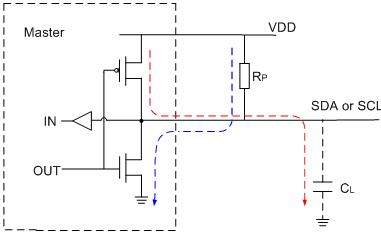

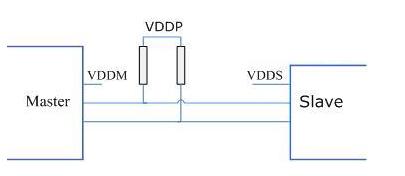

ЁЁЁЁТЉМЋПЊТЗЩЯРЕчзшШЁжЕЮЊКЮВЛФмКмДѓЛђКмаЁ? ЁЁЁЁ  ЁЁЁЁШчЙћЩЯРЕчзшжЕЙ§аЁЃЌVccЙрШыЖЫПкЕФЕчСї(Ic)НЋНЯДѓЃЌетбљЛсЕМжТMOSЙмV2(Ш§МЋЙм)ВЛЭъШЋЕМЭЈ(Ib*ІТ ЁЁЁЁЃЌгаБЅКЭзДЬЌБфГЩЗХДѓзДЬЌЃЌетбљЖЫПкЪфГіЕФЕЭЕчЦНжЕдіДѓ(i2cавщЙцЖЈЃЌЖЫПкЪфГіЕЭЕчЦНЕФзюИпдЪаэжЕЮЊ0.4v)ЁЃ ЁЁЁЁШчЙћЩЯРЕчзшЙ§ДѓЃЌМгЩЯЯпЩЯЕФзмЯпЕчШнЃЌгЩгкRCгАЯьЃЌЛсДјРДЩЯЩ§ЪБМфЕФдіДѓ(ЯТНЕбгЪЧаОЦЌФкЕФОЇЬхЙмЃЌЪЧгадДЧ§ЖЏЃЌЫйЖШНЯПь;ЩЯЩ§бгЪЧЮодДЕФЭтНгЕчзшЃЌЫйЖШТ§)ЃЌЖјЧвЩЯРЕчзшЙ§ДѓЃЌМДв§Ц№ЪфГізшПЙЕФдіДѓЃЌЕБЪфГізшПЙКЭИКдиЕФзшПЙПЩвдБШФтЕФЪБЃЌдђЪфГіЕФИпЕчЦНЛсЗжбЙЖјМѕЩйЁЃ ЁЁЁЁI2CЕФЩЯРЕчзшПЩвдЪЧ1.5KЃЌ2.2KЃЌ4.7KЃЌ ЕчзшЕФДѓаЁЖдЪБађгавЛЖЈгАЯьЃЌЖдаХКХЕФЩЯЩ§ЪБМфКЭЯТНЕЪБМфвВгагАЯьЃЌвЛАуНг1.5KЛђ2.2KЁЃ ЁЁЁЁ(ЪЕбщЃКНгШы200KЩЯРЕчзшЃЌНсЙћЙлВьЕНаХКХЩЯЩ§ЪБМфдіДѓЃЌЗНВЈБфГЩШ§НЧВЈ) ЁЁЁЁI2CЩЯРЕчзшШЗЖЈгавЛИіМЦЫуЙЋЪНЃК ЁЁЁЁRmin={Vdd(min)-o.4V}/3mA ЁЁЁЁRmax=(T/0.874) *c, T=1us 100KHz, T=0.3us 400KHz ЁЁЁЁCЪЧBus capacitanceRpзюДѓжЕгЩзмЯпзюДѓШнЯо(Cbmax)ОіЖЈ,RpзюаЁжЕгЩVioгыЩЯРЧ§ЖЏЕчСї(зюДѓШЁ3mA)ОіЖЈ;гкЪЧ Rpmin=5V/3mAЁж1.7K(@Vio=5V)Лђеп2.8V/3mAЁж1K(@Vio=2.8V)ЁЃ ЁЁЁЁRpmaxЕФШЁжЕЃК100KbpsзмЯпЕФИКдизюДѓШнЯо  ЁЁЁЁRPВЛвЫЙ§аЁЃЌвЛАуВЛЕЭгк1KІИ ЁЁЁЁвЛАуIO ЖЫПкЕФЧ§ЖЏФмСІдк2mAЁЋ4mAСПМЖЁЃШчЙћRPзшжЕЙ§аЁЃЌVDDЙрШыЖЫПкЕФЕчСїНЋНЯДѓЃЌетбљЛсЕМжТMOSЙмВЛЭъШЋЕМЭЈЃЌгаБЅКЭзДЬЌБфГЩЗХДѓзДЬЌЃЌетбљЖЫПкЪфГіЕФЕЭЕчЦНжЕдіДѓ(I2CавщЙцЖЈЃЌЖЫПкЪфГіЕЭЕчЦНЕФзюИпдЪаэжЕЮЊ0.4V);ШчЙћЙрШыЖЫПкЕФЕчСїЙ§ДѓЃЌЛЙПЩФмЫ№ЛЕЖЫПкЁЃЙЪЭЈГЃЩЯРЕчзшгІбЁШЁВЛЕЭгк1KІИЕФЕчзш(ЕБVDD=3VЪБЃЌЙрШыЕчСїВЛГЌЙ§3mA)ЁЃ ЁЁЁЁRPВЛвЫЙ§ДѓЃЌвЛАуВЛИпгк10KІИ ЁЁЁЁгЩгкЖЫПкЪфГіИпЕчЦНЪЧЭЈЙ§RPЪЕЯжЕФЃЌЯпЩЯЕчЦНДгЕЭЕНИпБфЛЏЪБЃЌЕчдДЭЈЙ§RPЖдЯпЩЯИКдиЕчШнCLГфЕчЃЌеташвЊвЛЖЈЕФЪБМфЃЌМДЩЯЩ§ЪБМфЁЃЖЫПкаХКХЕФЩЯЩ§ЪБМфПЩНќЫЦгУГфЕчЪБМфГЃЪ§RPCLГЫЛ§БэЪОЁЃ ЁЁЁЁаХКХЯпИКдиЕчШн(ЖдЕи)гЩЖрЗНУцзщГЩЃЌАќРЈЦїМўв§НХЁЂPCBаХКХЯпЁЂСЌНгЦїЕШЁЃШчЙћаХКХЯпЩЯЙвгаЖрИіЦїМўЃЌИКдиЕчШнвВЛсдіДѓЁЃБШШчзмЯпЙцЖЈЃЌЖдгкЕФ400kbpsЫйТЪгІгУЃЌаХКХЩЯЩ§ЪБМфгІаЁгк300ns;МйЩшЯпЩЯCLЮЊ20PFЃЌПЩМЦЫуГіЖдгІЕФRPжЕЮЊ15KІИЁЃ ЁЁЁЁШчЙћRCГфЕчЪБМфГЃЪ§Й§ДѓЃЌНЋЪЙЕУаХКХЩЯЩ§биБфЛЏЛКТ§ЃЌДяВЛЕНЪ§ОнДЋЪфЕФвЊЧѓЁЃвђДЫвЛАугІгУжабЁШЁЕФЖМЪЧМИKІИСПМЖЕФЩЯРЕчзшЃЌБШШчЖМбЁШЁ4K7ЕФЕчзшЁЃаЁзшжЕЕФRPЕчзшдіДѓСЫЖЫПкSinkЕчСїЃЌЙЪдкПЩФмЕФЧщПіЯТЃЌRPШЁжЕгІЩдДѓвЛЕуЃЌвдМѕЩйКФЕчЁЃСэЭтЃЌЭЈВњЧщПіЯТЃЌSDA,SCLСНЬѕЯпЩЯЕФЩЯРЕчзшШЁжЕЪЧвЛжТЕФЃЌВЂЩЯРЕНЭЌвЛЕчдДЩЯЁЃ ЁЁЁЁPCBВМОжВМЯпгыПЙИЩШХЩшМЦ ЁЁЁЁI2CаХКХЯпЪєгкЕЭЫйПижЦЯпЃЌдкЪжЛњPCBЩшМЦЪБЃЌАДЭЈГЃЕФПижЦIOЖдД§МДПЩЃЌЮоашзіЬиБ№ЕФБЃЛЄЩшМЦЃЌвЛАуВЛгУЕЃаФЪмЕНдыЩљдДИЩШХЁЃ ЁЁЁЁЕЋдквЛаЉЬиЖЈЕФЧщПіЯТЃЌБШШчелЕўЁЂЛЌИЧЛњаЭжаЃЌI2CЕФСНИљаХКХЯпашвЊЭЈЙ§зЊжсЛђЛЌЙьДІЕФFPCЃЌДЫЪБгЩгкаХКХТЗОЖБШНЯГЄЃЌОрРыЬьЯпБШНЯНќЃЌЖјЧвOpendrainЕФЪфГіМЖЖдЕизшПЙДѓЃЌЖдИЩШХБШНЯУєИаЃЌвђДЫБШНЯШнвзЪмЕНRFаХКХдДЕФИЩШХЁЃдкетжжЧщПіЯТЃЌОЭгІЪЪЕБзЂвтЖдI2CаХКХЯпЕФБЃЛЄЁЃБШШчI2CСНЬѕаХКХЯп(SDA,SCL)ЕШГЄЖШЕиЦНаазпЯпЃЌСНБпМгЕиЯпНјааБЃЛЄЃЌБмУтСйНќВуГіЯжИпЫйаХКХЯпЕШЁЃ ЁЁЁЁЩЯРЕчзшгІАВжУдкODЪфГіЖЫИННќЁЃЕБI2CзмЯпЩЯжїДгЦїМў(Master & ЁЁЁЁSlave)СНЖЫОљЮЊODЪфГіЪБЃЌЕчзшЗХжУдкаХКХТЗОЖЕФжаМфЮЛжУЁЃЕБжїЩшБИЖЫЪЧШэМўФЃФтЪБађЃЌЖјДгЩшБИЪЧODЪфГіЪБЃЌгІНЋЕчзшАВжУдкППНќДгЩшБИЕФЮЛжУЁЃ ЁЁЁЁI2CавщЛЙЖЈвхСЫДЎСЊдкSDAЁЂSCLЯпЩЯЕчзшRsЁЃИУЕчзшЕФзїгУЪЧЃЌгааЇвжжЦзмЯпЩЯЕФИЩШХТіГхНјШыДгЩшБИЃЌЬсИпПЩППадЁЃетИіЕчзшЕФбЁдёвЛАудк100ЁЋ200ohmзѓгвЁЃЕБШЛ,етИіЕчзшВЂВЛЪЧБиаыЕФЃЌдкЖёСгдыЩљЛЗОГжаЃЌПЩвдбЁгУЁЃ ЁЁЁЁ  ЁЁЁЁБШШчГЃгУЕФFM ЁЁЁЁНгЪеФЃПщЛђепCapsenseДЅУўИагІЙІФмПщЃЌЖМЪЧЭЈЙ§I2CНгПкПижЦЕФЁЃI2CНгПкаХКХДгДІРэЦїГіЗЂЃЌОЙ§PCBЩЯЕФаХКХТЗОЖЃЌНјШыЩЯЪіЕчТЗЕЅдЊЁЃI2CаХКХЯпЩЯдигавЛЖЈИЩШХЃЌетжжИЩШХЫфШЛЗљЖШВЂВЛКмДѓЃЌЕЋЛЙЪЧЛсгАЯьУєИаЕФFMНгЪеФЃПщЛђCapsenseДЅУўИагІЙІФмПщЁЃДЫЪБЃЌПЩвдЭЈЙ§дкППНќFMФЃПщЛђДЅУўИагІФЃПщЕФI2CаХКХЯпЩЯДЎНгRsЕчзшЃЌМДПЩгааЇНЕЕЭИЩШХЕФгАЯьЁЃДЫЭтЃЌЩЯРЕчзшЖЫЕФЕчдДвВвЊНјааЭЫёюДІРэЁЃ ЁЁЁЁШэМўФЃФтI2CЪБађ ЁЁЁЁгЩгквЛАуЕФI2CгІгУЫйТЪВЂВЛИп(400kbps)ЃЌЪЙгУДІРэЦїЕФIOПкФЃФтI2CВЈаЮ,ЭъШЋПЩвдЪЄШЮ(ДІРэЦївЛАуЕЃШЮMasterЃЌеМгаI2CЭЈаХЕФПижЦШЈЃЌЮоашЕЃаФЫцЛњЕФI2CЭЈаХЗўЮёжаЖЯЦфЫћШЮЮёЕФжДаа)ЁЃ ЁЁЁЁДІРэЦїЗжХфИјI2CШЮЮёЕФIOПкЃЌвЊЧѓПЩвдЪфГіИпЕЭЕчЦНЃЌЛЙФмХфжУЮЊЪфШыЖЫПкЁЃДІРэЦїИљОнзмЯпЙцЗЖвдМАДгЩшБИЕФЪБађвЊЧѓЃЌРћгУ2ЬѕIOаХКХЯпЃЌФЃФтI2CНгПкЪБађВЈаЮЃЌНјааI2CЭЈаХЁЃ ЁЁЁЁДІРэЦїЗЂЫЭЪ§ОнЪБЃЌЭЈЙ§IOПкЪфГіИпЕчЦНЃЌЩЯЩ§ЪБМфЛљБОгыЭтВПЩЯРДЕчзшзшжЕЮоЙиЃЌЧвБШгУЭтВПЩЯРЕчзшЩЯРЕНИпЕчЦНПьКмЖрЁЃДІРэЦїдкНгЪмЪ§ОнЪБЃЌМДБуЩЯРЕчзшзшжЕбЁЕФДѓвЛаЉЃЌДгЩшБИЪфГіЪ§ОнЕФВЈаЮЩЯЩ§биЛКТ§ЃЌЕЋгЩгкДІРэЦїЪЙгУШэМўВЩбљЕФЖјЗЧгВМўВЩбљЃЌвђДЫЃЌЖдЪ§ОнДЋЪфЕФНсЙћВЂВЛгАЯьЁЃвВОЭЪЧЫЕЃЌЪЙгУIOПкФЃФтI2CЪБађЪБЃЌЩЯРЕчзшзшжЕПЩвдЪЪЕБбЁЕФДѓвЛаЉЁЃ ЁЁЁЁашвЊжИГіЕФЪЧЃЌЪЙгУШэМўФЃФтзюЖржЛФмЭъГЩЕЅMasterЕФгІгУЃЌЖдгкЖрMasterгІгУЃЌгЩгкашвЊНјаазмЯпПижЦШЈЕФжйВУЙмРэЃЌЪЙгУШэМўФЃФтЕФЗНЗЈКмФбЭъГЩЁЃ ЁЁЁЁI2CзмЯпПеЯаЕФЪБКђЃЌСНЬѕаХКХЯпгІИУЮЌГжИпЕчЦНЁЃЗёдђЃЌЩЯРЕчзшЩЯЛсгаКФЕчЁЃЬиБ№ЪЧдкЩЯЕчЙ§ГЬжаЃЌIOЯпЩЯЕчЦНвВгІБЃГждкИпЕчЦНзДЬЌЁЃвВОЭЪЧЫЕЃКЕБMasterЕФI2CЪЙгУЕФЪЧIOШэМўФЃФтЪБЃЌвЛЖЈвЊБЃжЄИУСНИіIOЩЯЕчФЌШЯОљЮЊЪфШы(ЛђИпзш)ЛђепЪфГіИпЕчЦНЃЌЧаВЛПЩФЌШЯЮЊЪфГіЕЭЕчЦНЁЃIOФЌШЯЮЊЪфШыЪБЃЌПЩвдЭЈЙ§ЭтВПЩЯРЕчзшНЋI2CаХКХЯпРжСИпЕчЦНЁЃ ЁЁЁЁ  ЁЁЁЁI2CгІгУжаЩЯРЕчзшЕчдДЮЪЬт ЁЁЁЁдкВПжаЗжгІгУжаЃЌЛЙДцдкжїДгЩшБИвдМАЩЯРЕчзшЕчдДВЛвЛжТЕФЧщПіЃЌБШШчCameraФЃзщЁЃдкКмЖрЩшМЦЗНАИжаЃЌCameraФЃзщВЛЙЄзїЪБЃЌВЂВЛЪЧНјШыPowerDownФЃЪНЃЌЖјЪЧжБНгЙиБеФЃзщЙЉЕчVDDSЁЃДЫЪБЃЌДІРэЦїгыФЃзщЯрЛЅСЌНгЕФЫљгааХКХЯпЖМгІИУНјШыИпзшЬЌЃЌЗёдђОЭЛсгаЕчСїТЉШыФЃзщ;ЖјЖдгкДЫЪБЕФI2CПижЦаХКХЯпРДЫЕЃЌгЩгкЩЯРЕчзшЕФДцдкЃЌБиаыЙиЖЯЩЯРЕчзшЕчдДVDDPЁЃШчЙћЩЯРЕчзшЪЙгУЕФЪЧЯЕЭГЕчдДVDDM(VDDP=VDDM)ЃЌЮоЗЈЙиБеЃЌОЭЛсгаТЉЕчСїНјШыФЃзщ;вђДЫетжжЧщПіЯТЃЌгІИУЪЙгУVDDSзїЮЊЩЯРЕчзшЕчдД(VDDP=VDDS)ЃЌетбљЩЯРЕчзшЕчдДгыSlaveЕчдДМДПЩЭЌЪБЙиБе,ЧаЖЯСЫТЉЕчТЗОЖЁЃ ЁЁЁЁСэЭташвЊзЂвтЕФЪЧЃЌдкЩЯЪігІгУЪЕР§жабЁдёЕФIOЃЌгІИУбЁШЁЩЯЕчФЌШЯЮЊЪфШы(ЛђИпзш)ВХааЁЃ ЁЁЁЁ  |

ЭјгбЦРТл