аЁУЗИчКЭФувЛЦ№ЩюШыбЇЯАFPGAжЎДЎПкЕїЪдЃЈвЛЃЉ(ЩЯ)

ЗЂВМЪБМфЃК2016-1-26 11:52

ЗЂВМепЃКdesignapp

|

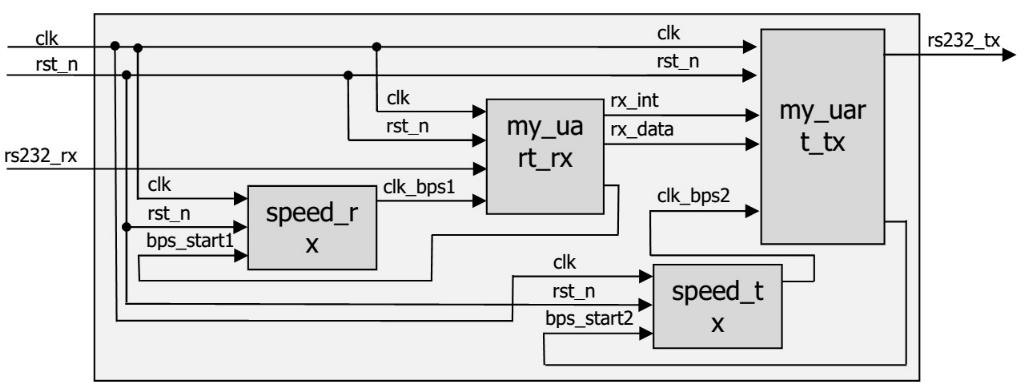

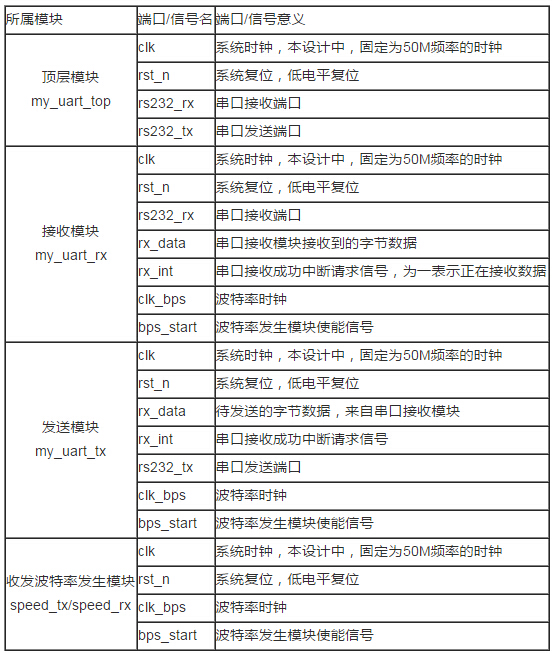

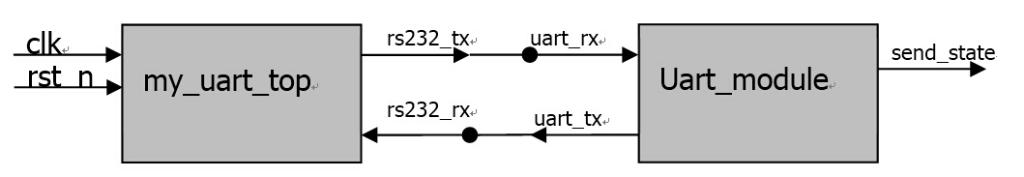

ДѓМвКУЃЌетМИЬьдкИїИіТлЬГЩЯЃЌОГЃОЭгаШЫдкЯђЮвзЩбЏЛљгкFPGAЕФДЎПкЭЈаХДњТыЃЌДѓВПЗжЖМЪЧдкЭјЩЯЯТдивЛИіЯжГЩЕФДњТыЃЌЕЋЪЧдкЪЙгУжаОЭгіЕНСЫИїжжЮЪЬтЃЌгкЪЧОЭЗЂЕНСЫТлЬГЩЯРДЧѓжњЁЃдкдФЖССЫЫћУЧЕФДњТыжЎКѓЃЌЮвЗЂЯжМИКѕГіздЭЌвЛИіАцБО(ФПЧАШЗЖЈЮЊЬиШЈЭЌбЇЕФЛљгкEPM240ШыУХЪЕбщЕФДњТы)ЁЃЫћУЧдкЕїЪдетИіДњТыЕФЪБКђЃЌОГЃДцдкетбљМИИіЮЪЬтЃК1ЁЂВПЗжШЫЖдИУДЎПкЭЈбЖФЃПщЭъШЋВЛРэНтЃЌЖдУПОфЛАЃЌЩѕжСУПИіФЃПщЕФЙІФмЖМВЛРэНт;2ЁЂВПЗжШЫВЩгУзюдЪМЕФЛВЈаЮЕФЗНЪНРДЖдИУФЃПщНјааЗТецЃЌНсЙћЮоЗЈЕУЕНЗТецНсЙћ;3ЁЂВПЗжШЫВЛЛсЪЙгУmodelsimЖдИУЩшМЦНјааЗТец;4ЁЂОјДѓВПЗжШЫВЛЛсБраДtestbench;5ЁЂЯТАхВтЪдЮоЗЈНјаае§ШЗЕФзжЗћДЎЪеЗЂЁЃдкЙЋЫОФкВПЃЌЮвНЋетжжЯжЯѓКЭМИЮЛРЯЪІНЛСїжЎКѓЃЌЯФгюЮХРЯЪІНЈвщЮвзЈУХеыЖдИУДњТыаДвЛИігЩдРэЕНДњТыЃЌгЩЗТецЕНАхМЖЕФЕїЪдБЪМЧЁЃељШЁгУзюЭЈЫзЃЌвВЪЧзюБПЕФАьЗЈЃЌЪжАбЪжЕФНЬЛсДѓМвРДЕїЪдетИіДњТыЁЃ БОЕїЪдБЪМЧжївЊгЩЮхИіВПЗжзщГЩЃКдЪМДњТыЗжЮі;дЪМДњТыбщжЄ;ЖддЪМДњТыНјаааоИФ;ЖдаоИФКѓЕФДњТыНјаабщжЄ;ЖдаоИФКѓЕФЩшМЦНјааАхМЖбщжЄЁЃУПИіВПЗжЃЌаЁУЗИчЖМЛсгУЭМЮФНсКЯЕФЗНЪНЃЌНЬДѓМввЛВНвЛВНЕФРДНјааЁЃ дЪМДњТыЗжЮі ИУДњТыРДздаЁУЗИчзюГчАнЕФДѓЩёЃЌЬиШЈЭЌбЇЁЃЕБЪБаЁУЗИчвВЪЧПДзХЬиШЈЭЌбЇЕФЪщКЭЪгЦЕНЬГЬвЛВНвЛВНзпЙ§РДЕФЁЃЬиШЈЭЌбЇЕФДњТыЪЕЯжСЫЕЅзжНкЕФЪеЗЂВтЪдЃЌУЛгаЖдСЌајзжНкЕФЪеЗЂНјааВтЪдЁЃЬиШЈЭЌбЇЕБЪБвВЫЕЙ§ЃЌетИіжЛЪЧвЛИіМђЕЅЕФЪЕбщЃЌРыЪЕМЪЙЄвЕгІгУЛЙгавЛЖЈЕФОрРыЁЃПМТЧЕНТлЬГЩЯКмЖраЁЛяАщЖМЯЃЭћФмЙЛЪЕЯжСЌајзжНкЕФЪеЗЂЙІФмЃЌвђДЫаЁУЗИчОЭдкЬиШЈЭЌбЇЕФДњТыЩЯНјааСЫаоИФЁЃаоИФКѓЕФДњТыЃЌЪфШыЪБжгПЩвддквЛЖЈЗЖЮЇФкбЁдёШЮвтЦЕТЪЃЌФПЧАвбОжЇГж5жжВЈЬиТЪбЁдё(9600ЁЂ19200ЁЂ38400ЁЂ57600ЁЂ115200)ЃЌЪЕМЪаЁУЗИчЛЙзіЙ§ИќИпВЈЬиТЪЕФВтЪдЃЌФПЧАЪЕВтдк115200ВЈЬиТЪЕФЫйТЪЯТПЩвдЪЕЯжГЌЙ§9999999ДЮСЌајЮоМфЖЯЕФЪеЗЂЁЃетРяЃЌаЁУЗИчЪзЯШНЋЬиШЈЭЌбЇЩшМЦМмЙЙдкетРяСаГіРДЃЌвдИјЖСепвЛИіжБЙлЕФгЁЯѓЁЃ  гЩЩЯЭМПЩжЊЃЌЬиШЈЭЌбЇЕФUARTДЎПкЩшМЦжївЊАќКЌСЫЫФИіФЃПщЃКДЎПкЗЂЫЭФЃПщ(my_uart_tx)ЁЂДЎПкНгЪеФЃПщ(my_uart_rx)ЁЂДЎПкНгЪеВЈЬиТЪЗЂЩњЦї(speed_rx)КЭДЎПкЗЂЫЭВЈЬиТЪЗЂЩњЦї(speed_tx)ЃЌЦфжаЃЌДЎПкЗЂЫЭВЈЬиТЪЗЂЩњЦїжївЊгУРДВњЩњДЎПкЗЂЫЭФЃПщЗЂЫЭЪ§ОнЪБЫљашЕФВЈЬиТЪЪБжгЃЌДЎПкНгЪеВЈЬиТЪЗЂЩњЦїжївЊгУРДВњЩњДЎПкНгЪеФЃПщНгЪеЪ§ОнЪБЕФВЈЬиТЪЪБжгЃЌДЎПкЗЂЫЭФЃПщжївЊИКд№дкжИЖЈВЈЬиТЪЕФЫйТЪЯТНЋД§ЗЂЫЭзжНкЗЂЫЭГіШЅЃЌДЎПкНгЪеФЃПщдђжївЊИКд№НгЪеРДздЦфЫћЩшБИЗЂЫЭЙ§РДЕФДЎПкЪ§ОнЁЃ my_uart_topФЃПщМДДЎПкЪеЗЂЖЅВуФЃПщЪЕЯжСЫИїИіФЃПщМфЕФаХКХСЌНгЙІФмЃЌЭЈЙ§ИУЖЅВуФЃПщЕФСЌНгЃЌЪЕЯжСЫНЋДЎПкНгЪеЕНЕФЪ§ОндйЗЂЫЭГіШЅЕФЙІФмЃЌМДЮвУЧВтЪдДЎПкЭЈаХзюГЃгУЕФвЛжжЗНЪНЁЊЁЊЛиЛЗВтЪдЁЃЬиШЈЭЌбЇИУЪЕбщЕФИїИіЖЫПкКЭФкВПаХКХЕФвтвхШчБэ1ЫљЪОЃК  ИУЪЕбщЕФФкШнЮЊЃЌДЎПкНгЪеФЃПщдкМьВтЕНЗЂЫЭЩшБИЗЂЫЭЙ§РДЕФЪ§ОнЦ№ЪМЮЛЪБЃЌНгЪежаЖЯаХКХжУ1ЃЌИУаХКХдђзїЮЊЦєЖЏДЎПкНгЪеВЈЬиТЪЗЂЫЭЦїЕФПижЦаХКХЃЌШЛКѓдкУПИіВЈЬиТЪЪБжгЩЯЩ§биЕНРДЪБЖСШЁДЎПкНгЪеЖЫПк(rs232_rx)ЩЯЕФЪ§ОнЁЃвЛжЁ(зжНк)Ъ§ОнНгЪеЭъГЩКѓЃЌНгЪежаЖЯаХКХРЕЭЃЌЭЃжЙВЈЬиТЪЗЂЩњЦїЙЄзїЃЌНгЪеЭъГЩЃЌЯЕЭГНјШыЕШД§зДЬЌЃЌЕШД§ЯТвЛДЮЕФЪ§ОнЕНРДЁЃ ЭЌЪБЃЌНгЪежаЖЯаХКХЕФЯТНЕбивВзїЮЊДЎПкЗЂЫЭФЃПщЕФЗЂЫЭЪЙФмаХКХЃЌвђЮЊвЛЕЉНгЪежаЖЯаХКХЕФЯТНЕбиГіЯжЃЌОЭБэУїНгЪеФЃПщЭъГЩСЫвЛДЮЪ§ОнЕФНгЪеЃЌДЫЪБЃЌОЭПЊЪМЪЙФмДЎПкЗЂЫЭВЈЬиТЪЗЂЩњЦїЃЌДЎПкЗЂЫЭФЃПщдђдкВЈЬиТЪЪБжгЕФЩЯЩ§биЕНРДЪБвРДЮНЋНгЪеФЃПщНгЪеЕНЕФЪ§ОнЕФУПвЛЮЛ(ЗЂЫЭФЃПщздЖЏЬэМгЦ№ЪМЮЛКЭЭЃжЙЮЛ)вРДЮЗЂЫЭГіШЅЃЌЕБЪ§ОнЗЂЫЭЭъГЩжЎКѓЃЌЭЃжЙДЎПкЗЂЫЭВЈЬиТЪЗЂЩњЦїЕФЪЙФмЃЌФЃПщНјШыЕШД§зДЬЌЃЌЕШД§ЯТвЛДЮНгЪежаЖЯаХКХЯТНЕбиЕФЕНРДЁЃ етРяЃЌЮвУЧЪзЯШЖдИУЩшМЦЕФВЈЬиТЪЗЂЩњЦїФЃПщНјааЗжЮіЁЃИУФЃПщЯрЖдМђЕЅЃЌДњТыШчЯТЫљЪОЃК вдЯТЪЧДњТыЦЌЖЮЃК 1 module speed_select ( 2 clk, rst_n , 3 bps_start , clk_bps 4 ); 5 6 input clk; // 50MHz 7 input rst_n ; // 8 input bps_start ; // 9 output clk_bps ; // clk_bps 10 11 /* 12 parameter bps9600 = 5207, // 9600bps 13 bps19200 = 2603, // 19200bps 14 bps38400 = 1301, // 38400bps 15 bps57600 = 867, // 57600bps 16 bps115200 = 433; // 115200bps 17 18 parameter bps9600_2 = 2603, 19 bps19200_2 = 1301, 20 bps38400_2 = 650, 21 bps57600_2 = 433, 22 bps115200_2 = 216; 23 */ 24 25 // 26 `define BPS_PARA 5207 // 9600 27 `define BPS_PARA_2 2603 // 9600 28 29 reg[ 12 : 0] cnt ; // 30 reg clk_bps_r ; // 31 32 //--------------------------------------------------------- 33 reg[ 2 : 0] uart_ctrl ; // uart 34 //--------------------------------------------------------- 35 36 always @ ( posedge clk or negedge rst_n ) 37 if(! rst_n ) cnt 38 else if(( cnt == `BPS_PARA ) || ! bps_start ) cnt 39 else cnt 40 41 always @ ( posedge clk or negedge rst_n ) 42 if(! rst_n ) clk_bps_r 43 else if( cnt == `BPS_PARA_2 ) clk_bps_r //clk_bps_r , 44 else clk_bps_r 45 46 assign clk_bps = clk_bps_r ; 47 48 endmodule ИУДњТыЕФ12-22аагУзЂЪЭЕФЗНЪНИцЫпСЫЮвУЧЃЌЛёЕУВЛЭЌВЈЬиТЪЪБВЈЬиТЪЗжЦЕМЦЪ§ЦїЕФжЕгІИУЮЊЖрЩйЃЌвдМАВЈЬиТЪМЦЪ§ЦїМЦЪ§ЕНвЛАыЪБЕФжЕЮЊЖрЩй(ИУжЕзїЮЊЖдаХКХЕФВЩбљЕуЃЌвђЮЊвЛАуЧщПіЯТЃЌвЛЮЛЪ§ОнЃЌдкИУЮЛЪ§ОнБЃГжЪБМфЕФжаМфЪБПЬЪЧзюЮШЖЈЕФ)ЁЃ26ааКЭ27ааЖЈвхЕФСНИіВЮЪ§BPS_PARAКЭBPS_PARA_2ЗжБ№ОЭЪЧВЈЬиТЪЗжЦЕМЦЪ§ЦїЕФзюДѓжЕКЭжаМфжЕЁЃЪЕМЪЪЙгУЪБЃЌжЛашвЊИљОнФуЫљашвЊЕФВЈЬиТЪЃЌИќИФетСНИіВЮЪ§ЕФжЕМДПЩ ЁЃР§ШчЃЌбЁдёВЈЬиТЪЮЊ9600bpsЪБЃЌЩшЖЈBPS_PARA=5207ЃЌBPS_PARA_2=2603ЁЃЙигкетИіжЕЕФМЦЫуЃЌетРяднЪБВЛЬсЃЌКѓЮФЛсгаНЛДњЁЃ 36аажС39ааЮЊВЈЬиТЪЗжЦЕМЦЪ§ЦїЕФМЦЪ§НјГЬЃЌМДВЈЬиТЪЗЂЩњФЃПщУЛгаБЛЪЙФм(! bps_start)ЛђепМЦЪ§ЦїМЦЪ§ЕНBPS_PARAКѓдђНЋМЦЪ§ЦїЧхСуЃЌЦфЫќЧщПіЯТдђУПРДвЛИіЪБжгЩЯЩ§биМЦЪ§ЦїздМг1ЁЃЭЈЙ§ДЫНјГЬЃЌдђПЩЕУЕНЯрЖдОЋзМЕФВЈЬиТЪЖЈЪБЁЃ 41аажС44ааЮЊЪ§ОнВЩбљЪБПЬЕФЩњГЩЃЌЩЯУцЬсЕНЙ§ЁАвЛАуЧщПіЯТЃЌвЛЮЛЪ§ОнЃЌдкИУЮЛЪ§ОнБЃГжЪБМфЕФжаМфЪБПЬЪЧзюЮШЖЈЕФЁБЃЌвђДЫетРяЮвУЧдкМЦЪ§ЦїМЦЪ§ЕНвЛАыЪБЃЌВњЩњвЛИіЪБжгжмЦкЕФИпТіГхЃЌДЫТіГхзїЮЊВЩбљЪ§ОнЕФЪЙФмаХКХЁЃ вдЩЯЮЊВЈЬиТЪЗЂЩњЦїЕФДњТыМАЗжЮіЃЌВЈЬиТЪЗЂЩњФЃПщдкР§ЛЏЪББЛЗжБ№Р§ЛЏЮЊДЎПкЗЂЫЭВЈЬиТЪЗЂЩњЦїКЭДЎПкНгЪеВЈЬиТЪЗЂЩњЦїЁЃНгЯТРДЮвУЧдйРДЗжЮіДЎПкНгЪеФЃПщЕФДњТыЁЃ 1 module my_uart_rx ( 2 clk, rst_n , 3 rs232_rx , rx_data , rx_int , 4 clk_bps , bps_start 5 ); 6 7 input clk; // 50MHz 8 input rst_n ; // 9 input rs232_rx ; // RS232 10 input clk_bps ; // clk_bps 11 output bps_start ; // 12 output [ 7: 0] rx_data ; // 13 output rx_int ; // , 14 15 //--------------------------------------------------------- 16 reg rs232_rx0 , rs232_rx1 , rs232_rx2 , rs232_rx3 ; // 17 wire neg_rs232_rx ; // 18 19 always @ ( posedge clk or negedge rst_n ) begin 20 if(! rst_n ) begin 21 rs232_rx0 22 rs232_rx1 23 rs232_rx2 24 rs232_rx3 25 end 26 else begin 27 rs232_rx0 28 rs232_rx1 29 rs232_rx2 30 rs232_rx3 31 end 32 end 33 // 34 // 35 // 40ns 36 assign neg_rs232_rx = rs232_rx3 & rs232_rx2 & ~rs232_rx1 & ~rs232_rx0; // neg_rs232_rx 37 38 //--------------------------------------------------------- 39 reg bps_start_r ; 40 reg[ 3: 0] num; // 41 reg rx_int ; // , 42 43 always @ ( posedge clk or negedge rst_n ) 44 if(! rst_n ) begin 45 bps_start_r 46 rx_int 47 end 48 else if( neg_rs232_rx ) begin // rs232_rx 49 bps_start_r 50 rx_int 51 end 52 else if( num==4'd12 ) begin // 53 bps_start_r 54 rx_int 55 end 56 57 assign bps_start = bps_start_r ; 58 59 //--------------------------------------------------------- 60 reg[ 7 : 0] rx_data_r ; // 61 //--------------------------------------------------------- 62 63 reg[ 7 : 0] rx_temp_data ; // 64 65 always @ ( posedge clk or negedge rst_n ) 66 if(! rst_n ) begin 67 rx_temp_data 68 num 69 rx_data_r 70 end 71 else if( rx_int ) begin // 72 if( clk_bps ) begin // , 8bit 1 2 73 num 74 case ( num) 75 4'd1:rx_temp_data[0] 76 4'd2:rx_temp_data [1] 77 4'd3:rx_temp_data [2] 78 4'd4:rx_temp_data [3] 79 4'd5:rx_temp_data [4] 80 4'd6:rx_temp_data [5] 81 4'd7:rx_temp_data [6] 82 4'd8:rx_temp_data [7] 83 default : ; 84 endcase 85 end 86 else if( num == 4'd12 ) begin // 1+8+1(2)=11bit 87 num 88 rx_data_r 89 end 90 end 91 92 assign rx_data = rx_data_r ; 93 94 endmodule Ек19ааЕНЕк36ааЮЊЦ№ЪМЮЛМьВтВПЗжЃЌ19ЕН32ааЃЌЪЕЯжСЫЖдrs232_rxЖЫПкЩЯЕчЦНЕФСЌајЫФИіЪБжгжмЦкЕФМФДцЃЌЕк36аадђЖдетСЌај4ИіЪБжгЩЯЩ§биЪБЕФrs232_rxЖЫПкЕчЦННјааТпМВйзїЃЌЕУГіrs232_rxЖЫПкаХКХЯТНЕбиЕФЕНРДЁЃneg_rs232_rx = rs232_rx3 & rs232_rx2 & ~rs232_rx1 & ~rs232_rx0ЃЌМДКѓСНДЮМФДцЕФзДЬЌЮЊЕЭЕчЦНЖјЧАСНДЮМФДцЕФзАЬюЮЊИпЕчЦНЃЌдђБэУїИУЖЫПкЩЯЕФаХКХЗЂЩњСЫ1->0ЕФЬјБфЃЌМДгаЯТНЕбиГіЯжЁЃneg_rs232_rxаХКХЛсВњЩњвЛИіжмЦкЕФИпТіГхЁЃ Ек43аажСЕк55аадђИљОнneg_rs232_rxКЭnumМЦЪ§жЕРДПижЦДЎПкНгЪеВЈЬиТЪЗЂЩњЦїЕФЙЄзїКЭНгЪежаЖЯаХКХЁЃЕк65аажСЕк90аадђВЩгУЯпадађСаЛњЕФЩшМЦЗНЪНЃЌНјаавЛИізжНкЕФЪ§ОнЕФНгЪеЁЃ вдЩЯЮЊЖдДЎПкНгЪеФЃПщЕФвЛИіМђЕЅЗжЮіЃЌНгЯТРДЃЌдйНјааДЎПкЗЂЫЭФЃПщЕФЗжЮіЁЃ 1 module my_uart_tx ( 2 clk, rst_n , 3 rx_data , rx_int , rs232_tx , 4 clk_bps , bps_start 5 ); 6 7 input clk; // 50MHz 8 input rst_n ; // 9 input clk_bps ; // clk_bps_r , 10 input [ 7 : 0] rx_data ; // 11 input rx_int ; 12 output rs232_tx ; // RS232 13 output bps_start ; // 14 15 //--------------------------------------------------------- 16 reg rx_int0 , rx_int1 , rx_int2 ; //rx_int 17 wire neg_rx_int ; // rx_int 18 19 always @ ( posedge clk or negedge rst_n ) begin 20 if(! rst_n ) begin 21 rx_int0 22 rx_int1 23 rx_int2 24 end 25 else begin 26 rx_int0 27 rx_int1 28 rx_int2 29 end 30 end 31 32 assign neg_rx_int = ~rx_int1 & rx_int2 ; // neg_rx_int 33 34 //--------------------------------------------------------- 35 reg[ 7 : 0] tx_data ; // 36 //--------------------------------------------------------- 37 reg bps_start_r ; 38 reg tx_en ; // 39 reg[ 3: 0] num; 40 41 always @ ( posedge clk or negedge rst_n ) begin 42 if(! rst_n ) begin 43 bps_start_r 44 tx_en 45 tx_data 46 end 47 else if( neg_rx_int ) begin // 48 bps_start_r 49 tx_data 50 tx_en 51 end 52 else if( num==4'd11 ) begin // 53 bps_start_r 54 tx_en 55 end 56 end 57 58 assign bps_start = bps_start_r ; 59 60 //--------------------------------------------------------- 61 reg rs232_tx_r ; 62 63 always @ ( posedge clk or negedge rst_n ) begin 64 if(! rst_n ) begin 65 num 66 rs232_tx_r 67 end 68 else if( tx_en ) begin 69 if( clk_bps ) begin 70 num 71 case ( num) 72 4'd0 : rs232_tx_r 73 4'd1 : rs232_tx_r 74 4'd2 : rs232_tx_r 75 4'd3 : rs232_tx_r 76 4'd4 : rs232_tx_r 77 4'd5 : rs232_tx_r 78 4'd6 : rs232_tx_r 79 4'd7 : rs232_tx_r 80 4'd8 : rs232_tx_r 81 4'd9 : rs232_tx_r 82 default : rs232_tx_r 83 endcase 84 end 85 else if( num==4'd11 ) num 86 end 87 end 88 89 assign rs232_tx = rs232_tx_r ; 90 91 endmodule ДњТы19ааЕН30ааЖдДЎПкНгЪеФЃПщЕФНгЪежаЖЯаХКХНјааСЫ3ДЮМФДцЃЌЕк32аадђЭЈЙ§ЖдСЌајСНДЮМФДцНсЙћЕФХаЖЯЃЌРДМьВтНгЪежаЖЯаХКХrx_intЕФЯТНЕбиЁЃШчЙћгаЯТНЕбиЕНРДЃЌneg_rx_intаХКХдђЛсВњЩњвЛИіЪБжгжмЦкЕФИпТіГхаХКХЃЌЕк47аадђЭЈЙ§ЖдИУаХКХЕФзДЬЌХаЖЯЃЌРДШЗЖЈЪЧЗёЦєЖЏЗЂЫЭВЈЬиТЪЗЂЩњЦїФЃПщЁЃШчЙћМьВтЕНСЫИУИпТіГхЃЌдђЪЙФмДЎПкЗЂЫЭ(tx_en FPGAАЎКУепбЇЯАЁЃ дЪМДњТыбщжЄ ЧАУцЃЌЭЈЖдЩшМЦДњТыЕФвЛИіМђЕЅЗжЮіЃЌХЊЧхГўСЫЬиШЈЭЌбЇЩшМЦДњТыЕФЛљБОМмЙЙКЭЫМТЗЁЃФЧУДПДЙ§ЬиШЈЭЌбЇНЬбЇЪгЦЕЕФЖМжЊЕРЃЌИУДњТыФмЙЛЪЕЯжвЛИізжНкЕФЪ§ОнЪеЗЂВтЪдЁЃФЧУДетРяЃЌаЁУЗИчОЭЯШЖдИУЩшМЦНјаавЛИіЗТецЃЌЭЈЙ§ЗТецРДЗжЮіДЫЩшМЦЕФадФмЁЃ ЗТецЕФЫМТЗКмМђЕЅЃЌОЭЪЧЭЈЙ§ФЃФтДЎПкЗЂЫЭЙ§ГЬЃЌИјИУЩшМЦФЃПщЗЂЫЭЪ§ОнЃЌгЩЧАУцЗжЮіПЩжЊЃЌИУЩшМЦФЃПщНгЪеЕНЪ§ОнКѓЃЌЛсСЂМДНЋЪ§ОнЗЂЫЭГіШЅЃЌвђДЫЮвУЧЛЙашвЊЖдДЎПкЗЂЫЭГіРДЕФЪ§ОнНјааЗжЮіЃЌетРяЃЌЪьЯЄUartавщЕФЃЌЮвУЧПЩвджБНгЙлВьЗЂЫЭВЈаЮЁЃЕБШЛЃЌЮЊСЫИќМгжБЙлЃЌЮвУЧвВПЩвдЩшМЦвЛИіФЃФтДЎПкНгЪеЪ§ОнЕФЗТецФЃаЭЃЌЭЈЙ§ИУФЃПщРДЖСШЁДЎПкЗЂЫЭГіРДЕФЪ§ОнЁЃПМТЧЕНПДетЦЊЮФеТЕФДѓЖрЪЧГѕбЇепЃЌЮЊСЫШУДѓМвФмЙЛИќКУЕФВщПДЮвУЧЕФЗТецНсЙћЃЌЭЌЪБНЬДѓМвНјааЗТецФЃаЭЕФЩшМЦЃЌаЁУЗИчЛЙЪЧздМКБраДСЫвЛИіащФтЕФДЎПкЗТецФЃаЭЁЃбщжЄЪБЃЌжЛашвЊНЋИУЗТецФЃаЭЙвНгЕНДЎПкФЃПщЩЯЃЌдђИУФЃаЭБуФмЙЛздЖЏЕФИјДЎПкФЃПщЗЂЫЭЪ§ОнЃЌЭЌЪБНгЪеДЎПкЗЂЫЭЙ§РДЕФЪ§ОнЁЃВЂЛсЪЕЪБЕФНЋЗЂЫЭЕФЪ§ОнКЭНгЪеЕФЪ§ОнДђгЁГіРДЃЌЪЕМЪдкЙлВьЗТецНсЙћЪБЃЌЮвУЧБужЛашвЊЙлПДДђгЁЕФНсЙћОЭПЩвдСЫЁЃИУДЎПкЗТецФЃаЭЕФДњТыШчЯТЫљЪОЃК вдЯТЪЧДњТыЦЌЖЮЃК 1 `timescale 1ns/1ps 2 3 module Uart_module ( uart_rx , uart_tx , send_state ); 4 5 input uart_rx ; 6 output reg uart_tx ; 7 output reg send_state ; 8 9 reg Clk; 10 reg Rst_n ; 11 12 wire Mid_Flag_send ; 13 wire Mid_Flag_Receive ; 14 15 reg Receive_Baud_Start ; 16 reg [ 7 : 0] rx_data ; 17 18 initial Clk = 1; 19 always #10 Clk = ~Clk; 20 21 speed_select speed_select_Send ( 22 . clk( Clk), 23 . rst_n ( Rst_n ), 24 . bps_start ( 1'b1 ), 25 . clk_bps ( Mid_Flag_send ) 26 ); 27 28 speed_select speed_select_receive ( 29 . clk( Clk), 30 . rst_n ( Rst_n ), 31 . bps_start ( Receive_Baud_Start ), 32 . clk_bps ( Mid_Flag_Receive ) 33 ); 34 35 initial begin 36 Rst_n = 0; 37 uart_tx = 1; 38 send_state = 0; 39 #300 Rst_n = 1; 40 41 $display ( "Set Baud As 9600bps" ); 42 #200 ; Uart_Send ( 8'hb6 ); 43 #20 ; Uart_Send ( 8'he7 ); 44 #80 ; Uart_Send ( 8'hf0 ); 45 #500 ; Uart_Send ( 8'h02 ); 46 #300 ; Uart_Send ( 8'hb4 ); 47 #40 ; Uart_Send ( 8'he5 ); 48 #90 ; Uart_Send ( 8'hb0 ); 49 #1000 ; Uart_Send ( 8'h32 ); 50 #2000000 ; 51 $stop ; 52 end 53 54 task Uart_Send ; 55 input [ 7: 0] Data ; 56 begin 57 send_state = 1; 58 @( posedge Mid_Flag_send) #0.1 uart_tx = 0; 59 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [0]; 60 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [1]; 61 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [2]; 62 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [3]; 63 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [4]; 64 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [5]; 65 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [6]; 66 @( posedge Mid_Flag_send) #0.1 uart_tx = Data [7]; 67 @( posedge Mid_Flag_send) #0.1 uart_tx = 1; 68 $display ( "Uart_Send Data = %0h" , Data ); 69 send_state = 0; 70 end 71 endtask 72 73 initial begin 74 forever begin 75 @( negedge uart_rx ) 76 begin 77 Receive_Baud_Start = 1; 78 @( posedge Mid_Flag_Receive); 79 @( posedge Mid_Flag_Receive) rx_data [0] = uart_rx ; 80 @( posedge Mid_Flag_Receive) rx_data [1] = uart_rx ; 81 @( posedge Mid_Flag_Receive) rx_data [2] = uart_rx ; 82 @( posedge Mid_Flag_Receive) rx_data [3] = uart_rx ; 83 @( posedge Mid_Flag_Receive) rx_data [4] = uart_rx ; 84 @( posedge Mid_Flag_Receive) rx_data [5] = uart_rx ; 85 @( posedge Mid_Flag_Receive) rx_data [6] = uart_rx ; 86 @( posedge Mid_Flag_Receive) rx_data [7] = uart_rx ; 87 @( posedge Mid_Flag_Receive) Receive_Baud_Start = 0; 88 $display ( "Uart_receive Data = %0h" , rx_data ); 89 end 90 end 91 end 92 93 endmodule 94 вђЮЊдкНЋДњТыИДжЦЕНwordЕФЙ§ГЬжаЃЌЛсгавЛЖЈЕФИёЪНМцШнЮЪЬтЃЌЫљвдЮФжаВПЗжИёЪНВЛЪЧЬЋЙцЗЖЃЌЭћИїЮЛРэНтЃЌСэЭтЃЌЭъећЕФДњТыЃЌаЁУЗИчвВвдpdfЕФаЮЪНЬсЙЉСЫЃЌИааЫШЄЕФХѓгбПЩвдЯТдибЇЯАЁЃ БОЗТецФЃаЭЕФЕквЛОфЛАЁА`timescale 1ns/1psЁБЮЊЗТецОЋЖШМАЪБМфЕФЫЕУїЃЌЖЈвхЪБМфОЋЖШЮЊ1psЃЌЪБМфЕЅЮЛЮЊ1nsЃЌФЧУДЮвУЧдкДњТыБраДЕФЙ§ГЬжаЃЌШчЙћаДГЩЁА#200ЁБдђБэЪОбгЪБ200nsЃЌвђЮЊЪБМфОЋЖШЮЊ1psЃЌвђДЫЮвУЧЛЙПЩвдНјвЛВНЬсИпбгЪБОЋЖШЃЌШчЁА#200.1ЁББэЪОбгЪБ200.1nsЁЃвЛАуЕФВтЪдЮФМў(testbench)жаЃЌетОфЛАзїЮЊЕквЛОфЛАЃЌБиаДЃЌЕБШЛЃЌЪБМфОЋЖШКЭЕЅЮЛЮвУЧПЩвдИљОнздМКЕФашЧѓИќИФЃЌШчаДГЩЁА`timescale 1us/1nsЁБЛђепЁА`timescale 1ns/1nsЁБЕШЖМЪЧПЩвдЕФЁЃ ИУФЃПщзїЮЊвЛИіЗТецФЃаЭЃЌОЭЪЧащФтСЫвЛИіДЎПкЪеЗЂвЧЦїЃЌМШШЛЪЧвЛИіДЎПкЪеЗЂвЧЦїЃЌдђБиШЛгаДЎПкЗЂЫЭЖЫПкКЭДЎПкНгЪеЖЫПкЃЌвђДЫдкФЃПщУћКѓУцЖЈвхСЫШ§ИіЖЫПкЁЃетгывЛАуЕФtestbenchВЛЭЌЃЌвЛАуЕФtestbenchзїЮЊЗТецЪБЕФЖЅВуЃЌВЛашвЊЖЫПкЃЌвђДЫФЃПщУћКѓОЭжБНгвдЁА;ЁБНсЪјЁЃИУФЃПщЕФШ§ИіЖЫПкЁАuart_rx , uart_tx , send_stateЁБЗжБ№ЮЊДЎПкНгЪеЖЫПкЁЂДЎПкЗЂЫЭЖЫПкЁЂДЎПкЗЂЫЭзДЬЌаХКХЁЃДЎПкЪеЗЂЖЫПкВЛгУЫЕЃЌДѓМввВвбОжЊЕРСЫЃЌДЎПкЗЂЫЭзДЬЌаХКХжївЊзїЮЊжИЪОаХКХЃЌжИЪОЕБЧАЗТецФЃаЭе§дкНјааЪ§ОнЕФЗЂЫЭЙ§ГЬЁЃ Ек9аажСЕк16ааЮЊВтЪдЮФМўжааХКХЕФЖЈвхЃЌвдЧАЮвУЧзмЪЧРэНтЫЕетаЉаХКХОЭЪЧД§ВтЪдФЃПщЕФЖЫПкЃЌашвЊдкВтЪдЮФМўжаЖЈвхЁЃФЧУДетРяаЁУЗИчИќЯВЛЖЛЛвЛжжЗНЪНРДРэНтЃКЮвУЧздМКЕФЩшМЦЃЌБОЩшМЦжаМДЬиШЈЕФДЎПкФЃПщЃЌЪЧвЛИіЙІФмЮДжЊЕФКкКазгЃЌетИіКкКазггавЛаЉаХКХЯпв§ГіЃЌгаЕФаХКХЯпЪЧзїЮЊЪфШыЕФЃЌМДашвЊЭтВПЪфШывЛЖЈЕФаХКХзїЮЊМЄРјЃЌЖјгаЕФаХКХЯпЪЧзїЮЊЪфГіЕФЃЌФмЙЛЪфГівЛаЉЪ§ОнЃЌЕБШЛЛЙгавЛаЉаХКХЯпЪЧМШФмЙЛзїЮЊЪфШыЃЌгжФмЙЛзїЮЊЪфГіЕФЃЌМДШ§ЬЌЁЃЮвУЧвЊЯыжЊЕРетИіКкКазгЕФЙІФмЃЌОЭашвЊИјетИіКкКазгЕФЪфШыаХКХЯпНгЩЯаХКХдДЃЌЭЈЙ§ИјетаЉЪфШыаХКХЯпвЛЖЈЕФМЄРјЃЌЙлВьЦфЪфГіЖЫПкЩЯЕФЯьгІЃЌДгЖјЛёжЊИУКкКазгЕФЙІФмЁЃФЧУДдкетРяЃЌЖдгкД§ВтЪдФЃПщЕФЪфШыЖЫПкЃЌЮвУЧОЭНгЩЯаХКХЗЂЩњЦїЃЌЖдгкЪфГіЖЫПкЃЌЮвУЧОЭНгЩЯЪОВЈЦїЛђепТпМЗжЮівЧЃЌетбљЃЌЮвУЧОЭФмЙЛЭЈЙ§аХКХЗЂЩњЦїИјЪфШыЖЫПкВњЩњвЛЖЈЕФМЄРјЃЌШЛКѓЭЈЙ§ЪОВЈЦїЙлВьЪфГіЖЫПкЕФЪфГіСЫЁЃМДШчЯТЭМЫљЪОЃК  ФЧУДЃЌЮвУЧЕФtestbenchжївЊЪЕЯжаХКХЗЂЩњЦїЕФЙІФмЃЌМШШЛЪЧаХКХЗЂЩњЦїФЧУДОЭвЛЖЈгаЪ§ОнаХКХЪфГіЃЌетИіЪ§ОнаХКХЪфГіОЭПЩвдСЌНгЕНЮвУЧЕФД§ВтФЃПщЩЯЁЃД§ВтЪдФЃПщЕФЪфГіЖЫПкЃЌСЌНгЕНЮвУЧЕФЪОВЈЦїЛђепТпМЗжЮівЧЕФЬНЭЗЩЯЃЌетбљОЭЪЕЯжСЫвЛИіЭъећЕФВтЪдЯЕЭГЃЌФЧУДЮвУЧаХКХЗЂЩњЦїЕФаХКХдДЃЌПЩФмУќУћНазіЃЌaЃЌb,c,d,eЁЁ. ЖјЮвУЧЪОВЈЦїЕФЬНЭЗдђУќУћЮЊЬНЭЗ1ЃЌЬНЭЗ2ЁЁНгЯТРДОЭКУРэНтСЫЃЌдкtestbenchЃЌЮвУЧНЋаХКХЗЂЩњЦїЕФЪфГіаХКХЖЈвхЮЊregаЭЃЌЖјЪОВЈЦїЕФЬНЭЗЖЈвхЮЊwireаЭЁЃЮвУЧаХКХЗЂЩњЦїЕФЪфГіаХКХЯпКЭЪОВЈЦїЕФЬНЭЗЯпЖМПЩвдШЮвтУќУћЃЌЪЕМЪЪЙгУЪБвЛвЛЖдгІСЌНгЕНД§ВтЪдФЃПщЕФЖЫПкЩЯЃЌвВПЩвдОЭжБНггыД§ВтФЃПщЕФИїИіЖЫПкУћБЃГжвЛжТЁЃБОЩшМЦжаЃЌаЁУЗИчШУtestbenchжаЕФаХКХгыД§ВтФЃПщЕФЖЫПкБЃГжвЛжТЁЃ Ек18ааКЭ19ааЮЊВњЩњ50MHzЪБжгЕФгяОфЁЃ вђЮЊБОЗТецФЃаЭЪЕжЪЩЯОЭЪЧвЛИіДЎПкЪеЗЂФЃПщЃЌвђДЫвВашвЊгаЪеЗЂВЈЬиТЪЗЂЩњЦїЃЌетРяаЁУЗИчЮЊСЫЪЁЪТЃЌжБНгЕїгУСЫЬиШЈЭЌбЇЕФВЈЬиТЪЗЂЩњЦїФЃПщЃЌРДзїЮЊЮвЗТецФЃаЭЕФВЈЬиТЪЗЂЩњЦїЁЃвђЮЊИУВЈЬиТЪЗЂЩњЦїБОЩэвВЪєгкД§ВтЪдВПЗжЃЌаЁУЗИчжЎЫљвдИвЗХаФЕФЕїгУЃЌЪЧвђЮЊЪТЯШЮввбОЭЈЙ§ЗТецЃЌШЗЖЈСЫИУВЈЬиТЪЗЂЩњЦїЙІФмЕФе§ШЗадЁЃЕк21аажС33ааЮЊЗжБ№Р§ЛЏЕУЕНЗЂЫЭВЈЬиТЪЗЂЩњЦїКЭНгЪеВЈЬиТЪЗЂЩњЦїЕФДњТыЁЃ Ек54аажС71ааЮЊЗЂЫЭвЛИіЭъећзжНкЕФЪ§Он(здЖЏЬэМгЦ№ЪМЮЛКЭЭЃжЙЮЛ)ЕФДњТыЃЌИУВПЗжаДГЩШЮЮёЕФаЮЪНЃЌЗНБуЕїгУЁЃЕБЮвУЧашвЊЗЂЫЭвЛИізжНкЕФЪ§ОнЪБЃЌР§ШчЃЌЗЂЫЭ8'hb6ЃЌжЛашвЊаДЁАUart_Send ( 8'hb6 )ЁБМДПЩЃЌИУШЮЮёБуНЋздЖЏжДааЃЌНЋЪ§ОнЗЂЫЭГіШЅЁЃдквЛИізжНкЕФЪ§ОнЗЂЫЭЭъГЩКѓЃЌЭЌЪБЪЙгУЯЕЭГШЮЮё$displayРДДђгЁЕБЧАЗЂЫЭЕФЪ§ОнЪЧЖрЩйЃЌвдЗНБуЮвУЧжБЙлЕФЙлВьЗТецдЫааЙ§ГЬЁЃжСгк$displayетИіЯЕЭГШЮЮёжаИїИіВПЗжЕФКЌвхЃЌЧыЖСепздаадФЖСverilogЕФгяЗЈЪщЁЃДњТыЕФ42жС49ааБуЪЧЕїгУДЫШЮЮёНјааСЫЖрДЮЪ§ОнЕФЗЂЫЭЁЃ 73аажС91ааЮЊФЃФтДЎПкНгЪеВПЗжЃЌЭЈЙ§ЖдДЎПкФЃПщЗЂЫЭГіРДЕФЪ§ОнНјааНгЪеЃЌВЂНЋНгЪеЕНЕФЪ§ОнгУ$displayКЏЪ§ДђгЁГіРДЁЃЮвУЧжЛашвЊдФЖСЗЂЫЭЪ§ОнКЭНгЪеЪ§ОнКѓДђгЁГіРДЕФаХЯЂЃЌМДПЩХаЖЯЭЈаХЪЧЗёГЩЙІЃЌД§ВтФЃПщЙІФмЪЧЗёе§ГЃЁЃ етРяашвЊзЂвтЕФЪЧЃЌДђгЁГіРДЕФНгЪеЪ§ОнКЭЗЂЫЭЪ§ОнЪЧеыЖдЗТецФЃаЭРДЫЕЕФЃЌsend dataЪЧЗТецФЃаЭЗЂЫЭГіШЅЕФЪ§ОнЃЌЖдгІД§ВтФЃПщгІИУНгЪеЕНЕФЪ§ОнЁЃreceive dataдђЪЧЗТецФЃаЭНгЪеЕНЕФЪ§ОнЃЌЖдгІД§ВтФЃПщЗЂЫЭЕФЪ§ОнЁЃ ЮвУЧЫљБраДЕФВтЪдЮФМўЃЌвЛЖЈвЊЪЧПЩПиЕФЃЌМДдкЫљгаЪТЮёЭъГЩКѓЃЌНЋЗТецЭЃЯТРДЃЌЗёдђЃЌЗТецЛсвЛжБНјааЯТШЅЃЌЕМжТГіЯжДѓСПШпгрВЈаЮЃЌгАЯьЮвУЧЖдЗТецНсЙћЕФЗжЮіЁЃвђДЫдкЕк51ааЃЌЕБЫљгаВтЪдвбОЭъГЩКѓЃЌЪЙгУЯЕЭГШЮЮё$stopНЋЗТецЭЃЯТРДЁЃ вдЩЯЖдаЁУЗИчаДЕФДЎПкЗТецФЃаЭНјааСЫНщЩмЃЌдкЪЕМЪЪЙгУжаЃЌжЛашвЊНЋИУФЃаЭгыД§ВтФЃПщАДееШчЯТЭМЫљЪОЕФЗНЪНСЌНгЦ№РДМДПЩЁЃ  етРяЃЌаЁУЗИчЪЙгУвЛИіtestbenchЮФМўзїЮЊЖЅВуЃЌНЋетСНИіВПЗжСЌНгЦ№РДЃЌЭЌЪБВњЩњmy_uart_topЙЄзїЫљашЕФЪБжгКЭИДЮЛаХКХЁЃИУЮФМўЯъЯИДњТыШчЯТЃК 1 `timescale 1ns /1ns 2 3 module Uart_tb ; 4 5 reg Clk; 6 reg Rst_n ; 7 8 wire uart_rx ; 9 wire uart_tx ; 10 wire send_state ; 11 12 my_uart_top u1 ( 13 . clk( Clk), 14 . rst_n ( Rst_n ), 15 . rs232_rx ( uart_tx ), 16 . rs232_tx ( uart_rx ) 17 ); 18 19 Uart_module u2 ( 20 . uart_rx ( uart_rx ), 21 . uart_tx ( uart_tx ), 22 . send_state ( send_state ) 23 ); 24 25 initial begin 26 Clk = 1; 27 Rst_n = 0; 28 #200 ; 29 Rst_n = 1; 30 end 31 32 always #10 Clk = ~Clk; 33 34 endmodule 35 ИУДњТыЪЕдкМђЕЅЃЌжЛЪЧЪЕЯжСЫвЛИіЦєЖЏЪБЕФГѕЪМЛЏКЭ50MHzЪБжгЕФВњЩњЃЌвђДЫаЁУЗИчОЭВЛзіШЮКЮЗжЮіСЫЁЃ |

ЭјгбЦРТл