Xilinx FPGA入门连载42:UART loopback测试

发布时间:2016-1-4 09:40

发布者:rousong1989

|

Xilinx FPGA入门连载42:UART loopback测试 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1jGjAhEm

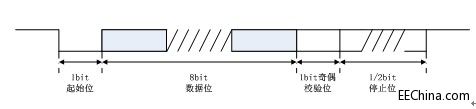

UART(Universal Asynchronous Receiver/Transmitter),即通用异步收发,它的数据传输不需要时钟,只要两条信号线分别进行数据收发。既然没有时钟,那么他们是如何保证数据收发的准确性的?很简单,收发双方首先需要做到知己知彼,约定好数据传输的速率(简单的讲就是约定好一个数据位传输的时间)和帧格式(即一帧的长短,一帧由哪些位组成,他们的功能都是什么)。 我们看看UART的一个帧定义。简单的串口帧格式如图所示,它由1个起始位(必须为0)、8个数据位(用户数据)、1个奇偶校验位(用于简单的纠错以保证传输可靠性)和1或2个停止位(必须为1)组成。除了奇偶校验位,其他三个部分都是必须的。当信号线空闲时,必须为高电平。要发起数据传输时,1个低电平的脉冲表示起始位,然后连续传输8个数据位和若干个高电平的停止位,这样便完成一次传输。

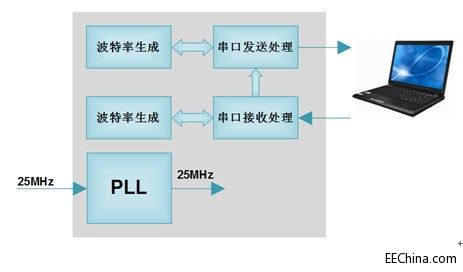

该实验要实现的功能是FPGA实时监测uart_rx信号是否有数据,若接收到数据,则把接收到的数据通过uart_tx发回给对方。PC机使用一个串口调试助手进行通信。 在代码设计中,speed_setting.v模块里可以修改收发数据的波特率,如9600bps,19200bps,38400bps,57600bps或115200bps等。发送的数据帧格式为:1bit起始位,8bit数据,无校验位,1bit停止位。 该实例的内部功能如图所示。

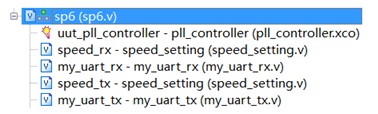

该工程实例的设计模块层次如图所示。

my_uart_rx.v模块主要是完成数据的接收,speed_setting.v(speed_rx)模块主要响应my_uart_rx.v模块发出的使能信号进行波特率控制,并且回送一个数据采样使能信号。my_uart_tx.v模块在my_uart_rx.v模块接收好一个完整的数据帧后启动运行,将接收到的数据作为发送数据返回给PC端,它的波特率控制是由speed_setting.v(speed_tx)模块产生。 连接好下载线,给SP6开发板供电(供电的同时也连接好了UART)。 打开ISE,进入iMPACT下载界面,将本实例工程下的sp6.bit文件烧录到FPGA中在线运行。 双击如图所示的“串口调试器”,。

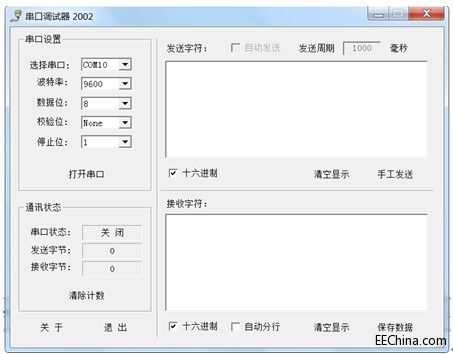

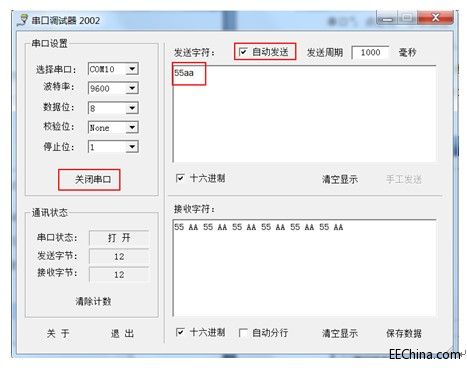

如图6.109所示,打开串口调试器后,选择串口为COM10(我们前面在硬件管理器中新识别到的COM口,实验者应以自己电脑识别到的COM口为准),设置波特率为9600,数据位为8,校验位为None,停止位为1。点击“打开串口”。

如图所示,当我们点击完“打开串口”,其显示字符就变成了“关闭串口”;输入需要发送的数据“55aa”,然后勾选上“自动发送”,我们就可以看到接收字符下面的空白区域每隔一会就打印一组我们发送的字符串。这说明我们的实验成功了。大家可以更改代码中的波特率再进行测试,也可以将返回的数据做一些更改,如将接收的数据取反后返回,最后在串口调试助手上再做些调试,看看是否达到预定的功能。

|

网友评论