Xilinx FPGAШыУХСЌди35ЃКГЌЩљВЈВтОржеМЋНсЙћЯдЪОжЎГЫЗЈЦїIPНтЮі

ЗЂВМЪБМфЃК2015-12-7 12:00

ЗЂВМепЃКrousong1989

|

Xilinx FPGAШыУХСЌди35ЃКГЌЩљВЈВтОржеМЋНсЙћЯдЪОжЎГЫЗЈЦїIPНтЮі ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1jGjAhEm

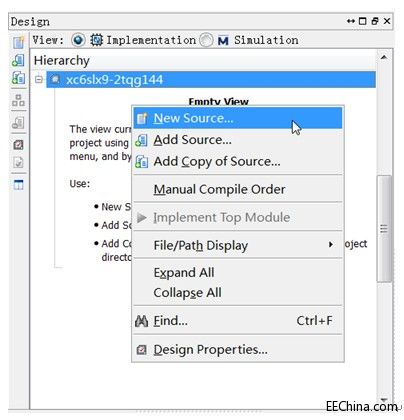

дкБОР§ГЬЕФЙЄГЬдДТыdistance_compute.vжаЃЌР§ЛЏСЫвЛИіГЫЗЈЦїIPКЫЁЃетРяЮвУЧМђЕЅЕФРДПДПДетИіIPКЫЪЧШчКЮДДНЈЁЂХфжУВЂЪЙгУЕФЁЃ ДђПЊISEЙЄГЬЃЌШчЭМЫљЪОЃЌдкЁАDesign ЈЄ Implementation ЈЄ HierarchyЁБжаЕФШЮвтЮЛжУЕЅЛїЪѓБъгвМќЃЌЕЏГіВЫЕЅжабЁдёЁАNew Source..ЁБЁЃ

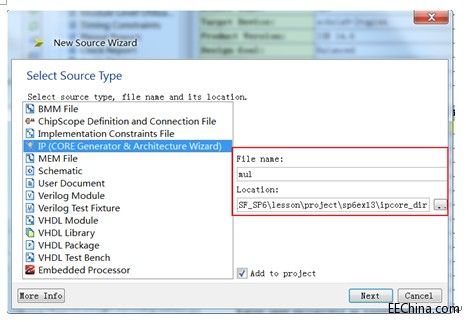

дкЁАNew Source WizardЁБжаЃЌзіШчЭМЫљЪОЕФЩшжУЁЃ Ёё ЁАSelect Source TypeЁБжабЁдёаТНЈЮФМўРраЭЮЊЁАIP(CORE Generator & Architecture Wizard)ЁБЁЃ Ёё ЁАFile nameЁБМДЮФМўУћЃЌЮвУЧУќУћЮЊЁАmuxЁБЁЃ Ёё ЁАLocationЁБЯТУцЪфШыетИіаТНЈЮФМўЫљДцЗХЕФТЗОЖЃЌЮвУЧНЋЦфЖЈЮЛЕНЙЄГЬТЗОЖЯТЕФЁАipcore_dirЁБЮФМўМаЯТЁЃ Ёё ЙДбЁЩЯЁАAdd to projectЁБЁЃ

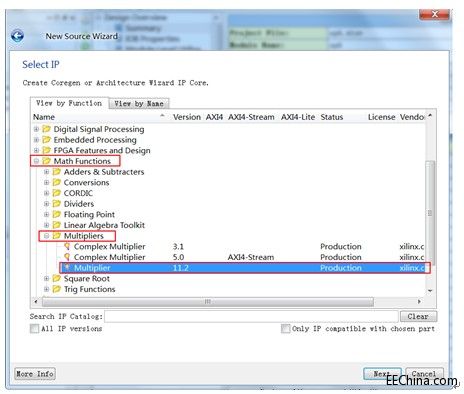

ЭъГЩвдЩЯЩшжУКѓЃЌЕуЛїЁАNextЁБНјШыЯТвЛВНЁЃ дкЁАSelect IPЁБвГУцжаЃЌШчЭМЫљЪОЃЌЮвУЧдкЁАViewby FunctionЁБЯТУцевЕНЁАMath Functions ЈЄ Multipliers ЈЄ MultiplierЁБЃЌЕЅЛїбЁжаЫќЃЌНгзХЕуЛїЁАNextЁБНјШыЯТвЛВНЁЃ

ШчЭМЫљЪОЃЌЕЏГіЁАSummaryЁБвГУцКѓЃЌЕуЛїЁАFinishЁБМДПЩЁЃ

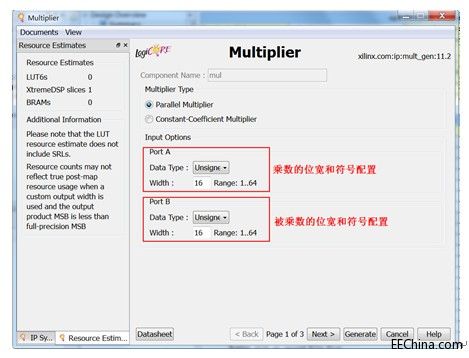

дкMultiplierЕФЕквЛИіХфжУвГУцжаЃЌЮвУЧбЁдёЖдГЫЗЈЦїЕФСНИіЪфШыportЃЈМДГЫЪ§КЭБЛГЫЪ§ЃЉНјааХфжУЃЌбЁдёЫќЕФDataTypeЮЊЁАUnsignedЁБЃЌМДЮоЗћКХЪ§ЃЛЫќЕФWidthЮЊЁА16ЁБЃЌМДЮЛПэ16bitЁЃ

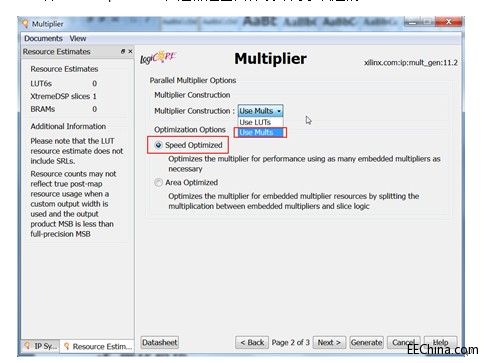

ЕкЖўИіХфжУвГУцжаЃЌШчЭМЫљЪОЁЃ Ёё бЁдёЁАMultiplier ConstructionЁБЮЊЁАUse MultsЁБЃЌМДЪЙгУFPGAФкВПЕФзЈгУГЫЗЈЦїРДЪЕЯжетИіIPКЫЁЃЕБШЛСЫЃЌвВПЩвдбЁдёЁАUse LUTsЁБЃЌетвтЮЖзХетИіГЫЗЈЦїЪЧЪЙгУFPGAЕФТпМзЪдДЪЕЯжЕФЁЃ Ёё ЙДбЁЁАSpeed OptimizedЁБЃЈЫйЖШгХЛЏЃЉЃЌЭЈГЃдкзЪдДЗсИЛЃЌЫйЖШвЊЧѓИпЕФЪБКђЃЌЮвУЧбЁдёЁАSpeed OptimizedЁБЁЃЖјдкЫйЖШвЊЧѓВЛИпЃЌзЪдДНєеХЕФЪБКђЃЌЮвУЧЭЈГЃЛсбЁдёСэвЛИібЁЯюЁАArea OptimizedЁБЃЌетЖМЪЧгЩОпЬхЩшМЦашЧѓОіЖЈЕФЁЃ

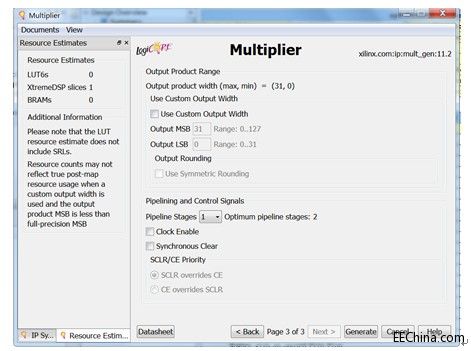

ЕкШ§ИіХфжУвГУцжаЃЌЮвУЧЮоашзіЩшжУЃЌжБНгЕуЛїЁАGenerateЁБЩњГЩХфжУКУЕФIPКЫМДПЩЁЃ

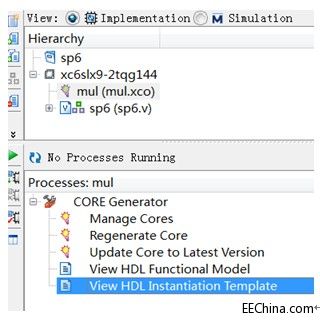

ЁАGenerateЁБЭъГЩКѓЃЌШчЭМЫљЪОЃЌЮвУЧПЩвддкЁАHierarchyЁБжабЁжаmul.xcoМДИеИеВњЩњЕФIPКЫФЃПщЃЌШЛКѓЫЋЛїДђЁАProcessesЁБЯТЕФЁАView HDLInstantiation TemplateЁБВщПДIPКЫЕФР§ЛЏФЃАхЁЃ

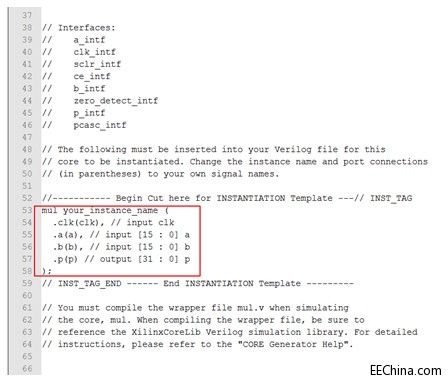

Р§ЛЏФЃАхДђПЊШчЭМЫљЪОЃЌОиаЮЧјгђФкЕФДњТыЮвУЧИДжЦЕНЙЄГЬдДТыжаЃЌЖдЁА( )ЁБФкЕФНгПкзіКУгГЩфЃЌОЭПЩвдНЋЦфМЏГЩЕНЮвУЧЕФЩшМЦжаЁЃ

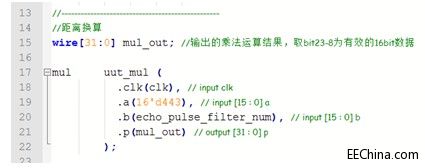

ШчЯТДњТыЫљЪОЃЌдкЮвУЧЕФЩшМЦжаЃЌГЫЗЈЦїЕФСНИіЪфШыaКЭbЗжБ№ЮЊГЃЪ§443КЭГЌЩљВЈВтОрЕФТіПэМЦЪ§МФДцЦїecho_pulse_filter_numЃЌЪфГіНсЙћЮЊ32bitЕФmul_outЁЃ

|

ЭјгбЦРТл