越快越好:GSPS ADC实现宽带宽RF数字化仪

发布时间:2015-12-4 14:30

发布者:designapp

|

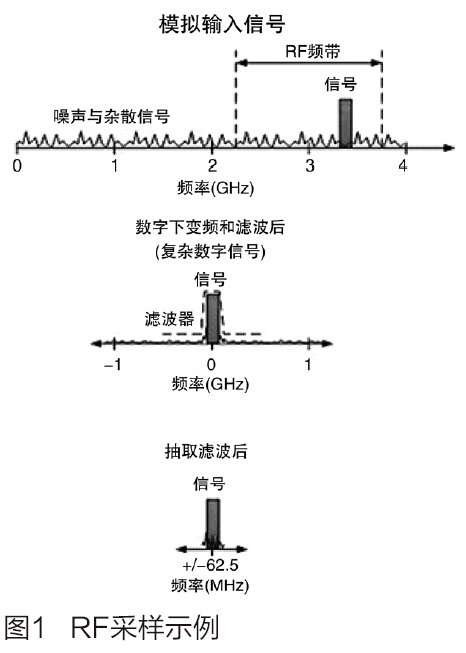

摘要:本文讨论即将来临的3.3V控制器局域网 (CAN) 收发器在工业领域的应用,敬请关注。 过去5年间,速度在1GSPS以上的高速ADC技术的采样率和性能不断提升,全新器件能够实现RF频谱的直接采样。这些全新的模数转换器 (ADC) 能够在保持出色噪声和线性的同时,在3GHz或更高的频率上,以大于1GHz的带宽对信号进行采样。更高的采样率是实现这个功能的关键所在,更快速的采样率可以大大减少宽带宽RF数字化仪的尺寸和功率。 可以考虑一下,一个12位4 GSPS ADC,比如ADC12J4000,是如何能够直接在RF上采样1GHz带宽的信号。它的3.3GHz输入带宽可实现在第二那奎斯特区域的信号采样。为了防止其它目标数字频带外的信号干扰数字化信号,需要一个抗混叠滤波器来减少其它那奎斯特区域内的带外信号混叠进入目标信号。  为了将已采样信号放置在第二那奎斯特区域的中央,并且在最接近的1.5GHz混叠频率上使用一个具有60dB抑制性能的滤波器,我们需要一个3:1的整形因数。相对来说,虽然理论上可以使用处于第三那奎斯特区域中央的较低采样率,比如2.5GSPS,所需的抗混叠滤波器的采样因数将为1.5:1(整形因数越低,实现起来就越困难)。具有更高采样率的较宽松滤波器要求可以通过减少所需的谐振器或偶极子的数量来大大减少滤波器的系统尺寸、重量和成本。 在很多诸如信号智能、电子对抗和卫星通信的应用中,需要将微波或更高频带内10GHz或以上的频率范围数字化。通常情况下,这由GSPS ADC将信号下变频至2~4GHz以实现其数字化来完成。每条信号链都需要单独的放大器、混频器、合成器、滤波器和ADC。 ADC的采样率越高,需要的信号链就越少。例如,假定带宽占用达到70%,一个2.5 GSPS ADC需要12个单独的下变频级,而4 GSPS ADC只需要7个。这直接使数字化仪的尺寸、功率和重量减少了42%。 更快速的采样率还提升了较窄带宽系统的性能、功率和密度。如图1中,一个100MHz的信号位于3GHz频带中央的1.5GHz频带内,由采样率为4 GSPS ADC进行采样。采样后,ADC内的集成数字下变频转换器可被用来隔离目标信号,并且过滤掉所有目标信号以外的有害噪声和干扰能量。 然后可以将采样率减少32倍,达到125MSPS复采样,刚好能够支持所需的信号带宽。与通过取采样数量的平方根值,用更多的采样提升信噪比 (SNR) 的方法相类似,已抽取的数据比ADC SNR高,高出的值为ADC与输出采样率之间比率的常用对数的10倍。借助较低的输出采样率,ADC12J4000的灵活JESD204B接口能够只通过一条串化器/解串器 (SERDES) 信道输出信号,从而可以使大量的ADC 被连接至单个FPGA,并且每个ADC的接口功率更低。 对于宽频带RF数字化仪的设计人员来说,采样率的确是越快越好。 |

网友评论