接收机的中频处理技术

发布时间:2015-11-30 14:24

发布者:designapp

|

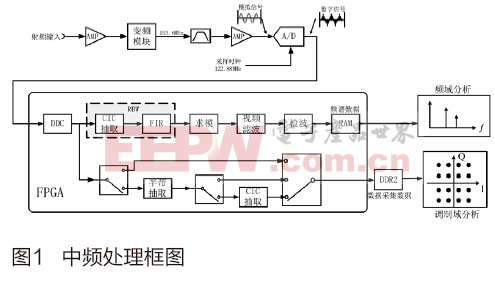

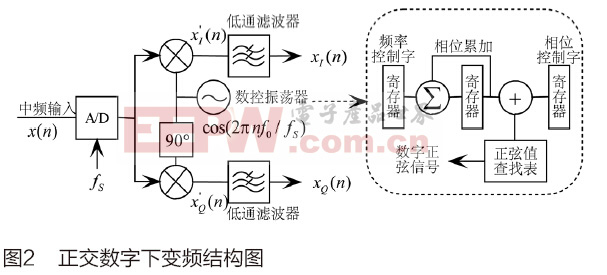

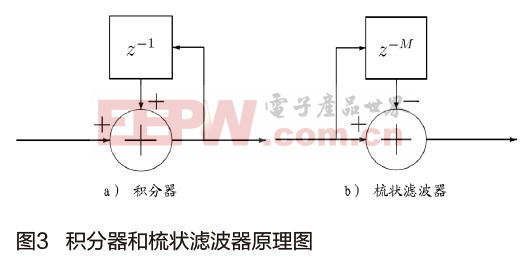

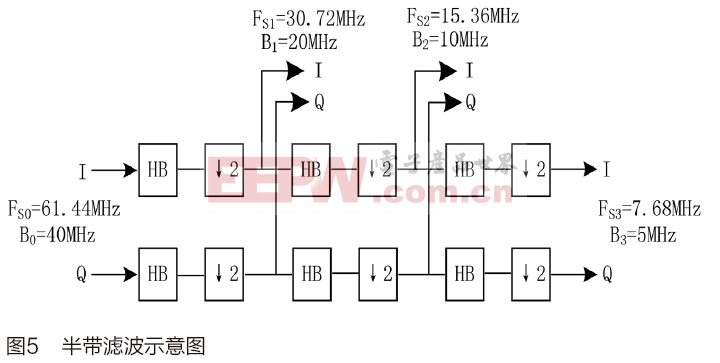

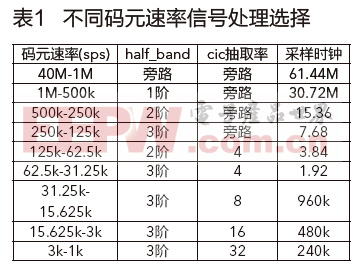

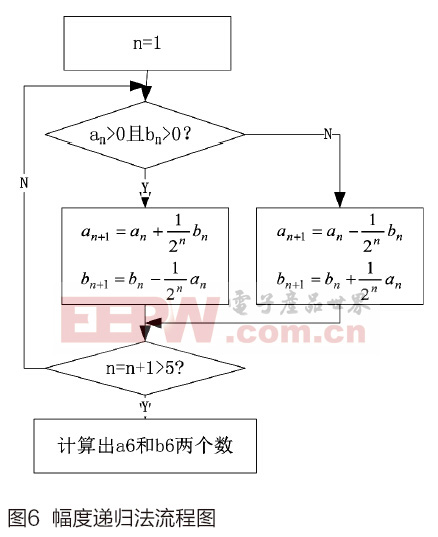

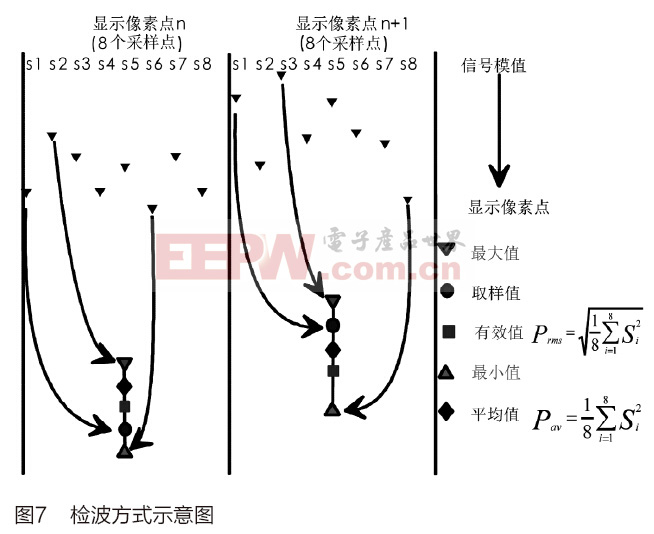

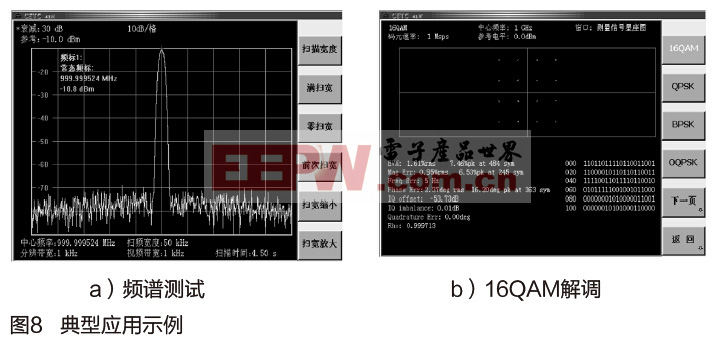

摘要:本文对数字中频信号处理技术进行了研究,采用软件无线电的设计思想和解决方案,提出了一种基于“AD+FPGA”的中频信号处理技术,在频谱分析仪及信号分析仪等接收机中应用广泛。 引言 随着数字技术的发展,接收机的设计越来越多地采用软件无线电(software radio)的思想,以开放性、可扩展、结构精简的硬件为通用平台,把尽量多的功能用可重构、可升级的构件化软件来实现。从实际设计来说,射频模块尽量简化,将信号通过ADC转换为数字信号进行处理,提高接收机的稳定性、通用性并降低实现成本。在接收机中,最常用的是频谱分析和信号分析功能,本文以现场可编程逻辑器件(FPGA)为设计基础,简述频谱分析和信号分析的中频处理。 1 方案 输入的射频信号经过变频模块生成153.6MHz的中频信号,通过ADC进行122.88MHz频率采样,数字信号送入FPGA进行数字下变频(DDC)、CIC抽取、RBW滤波、求模、视频滤波、检波后存入RAM后送CPU进行频谱分析;经过DDC、半带滤波及CIC后存入DDR2后送CPU进行信号分析,包括矢量信号解调,GSM、TD-SCDMA、WCDMA、TD-LTE及FDD-LTE分析等通信制式的非信令解调。具体中频处理框图如图1所示。  2 具体实现 2.1 模数转换(AD) ADC是整个中频处理的关键部分,它直接关系到整个接收机的性能指标,其选用主要参考二个指示,即信噪比和采样频率。由于信噪比与ADC的有效位数有直接关系:SNR=(6.02N+1.76)dB,其中N为ADC的位数,所以尽量选用高位数ADC;同时,由于中频的宽带化需求,需要高采样时钟的ADC,如要满足40MHz的分析带宽,理论上要求采样时钟大于80MHz,本设计的采样时钟为122.88MHz。综合两方面考虑,ADC我们选用了LINERA公司的LTM9001。 2.2 数字下变频 数字下变频(DDC)是数字接收机中的关键技术,广泛应用于雷达、声纳和无线电接收机中,主要将中频信号混频到基带,便于后续处理。它跟模拟下变频类似,包括数字混频器、数字控制振荡器及数字低通滤波器三部分,基本结构图见图2所示。  在本设计中,由于fo=153.6MHz,fs=122.88MHz,满足fo/ fs =(2n+1)/4,NCO输出为cos(0)、cos(π/2)、cos(π)、cos(3π/4),即1,0,-1,0等几个特殊值,实现了免混频,用简单的组合逻辑和取反电路就能实现,具体方法为:先将输入信号每隔2 个取2 补码,形成一个新的数据流;再将新数据流每隔一个置0,所得输出就是混频后的信号。 2.3 CIC抽取滤波 在数据处理系统中,经常需要将信号的采样率降低以便其后进行数字处理或存储,接收机最常用的是CIC抽取滤波或半带抽取滤波。CIC滤波器是级联积分梳状滤波器(Cascaded Integrator-Comb Filter)的简称,其基本构成单元是积分器和梳状滤波器。经过若干级级联后可实现采样率整数倍的抽取和内插,在接收机的设计中,主要采用CIC进行抽取。抽取滤波器可以实现降低取样速率并能使通带混叠或误差依据在要求的范围之内。积分器和梳状滤波器的原理图如图3所示。   在滤波器的实现时,CIC将只有加法而没有乘法,有效地节省了硬件资源。其FPGA实现框图及其控制时序图如下,只需通过改变抽取率R值,就可以实现大范围整数倍抽取。 2.4 RBW 信号经CIC滤波器抽取后降低了率采样速率,但频谱分析仪需要实现从1Hz~3MHz的分辨率带宽,此时,为了得到更高质量的频谱波形,需要添加高斯FIR滤波,这里RBW大于等于1kHz时选择了25级、22 bit滤波器系数,RBW小于1kHz时选择了1024级,22 bit滤波器系数,满足带外衰减优于100 dB。   2.5 半带滤波抽取 半带滤波器(Half-Band Filter)在多速率信号处理中有着特别重要的位置,半带FIR滤波器系数对称、约一半的系数为零,可节约FPGA的MAC资源,是一种高效的数字滤波器。因此这种滤波器特别适合实现  (即2的幂次方倍)的抽取或内插,而且计算效率高,实时性强。 图5采用半带抽取方式实现降低信号采样速率的要求。假设有N级半带滤波器实现抽取,FS0是输入采样速率,FSN是第N级半带滤波器的输入采样速率,则FSN= FS0/2N,且信号经过每一级半带滤波器抽取后,带宽变为原来的一半。半带滤波和CIC抽取滤波结合降低信号的采样率,实现大跨度码元速率信号的处理。 2.6 求模 数字中频信号经下变频分解为正交的I和Q路,经滤波处理过后,信号序列的每一点分别对应I路和Q路的两个值a和b。  就是信号序列每一点的幅度值。由于采用了硬件方式实现幅度运算,会消耗大量的硬件资源。在这里,采用一种新的逼近算法,采用寄存器结构即可实现,首先对数据a和b分别移位处理得到绝对值,然后计算  ,  ;按照下面的框图递推计算a (n)并逼近真值,增加循环次数可提高数值精度。当递归次数n等于6时,可得到精确的幅度值,误差为0.02dB。   2.7 视频滤波 视频滤波器在求模值之后,是一种低通滤波器,用以平均噪声起伏,平滑显示结果。一个较窄的视频滤波器相当于一个平均电路,虽然它不能改变灵敏度,但能减小噪声对被观测信号的影响。在缺省情况下,一般设置为与分辨率相等,但在测量脉冲信号或随机信号时,适当加大或减小视频滤波带宽可以更准确地观察信号。该设计采用一阶滞后滤波法来实现视频滤波。 一阶滞后滤波法首先选择一个常数a=0~1,计算方式为:本次滤波结果=(1-a)*本次采样值+a*上次滤波结果。它可以对周期性干扰具有良好的抑制作用,适用于波动频率较高的场合,缺点就是灵敏度偏低。 2.8 检波 数字系统有一个固有的问题,就是无论显示使用多少个数据点,每个点都代表一定的频率间隔和一定时间间隔内的数值,这个间隔称为进程(Bucket)。检波方式就是对每个进程所包含的子进程数据进行不同方式选取,使每个进程得到一个检波数据输出并显示在屏幕上。频谱仪常用检波方式主要有取样值、最大值、最小值、有效值及平均值检波等方式,其检波方式如图7所示。 2.9 存储 在频谱分析应用中,由于数据量较少,存储介质采用FPGA内部的RAM(XC5VSX35T内部RAM空间3Mb左右)即可,但在数据分析过程中,经常需要采集大数据量的信号数据,例如在TD-LTE信号分析中,经常需要用61.44MHz采样时钟采集10ms的IQ两路各16位数据,数据量约为18Mb,TD-LTE-A信号分析,所以采用了基于FPGA的DDR2 SDRAM存储方案,如MT47H128M16存储容量为2GB。在设计时必须考虑正确的布线阻抗、传播延迟以及信号完整性等因素,通过FPGA内的MIG等实现对DDR2的控制,根据需要选择控制命令组合,完成简单可靠的数据存储。 3 结果 输入信号经过上述流程处理经CPU计算显示后,可以实现频谱分析及矢量信号、通信制式信号解调等众多功能,其典型测量应用示例见图8。  4 结论 本中频信号处理采用了软件无线电的设计理念,硬件结构简单,主要的数据处理都采用软件模块重构思路,应用灵活,能完成大跨度码元速率信号的频谱,解调等分析,只要不大于分析带宽的信号就能够实现处理并通过存储计算的方式得到分析,完全满足设计需要,在接收机领域应用广泛,采用该设计的接收机已经投放市场并得到了市场检验。 参考文献: [1] 杨小牛,楼才义,徐建良.软件无线电技术及应用[M].北京:北京理工大学出版社,2010 [2] 丁玉华,高西全. 数字信号处理[M].西安:西安电子科技大学出版社,2000 [3] 陈爽. 高性能频谱分析仪中频信号处理技术研究[J].合肥工业大学,2007 [4] 张黎明. 高性能数字接收机FPGA设计[J].电子产品世界:2013.5:40-42 [5] 陈旻,刘平.频谱分析仪检波方式的分析与研究[J].现代电子技术:2010.1(312):97-102 |

网友评论