ЛљгкST40GX1гыSTi5514ЕФЭјТчНЛЛЅЪНЪ§зжЕчЪгЛњЖЅКагВМўЩшМЦ

ЗЂВМЪБМфЃК2015-11-24 11:05

ЗЂВМепЃКdesignapp

|

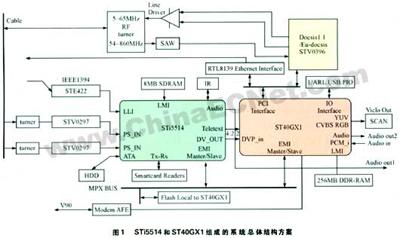

ЁЁЁЁНЛЛЅЪНЛњЖЅКаЁЂЪ§зжЕчЪгвбОДгЗжСЂЦїМўНсЙЙЗЂеЙЕНЕЅаОЦЌНтОіЗНАИЃЌетЪЧЪ§зжДѓЙцФЃМЏГЩЕчТЗжЦдьЙЄвеММЪѕНјВНЕФНсЙћЃЌвВЪЧзюДѓЯоЖШНЕЕЭЯЕЭГГЩБОЕФБиШЛвЊЧѓЁЃ ЁЁЁЁЯжДњЕЅаОЦЌНтОіЗНАИЕФЛњЖЅКавЛАуМЏГЩгаCPUЁЂНтИДгУЁЂвєЦЕЪгЦЕНтТыЁЂЖўЮЌЭМаЮДІРэЁЂБрТыКЭЭтЩшЖЫПкЕШФЃПщЁЃЮЊНкЪЁаОЦЌУцЛ§ЁЂетаЉЖРСЂВПЗжЪЧЭЈЙ§змЯпЗНЪНСЌНгдквЛЦ№ЕФЁЃИФНјЯЕЭГЕФадФмЃЌЭЈГЃЪЧЬсИпCPUЕФЫйЖШЁЂдіЧПЖўЮЌФЫжСШ§ЮЌЭМаЮЕФДІРэФмСІЁЂдіМгЭтЩшЖЫПкЕФНгПкЪ§ФПКЭРрБ№ЕШЗНУцзХЪжЃЌДгЖјДгзмЬхЩЯЬсИпЯЕЭГЕФНЛЛЅДІРэФмСІЁЃЕЋгЩгкЪгЦЕНтИДгУЦїКЭвєЦЕЪгЦЕНтТыЦїЖдДцШЁЪ§ОнзмЯпЪЕЪБадвЊЧѓбЯИёЃЌдіМгСЫCPUДІРэЕШД§ЪБМфЃЌаЮГЩСЫЫљЮНЕФзмЯпЦПОБЁЃгаЙиВтЪдБэУїЃЌзмЯпЦПОБЪЙЕУCPUЕФжДаажИСюЕШД§ЪБМфДяЕНСЫ76%ЃЌетжжЕЅДПвРППЬсИпCPUадФмРДПЫЗўДІРэФмСІВЛзуЕФЗНЪНЃЌВЂВЛФмЬсИпадМлБШЃЌЖјИФЩЦзмЯпЦПОБПЩвдЭЈЙ§ИФНјЛђдіМгЯЕЭГЛЅСЊзмЯпРДЭъГЩЃЌЕЋетБиНЋдіМгаОЦЌжЦдьжаЛЅСЊЯпЕФИДдгЖШЃЌДгЖјдіМгГЩБОЁЃ ЁЁЁЁГ§СЫзмЯпЦПОБДјРДЕФЮЪЬтЭтЃЌЫцзХгУЛЇЖдНгШыЗНЪНЖрбљадвдМАЭМаЮЭМЯѓДІРэвЊЧѓЕФШевцЬсИпЃЌЭЈЙ§ЕчЛАЯпЛиДЋЕФНЛЛЅЪНЛњЖЅКаЁЂЪ§зжЕчЪгЕФеДјНгШыЗНЪНвдМАгаЯоЕФМЦЫуФмСІвВдНРДдНВЛФмТњзуШЫУЧЕФвЊЧѓЃЌЫцзХгаЯпHFCЭјЕФЫЋЯђИФдьвдМАгыЕчаХЭјЁЂЛЅСЊЭјШ§ЭјКЯвЛНјГЬЕФМгЫйЃЌЮЊгУЛЇМгЬэCable Modem CMЁЂEthernetЕШСщЛюПЩбЁЕФДјПэНгШыЗНЪНвдМАдіМгИпМЖ2DФЫжС3DИпМЖЭМаЮДІРэЃЌБуГЩЮЊЛњЖЅКагІгУЕФвЛИіживЊЗНУцЁЃ ЁЁЁЁЛљгкST40GX1гыSTi5514ЕФЫЋCPUЗНАИ ЁЁЁЁЮЊНтОіЩЯУцЬсГіЕФЮЪЬтЃЌЩшМЦЪБПЩбЁдёSTЙЋЫОЭЦГіЕФЛљгкSTi5514ЕЅаОЦЌНтТыЦїКЭST40GX1ЖўЮЌЭМаЮДІРэЦїЕФЫЋДІРэЦїНтОіЗНАИЃЌИУЗНАИБмУтСЫЭтЩшФЃПщБЖдіДјРДЕФзмЯпгЕМЗвдМАНтТыЪЕЪБадвЊЧѓДјРДЕФЕШД§бгГйЁЃSTi5541КЭST40GX1ФкВПЖМВЩгУИпЫйЯШНјЕФSTBusРДЪЕЯжЛЅСЊЃЌЧАепИКд№ЪЕЪБадвЊЧѓНЯИпЕФгВМўНтИДгУЁЂЪгЦЕвєЦЕНтТыЁЂгыНтТыЯрЙиСЊЕФЭтЮЇI/OЩшБИПижЦЕШЁЃКѓепИКд№ПэДјНЛЛЅЪНгІгУвдМАИпМЖЭМаЮДІРэЃЌСНепжЎМфЕФИпЫйЪ§ОнЭЈаХЭЈЙ§MPX(Memory Periheral Exchange)змЯпвдМАДцДЂгГЩфЕФгЪЯф(Mailbox)РДНјааЃЌЭЈЙ§жїЦЕДя100MКезШЕФMPXзмЯпЃЌSTi5514ФмжБНгДцШЁST40GX1ЩЯПЩИпДя256MBЕФDDR SDRAMДцДЂзЪдДЁЃ ЁЁЁЁЁѓ STi5514ЕФЙІФмЬиЕуМАНгПк ЁЁЁЁSTi5514жївЊгУгкЭъГЩMPEG-2ЪгЦЕЁЂвєЦЕаХКХЕФНтбЙЫѕЁЃЦфФкВПМЏГЩСЫвЛИіMP@MLБъзМЧхЮњЖШЕФЪгЦЕНтТыФЃПщКЭвЛИіЖХБШAC-3/AAC/DTSвєЦЕНтТыФЃПщвдМАVideo EncoderКЭAudio DACФЃПщЕШЁЃФкВП32ЮЛRISC CPUЙЄзїжїЦЕЮЊ120MКезШдкЭтНгV.90ЕФгВМўModemЬѕМўЯТЃЌПЩвдЭЈЙ§ЕчЛАЯпНјааеДјНЛЛЅЪНгІгУЃЌШчНјааЛљгкЕчЛАЯпЛиДЋЕФЪгЦЕЕуВЅЁЂЕЭЫйInternetфЏРРЕШЁЃ ЁЁЁЁгыSTЙЋЫОдчЦкЭЦГіЕФЕЅаОЦЌНтТыЦїSTi5512ЯрБШЃЌГ§вЛАуЙІФмНгПкЯрЭЌЭтЃЌЦфЭЛГіЬиЕуЪЧЃКжИСюКЭЪ§ОнЛКГхЖМдіМгСЫвЛБЖЃЌЭЌЪБВЂЗЂДІРэШ§ТЗTS(Transport Stream)СїЪфШыЁЂжЇГжЖржжНтШХФЃЪН(АќРЈDVBЁЂDESЁЂICMЁЂFast-I)ЃЌжБНгжЇГжЖХБШAC-3/AAC/DTSвєЦЕНтТыЃЌЬсЙЉATAPIгВХЬЕчТЗНгПкЃЌВЂжБНгжЇГжUltra-DMA66ИпЫйЪ§ОнДЋЫЭФЃЪНЕФгВХЬвдЪЕЯжЪ§зжЕчЪгНкФПЕФЪЕЪБТМжЦЃЌЪгЦЕНтТыСїПЩвдвдITU-R601-656ИёЪНЪ§ОнСїЪфГіЛђепвдИДКЯЪгЦЕаХКХCVBSЁЂЗжСПаХКХRGBКЭYUVЕШВЛЭЌФЃФтФЃЪНЪфГіЃЌжЇГжTeletextНтТыЪфГіЃЌЭЌЪБЬсЙЉЖдСНТЗSIMПЈНгПкЁЃРћгкРЉеЙвјааПЈЕШИпМЖгІгУЁЃгЩгкSTi5514ШЅЕєСЫ1394НгПкЃЌЙЪашЭтНг1394ПижЦЦї(ШчSTE422ЕШ)РДРЉеЙЛљгк1394ЕФЪгЦЕЪфШыЁЃ ЁЁЁЁЁѓ ST40GX1ЕФЙІФмНсЙЙ ЁЁЁЁST40GX1ФкВПМЏГЩгаSH-4аЭ32ЮЛRISCДІРэЦїФкКЫЃЌGamma 2DЭМЯѓДІРэЃЌЛьКЯФЃПщвдМАЦфЫћЪгЦЕЕчТЗНгПкТпМЃЌST40GX1ЪЧНЛЛЅЪНгІгУЕФДІРэКЫаФЃЌЫќАќРЈЯЕЭГЩшБИКЭЭтЩшСНИіЗНУцЃК ЁЁЁЁ(1)ЯЕЭГЩшБИ ЁЁЁЁST40GX1ЕФЯЕЭГЩшБИАќРЈжабыДІРэЦї(CPU)ЁЂгУгкDSPЙІФмЕФИЁЕудЫЫуЕЅдЊ/МгГЫДІРэЕЅдЊ(FPU/Mac)ЁЂДцДЂЙмРэЕЅдЊ(MMU)вдМАDMAПижЦФЃПщЁЃЦфжаЃЌCPUЮЊ32ЮЛSuperH RISCЃЌЫќВЩгУ2ЭЈЕРГЌБъСПЬхЯЕНсЙЙЃЌжїЦЕ166MКезШЃЌ16ЮЛжИСюЖЈГЄ(Load-StoreНсЙЙ)ЃЌ8KBжБНгжИСюЛКДцЃЌ16KBжБНгВйзїЪ§ЛКДцЃЌВЂДјгавЛИіЦЌЩЯГЫЗЈЦїЁЃЖјЦфДцДЂЦїдђжЇГж4GBЕФДцДЂПеМфЃЌВЂжЇГжЕЅПщЛђЖрПщащФтФкДцФЃЪНЃЌвГУцЕФДѓаЁПЩвдЪЧ1KBЁЂ4KBЁЂ64KBЛђ1MBЃЌДЫЭтЃЌЫќЛЙжЇГж4ЭЈЕРШЋЯрЙижИСюITLB(Instruction Translation Lookaside Buffer)ЁЂ64ЭЈЕРШЋЯрЙижИСювдМАВйзїЪ§UTLBЃЌЭЌЪБжЇГжШэМўПижЦЕФИќаТЫуЗЈвдМАЫцЛњМЦЪ§ЕФИќаТЫуЗЈЃЌетЮЊ32ЮЛБЃЛЄФЃЪНЯТЕФВйзїЯЕЭГЬсЙЉСЫЭъБИЕФгВМўЦНЬЈЃЌST40GX1жаЕФЭЈгУDMAПижЦЦїПЩжЇГж5ИіЭЈЕРЕФЪ§ОнДЋЪфЃЌЦфжа4ИіЭЈЕРПЩвдгУгкДцДЂЦїЕНДцДЂЦїЛђДцДЂЦїЕНЭтЩшжЎМфЕФЪ§ОнДЋЫЭЃЌСэЭтвЛИіЭЈЕРЮЊДјЛКГхЕФЖрТЗИДКЯЭЈЕРЃЌЭЌЪБжЇГж2DПщЕФАсЖЏвдМАСДБэВйзїЃЌЦЌФкСНИіЭЈЕРЕФDMAЮеЪжаХКХКЭEMIНгПкаХКХЛЙПЩгУгкMPXзмЯпВйзїЁЃ ЁЁЁЁ(2)ЭтЩшНгПкФЃПщ ЁЁЁЁST40GX1ЕФЭтЩшНгПкФЃПщАќРЈЭЈгУНгПкФЃПщКЭЪгЦЕзЈгУНгПкФЃПщЃЌЦфжаЭЈгУНгПкФЃПщАќРЈСНИігыST40ЯЕСаДІРэЦїМцШнЕФШЋЫЋЙЄвьВНДЎааЭЈаХЖЫПкЁЂжаЖЯПижЦЦїЁЂЗћКЯIEEE1149ЙцЗЖЕФЕїжЦПижЦЦїЁЂЪЕЪБЪБжгЁЂ4ИігУЛЇПЩБрГЬЕФPLLЁЂ24ЮЛЪфШыЪфГіЗНЯђПЩХфжУЕФВЂааI/OПкЃЌвдМАСНИіЗћКЯV1.1ЙцЗЖЕФUSBжїПижЦЦїКЭЪеЗЂЦїЁЂModemФЃФтЧАЖЫНгПкMAFEЁЂСНИіПЩХфжУЮЊжЇГжI2CЛђSPIзмЯпНгПкБъзМЕФЭЌВНДЎааПижЦЦї(SSC0КЭSSC1)ЁЂTeletextЪфШыНгПкЁЂСНИіЪЙгУвьВНавщЕФSmartCardНгПкЁЂгУгкКЭЭтВПЮЂПижЦЦїЭЈаХЕФДцДЂгГЩфгЪЯф(Mailbox)ЁЂЗћКЯPCI2.1ЙцЗЖЕФPCIНгПкПижЦЦїЁЂСНТЗвєЦЕPCMЪфШыНгПкКЭвЛТЗPCMЪфГіНгПкЕШ;ЖјЪгЦЕзЈгУНгПкМАДІРэФЃПщдђАќРЈзжЪгЦЕЪфШыЖЫПкКЭ2DЭМЯѓДІРэЦїЃЌетСНИіCCIR601-656ЪгЦЕЪфГіЖЫПк(DVP0ЃЌDVP1)ПЩвдЭЌЪБЪфШыVCbCr4ЃК2ЃК2ИёЪНЕФЪгЦЕЪ§ОнЃЌВЂНЋЦфзАШыОжВПДцДЂЦїЁЃвВПЩЖдУЛгаФкЧЖЭЌВНаХКХЕФЪгЦЕРДИљОнSAV/EAVавщЬсЙЉЭтЭЌВНаХКХжЇГжЃЌгУЛЇПЩвдДгЪфШыЕФЪгЦЕЭМЯёжаЩшЖЈЪгЦЕВЖЛёДАПквдМАЛюЖЏДАПкЕФзгДАПкЁЃЪ§зжБрТыЦф(DENC)НЋЪ§зжЪгЦЕСїзЊЛЛЮЊБъзМЕФФЃФтЛљДјPAL/SECAM/NTSCаХКХвдМАRGBКЭYUVФЃФтЗжСПаХКХЃЌШчЙћдкLMIЩЯЪЙгУ32ЮЛЕФDRAMЃЌдђПЩвдЛёЕУRGB24ЮЛЕФЪ§зжЪгЦЕСїЃЌ2DЭМЯѓДІРэЦї(ЛђЭМЯёПщДЋЫЭв§Чц)гЕгаСНИі2D DMAЭМЯёЪ§ОнЪфШыдДЃЌПЩЭъГЩвЛећЬзЧПДѓЕФДІРэВйзїЃЌГ§ПЩЭъГЩЦеЭЈ2DЭМаЮМгЫйЙІФмЭтЃЌЛЙПЩЭъГЩВЛЭЌЭМаЮИёЪН(RGB/ YUVЕШ)жЎМфЕФзЊЛЛЃЌЦфжаАќРЈПщЬюГфЁЂПщПНБДЁЂвьВНИДКЯЁЂЩЋВЪБфЛЛвдМА2DЫѕЗХДІРэЕШЙІФмЁЃ ЁЁЁЁЛљгкSTi5514КЭST40GX1ЕФЯЕЭГЙЙГЩ ЁЁЁЁИљОнSTi5514КЭST40GX1ЕФЙІФмЬиЕуЃЌЭМ1ИјГіСЫБОЯЕЭГЕФзмЬхНсЙЙЗНАИЁЃ ЁЁЁЁ  ЁЁЁЁЭМ1 ЁЁЁЁЁѓ ЧАЖЫНтТыВПЗж ЁЁЁЁгЩгкSTi5514ФкжУШ§ТЗTSСїНтШХЭЈЕРЃЌЙЪВЩгУЫЋТЗЕФTurner+STV0297QAMНтЕїЦїЭЌЪБНтЕїСНИіЦЕЕРЕФЛљгкDVB-CЕФЪгЦЕЪ§ОнДЋЪфСїЃЌГфЗжРћгУSTi5514ЕФгВМўНтШХЁЂПижЦДІРэвдМАНтТыФмСІЃЌПЩвдЪЕЯжЛжаЛЙІФмЃЌЦфжаTurnerПЩвдВЩгУMicroTuneЕФMT2040ЕЅаОЦЌЕїаГЦївдНкЪЁПеМфКЭГЩБОЃЌДЫЭтЃЌЭЈЙ§ЭтНгSTE422ЃЌЖдIEEE1394НгПкЪфШыЬсЙЉжЇГжЁЃ ЁЁЁЁЁѓ КѓЖЫНтТыВПЗж ЁЁЁЁКѓЖЫНтТыгЩSTi5541ЭъГЩЃЌSTi5514ЭЈЙ§ЭтНг8MBЙВЯэЕФSDRAMЭъГЩдкаХЕРНтЕїЁЂНтИДгУвдМАНтТыЙ§ГЬжаЫљашвЊЕФДцДЂзЪдДЃЌSTi5514ЭЈЙ§MPXзмЯпЙВЯэЮЛгкST40GX1 EMIНгПкЩЯЕФ16MB FLASHЃЌЭЈЙ§ATAНгПкЭтНггВХЬДцДЂЦївдРЉеЙVCRгІгУЁЃSTi5514НтТыКѓЕФЗћКЯITU-R601_656БъзМЕФЪгЦЕЪ§ОнЭЈЙ§ЪгЦЕЪфГіЖЫПкжБНгЪфШыЕНST40GX1ЕФСНТЗЪгЦЕЪфШыЖЫПкжаЕФDVP0ЁЃSTi5514ЯђST40GX1ЗЂЫЭ27MКезШЕФЯёЫиЪБжгвдМАЭЌВНаХКХЃЌвдШЗБЃSTi5514ЪгЦЕЪ§Оне§ШЗНгЪеЁЃ ЁЁЁЁЁѓ ЭМаЮДІРэ ЁЁЁЁЕБгУST40GX1ДІРэЖўЮЌЭМаЮЪБЃЌПЩЯШгУST40GX1РДНгЪеРДздSTi5514ЕФНтТыЪгЦЕСїЃЌВЂОЙ§ВхжЕЁЂЩЋВЪПеМфзјБъБфЛЛКѓЃЌгыЭјвГфЏРРЕШЦфЫћЪгЦЕНјааЭИУїЖШДІРэ(Alpha blending)ЁЂБЅКЭЖШДІРэ(Gamma Processing)ЕШИДКЯДІРэЃЌДгЖјаЮГЩЭГвЛЕФЪгЦЕжЁЛКДцЪ§ОнЃЌдкЭЈЙ§ФкВПЕФDENCНЋЦфБрТыЮЊФЃФтЕчЪгФмНгЪеДІРэЕФИДКЯЪгЦЕаХКХCVBSЁЂSVideoЛђЗжСПаХКХRGBЁЂYUVЕШЪфГіЁЃ ЁЁЁЁгЩгкST40GX1жЛжЇГж3.3VЕФPCIНгПкЃЌЙЪПЩЭЈЙ§IntelЕФSB21150BCРДРЉеЙ3.3VЛђ5VЕФPCIВхВл;дкашвЊ3DЭМЯѓДІРэЕФЧщПіЯТЃЌвВПЩвдЭЈЙ§ЭтВхPCI 3DЭМаЮМгЫйПЈРДЪЕЯжЁЃ ЁЁЁЁЁѓ НЛЛЅЪНгІгУЕФЭјТчНгПк ЁЁЁЁНЛЛЅЪНгІгУЕФгВМўВПЗжПЩгЩST40GX1вдМАЯргІЕФЭјТчНгПкЭъГЩЁЃПМТЧЕНЭјТчНгПкЕФДјПэНгШыЗНЪНвЊЧѓЃЌЩшМЦЪБПЩРћгУST40GX1ЖдЭтВПЬсЙЉЕФPCIзмЯпНгПкЃЌВЂМЏГЩCable ModemЁЂEthernetЕШИпЫйНгПкЁЃ ЁЁЁЁ(1)Cable Modem ЁЁЁЁЪзЯШбЁдёЗћКЯDocsis1.1/Euro-docsis1.1ЙцЗЖЕФCable ModemЧАЖЫЕЅаОЦЌНгПкаОЦЌ STV0396зїЮЊCable ModemНтОіЗНАИЃЌетвЛВПЗжМШПЩвдзїЮЊвЛИіЖРСЂЕФPCIПЈРДЩшМЦЃЌвВПЩвдНЋЦфжБНгЧЖШыФИАхЩЯЃЌSTV0396ЪЧвЛИіИпЖШМЏГЩЕФЕїжЦНтЕїЯЕЭГЃЌАќРЈжЇГжЩЯааКЭЯТааЗћКЯDOCSIS1.1ЙцЗЖЕФЮяРэВуЙцЗЖНгПкЃЌУНЬхНгШыПижЦ(MAC)вдМАЙІФмЧПДѓЕФ32ЮЛST20 RISCДІРэЦїЁЂPCIЁЂEMI/MPXЕШгыST40GX1ЯрМцШнЕФЭтВПНгПкЁЃSTV0396ВЩгУ316ЙмНХЕФGBAЗтзАЃЌГ§ашЭтНгЫЋЯђЕїаГЦїЭтЃЌЛЙашвЊЬэМгЯТааЗНЯђЕФЩљБэУцВЈТЫВЈЦї(SAWЁЂЩЯааЗНЯђЕФЯпТЗЗХДѓЦївдМАЪБжгЕШЃЌВХФмЪЕЯжгыЯпРТЭЗЖЫЩшБИCMTSжЎМфЕФЭЈаХСЌНгЃЌЦфЕфаЭНгПкЕчТЗШчЭМ2ЫљЪОЁЃ ЁЁЁЁ  ЁЁЁЁ(2)вдЬЋЭјНгПк ЁЁЁЁПЩбЁдёЛљгкRTL8139CЕФ3.3VвдЬЋЭјаОЦЌзщзїЮЊНгПкаОЦЌЃЌетЪЧвђЮЊаОЦЌОпгаИпЖШМЏГЩЁЂдкЧЖШыЪНЯЕЭГжаЪЙгУЙуЗКвдМА10/100MздЪЪгІЬиадЁЂздДјPCIНгПкЁЂдкРрLinuxВйзїЯЕЭГЯТЧ§ЖЏГЬађШнвзевЕНЕШгХЕуЁЃRTL8139ВЩгУ128ЙмНХЕФQPF/LQPFЗтзАЃЌПЩЭЈЙ§PCIзмЯпНгПкгыST40GX1ЯрСЌЁЃ ЁЁЁЁ(3)V.90ШэМўModemЕФжЇГж ЁЁЁЁЖдгкV.90ШэМўModemЕФжЇГжЃЌПЩжБНгРћгУST40GX1ЕФModemЧАЖЫНгПкMAFEРДЭъГЩЁЃВЛЪЙгУгВМўModemПЩвдГфЗжРћгУST40GX1ЕФдЫЫуДІРэФмСІРДНЕЕЭГЩБОЁЃ ЁЁЁЁЯЕЭГЕФЦєЖЏМАЭЈбЖ ЁЁЁЁST40GX1гыSTi5514ЭЈЙ§ХфжУИїздMPXзмЯпНгПкЕФжї/Дг(Initiator/target)ЗНЪНРДОіЖЈЯЕЭГЕФЦєЖЏЫГађЁЃдкетРяЃЌгЩгкЯЕЭГЦєЖЏДњТыЮЛгкST40GX1ОжВПFLASHжаЃЌЙЪНЋST40GX1ХфжУЮЊжї(Initiator)НЋSTi5514ХфжУЮЊДг(target)ЁЃОпЬхЕФЦєЖЏЫГађЮЊЃКST40GX1ЪзЯШПижЦMPXзмЯпВЂЧвЯШЦєЖЏЃЌдкЦєЖЏЦкМфзшжЙSTi5514ЪЙгУMPXзмЯпЃЌжБЕНЦфЭъШЋЭъГЩДгFlashРяУцЖСШЁЦєЖЏДњТыКЭГѕЪМЛЏЮЊжЙЁЃНгзХST40GX1РћгУMPXзмЯпПНБДSTi5514ЕФЦєЖЏГЬађвдМАгІгУГЬађДњТыЕНздМКЕФLMI DDRФкДцжаЃЌПНБДЭъГЩКѓЃЌST40GX1ЪЭЗХВЂдЪаэSTi5514ПижЦMPXзмЯпЃЌSTi5514ДгST40GX1ЕФDDR SDRAMжаПНБДздМКЕФЦєЖЏГЬађМАгІгУГЬађДњТыЃЌНшМјетвЛЕуЃЌЭЈЙ§MPXзмЯпПЩвдЪЕЯжЖрCPUжЎМфЕФДцДЂЙВЯэЁЃ ЁЁЁЁSTi5514ЭЈЙ§MPXзмЯпПЩвдЗУЮЪST40GX1ЩЯЕФMailboxМФДцЦїЁЃMailboxБЛЙЬЖЈгГЩфгкST40GX1ДцДЂПеМфЕФЛљЕижЗ0x1B150000ДІЃЌИУМФДцЦїЖдСНИіCPUЖМФмВњЩњжаЖЯаХКХЁЃЭЈЙ§MaliboxМФДцЦїЃЌST40GX1гыSTi5514ФмЪЕЯжНјГЬЭЌВНЁЂЯћЯЂДЋЕнЕШНјГЬМфЭЈаХЁЃ |

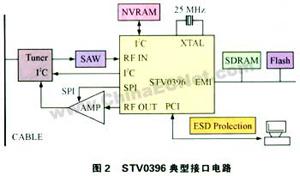

ЭјгбЦРТл