TIP41CΒΆΤΒ¥σΙΠ¬ ΤΫΟφΨßΧεΙή–ΨΤ§…ηΦΤ

ΖΔ≤Φ ±ΦδΘΚ2010-7-20 23:31

ΖΔ≤Φ’ΏΘΚconniede

|

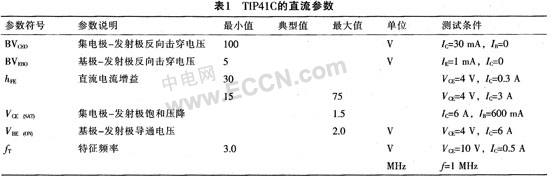

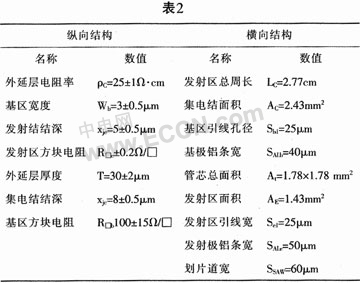

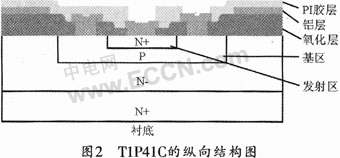

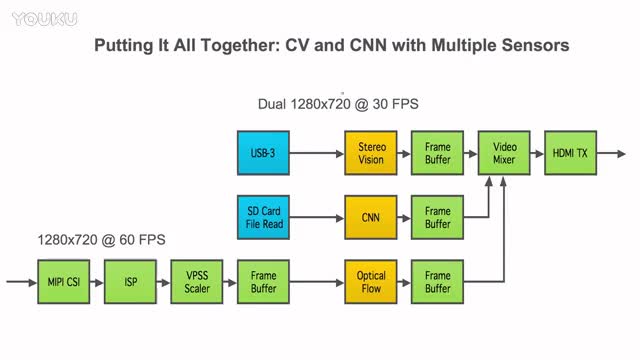

“ΐ―‘ TIP41C «“Μ÷÷÷–―ΙΒΆΤΒ¥σΙΠ¬ œΏ–‘ΩΣΙΊΨßΧεΙήΓΘΗΟΤςΦΰ…ηΦΤΒΡ÷ΊΒψ «ΥϋΒΡΦΪœό≤Έ ΐΓΘ…ηΦΤΖ¥―ΙΫœΗΏΒΡ¥σΙΠ¬ ΨßΧεΙή ±Θ§ Ήœ» «»γΚΈΧαΗΏΨßΧεΙήΒΡΖ¥―ΙΘ§ΫΒΒΆΦ·Βγ«χ‘”÷ ≈®Ε»NCΓΘΒΪ”…”ΎΒγΉη¬ Π―CΒΡ‘ω¥σΘ§Φ·Βγ«χΧεΒγΉη…œΒΡΒγ―ΙΫΒΜα‘ω¥σΘ§¥”Εχ Ι±ΞΚΆ―ΙΫΒ‘ω¥σΒΫ≤Μ‘ –μΒΡ≥ΧΕ»ΓΘΕχΦθ–ΓNC”÷Μα ΙΩ’ΦδΒγΚ…œό÷Τ–ß”ΠΖΔ…ζΘ§¥”Εχ‘λ≥…¥σΒγΝςΠ¬ΒΡΦ±Ψγœ¬ΫΒΓΘΈΣΫβΨω…œ ωΟ§ΕήΘ§…ηΦΤ ±“ΜΑψ≤…”ΟΆβ―”ΫαΙΙΓΘ ¬ Β…œΘ§TIP41CΒΆΤΒ¥σΙΠ¬ ΤΫΟφΨßΧεΙή‘Ύ…ηΦΤ…œ”Π≤…”Ο…νά©…ΔΓΔΚώΜυ«χΓΔ¥σΟφΜΐΩμΒγΦΪΒ»ΫαΙΙΘ§Ιή–ΨΒΡΉίœρ≥Ώ¥γ”Π±»ΫœΚώΘ§Καœρ≥Ώ¥γ”Π±»ΫœΩμΓΘΩΊ÷ΤΙή–ΨΟφΜΐ‘Ύ2ΓΝ2 mm2Ήσ”“ ±Θ§Ω…≤…”ΟΗ≤Η« ΫΫαΙΙ…ηΦΤΙβΩΧΑφΆΦΘ§’β―υΨΆΡήΨΓΩ…Ρή‘ωΦ”ΖΔ…δ«χ÷ή≥ΛΘ§¬ζΉψΒγΝς“Σ«σΘ§“≤Ρή ΙΒγΝςΖ÷≤ΦΗϋΨυ‘»ΓΘΈΣ¥ΥΘ§±ΨΈΡΗχ≥ωΝΥ“Μ÷÷ΩΣΖΔT1P41Θ·2CΒΆΤΒ¥σΙΠ¬ ΤΫΟφΨßΧεΙήΒΡ…ηΦΤΖΫΖ®ΓΘ 1 TIP41C–ΨΤ§ΒΡ≤Έ ΐ“Σ«σ TIP41CΨßΧεΙήΦΪœό≤Έ ΐ“Σ«σ»γœ¬ΘΚ PCΘΚΦ·ΒγΦΪΙΠ¬ ΚΡ…Δ(Tc=25Γφ)ΈΣ65 W BVCEOΘΚΦ·ΒγΦΪ-ΖΔ…δΦΪΒγ―ΙΈΣ100 V BVEBOΘΚΖΔ…δΦΪ-ΜυΦΪΒγ―ΙΈΣ5 V IC:Φ·ΒγΦΪΒγΝςΈΣ6A TlP41CΒΡ÷±ΝςΒγ≤Έ ΐ»γ±μ1ΥυΝ–ΓΘ 2 TIP41CΒΡ…ηΦΤΦΤΥψ Ε‘”Ύ“‘…œ…ηΦΤ“Σ«σΘ§Ω…Ά®Ιΐάμ¬έΦΤΥψά¥»ΖΕ®TIP41CΨßΧεΙήΗς≤ΩΖ÷ΒΡ‘”÷ ≈®Ε»ΦΑΫαΙΙ≥Ώ¥γΓΘ 2.1 Φ·ΒγΫαΒΡΫα…νΚΆΆβ―”≤ψΒγΉη¬ ΒΡ»ΖΕ® »τ―Γ»ΓΦ·ΒγΫαΫα…νxjcΒ»”Ύ8ΠΧmΘ§Ρ«Ο¥Θ§ΗυΨίBVCEOΓί100 VΘ§«“ 2.2 Μυ«χΩμΕ»WbΚΆΖΔ…δΫαΫα…νxjeΒΡ»ΖΕ® ΒΆΤΒ¥σΙΠ¬ ΨßΧεΙήΒΡWbΓΔxje÷ς“ΣΗυΨίΜς¥©Βγ―ΙΚΆΑ≤»ΪΙΛΉςΒΡ–η“Σά¥―ΓΕ®ΓΘΆΦ1 «Φ·ΒγΫαΗΫΫϋΒΡ‘”÷ Ζ÷≤ΦΚΆ Τάί«ιΩωΘ§Τδ÷–x1ΚΆx2Ζ÷±π «Φ·ΒγΫα‘ΎΜυ«χ≤ΩΖ÷ΚΆΦ·Βγ«χ≤ΩΖ÷ΒΡ ΤάίΩμΕ»Θ§ΥϋΟ«ΒΡΉή ΤάίΩμΕ» «ΠΡ=x1+x2ΓΘ’β―υΘ§‘ΎNCΈΣ2ΓΝ1014cm-3ΓΔNSBΈΣ1018 cm-3ΓΔVΈΣ280 VΒΡΧθΦΰœ¬Θ§≤ι±μΩ…ΒΟΠΡ=35ΠΧmΘ§x1Θ·ΠΡ=0.07Θ§¥Υ ±x1ΈΣ2.45ΠΧmΓΘ  ΈΣΝΥ±Θ÷ΛΜς¥©Βγ―ΙΒΡ“Σ«σΘ§”ΠΨΓΩ…ΡήΒΡΧαΗΏΕΰ¥ΈΜς¥©ΡΆ―ΙΝΩΘ§ΨßΧεΙήΒΡΜυ«χΩμΕ»”Π¥σ”Ύ2.45ΠΧmΘ§ΒΪ”÷≤ΜΡήΧΪ¥σΘ§Ζώ‘ρΜυ«χ δ‘ΥœΒ ΐΠ«ΜαΦθ–ΓΓΘ¥”Εχ ΙΒγΝςΖ≈¥σœΒ ΐΦθ–ΓΘ§“ρ¥Υ”Π―Γ‘ώΜυ«χΩμΕ»Wb=3ΠΧmΓΘ”…”ΎΦ·ΒγΫαΫα…νxjc=Wb+xje=8ΠΧmΘ§“ρ¥ΥΘ§“ΜΑψά¥ΥΒΘ§ΖΔ…δΫαxje”ΠΒ»”ΎΜυ«χΩμΕ»ΒΡ1.0ΓΪ2.5±ΕΓΘΉέΚœ“‘…œΩΦ¬«Θ§Ω…»ΖΕ®Μυ«χΩμΕ»WbΈΣ3ΠΧmΘ§ΖΔ…δΫαΫα…νxjeΈΣ5ΠΧmΓΘ 2.3 Άβ―”≤ψΚώΕ»TΒΡ»ΖΕ® Άβ―”≤ψΚώΕ»T÷Ν…Ό”ΠΒ»”ΎΦ·Βγ«χΚώΕ»WCΓΔΦ·ΒγΫαΫα…νxjeΓΔΖ¥ά©…Δ≤ψ»ΐ≤ΩΖ÷÷°ΚΆΓΘΈΣΝΥΡή¥οΒΫBVCBO÷Η±ξΘ§Φ·Βγ«χΗΏΉη≤ψΚώΕ»WC”Π¥σ”ΎΈΣΦ·ΒγΫα―©±άΜς¥© ±Ε‘”ΠΒΡΩ’ΦδΒγΚ…ΩμΕ»XmBΓΘ ¥”ΗΡ…Τ―©±άΉΔ»κΕΰ¥ΈΜς¥©ΒΡΫ«Ε»ΩΦ¬«Θ§œΘΆϊΦ·Βγ«χΚώΕ»WCΓίBVCBOΘ·EMΘ§Τδ÷–EMΈΣΉν¥σΒγ≥Γ«ΩΕ»ΓΘ Ρœ”ΎTIP41CΨßΧεΙήΒΡBVCBO“Σ«σΈΣ280 VΘ§“ρ¥ΥΘ§Ε‘”ΎΒγΉη¬ Π―cΈΣ25 ΠΗΓΛcmΒΡΙηΨßΧεΙήΘ§Φ·Βγ«χΚώΕ»WCΓ÷20ΠΧmΓΘΦΌ…η Ι”Ο≤τAs≥ΡΒΉ≤ΡΝœΘ§Ζ¥ά©…Δ≤ψΚώΈΣ2ΠΧmΘ§‘ρΆβ―”≤ψΚώΕ»T”ΠΒ»”Ύ30ΠΧmΓΘΥυ“‘Θ§Ω…»Γ≤ΡΝœΆβ―”≤ψΚώΕ»ΈΣ30+2ΠΧmΓΘ  2.4 Μυ«χ≈πά©…Δ≈®Ε»ΒΡ»ΖΕ® ΈΣΗΡ…ΤΨßΧεΙήΒΡ¥σΒγΝςΧΊ–‘Θ§Μυ«χ≈πά©…Δ≈®Ε»”ΠΗΏ“Μ–©Θ§ΒΪΜυ«χ‘”÷ ≈®Ε»ΧΪΗΏ”÷ΜαΫΒΒΆBVEBOΘ§Υυ“‘Θ§”Π‘Ύ±Θ÷ΛBYEBOΓί5 VΒΡ«ΑΧαœ¬ΨΓΝΩΧαΗΏΜυ«χ≈®Ε»ΓΘΜυ«χ‘”÷ ≥ΝΜΐΩ…≤…”ΟάκΉ”ΉΔ»ΥΙΛ“’Θ§Β±Μυ«χ‘ΌΖ÷≤ΦΚσΘ§Ω…»œΈΣΜυ«χ ή÷ς‘”÷ ΒΡ‘ΌΖ÷≤Φ «ΗΏΥΙΚ· ΐΖ÷≤ΦΓΘ»τ ‘”Ο±μΟφ≈®Ε»NSBΒ»”Ύ1018cm-3ά¥Ζ÷ΈωΘ§‘ρΘΚ Ϋ÷–ΘΚN(xΘ§t)ΈΣΙηΤ§÷–»Έ“β“ΜΒψx¥ΠΒΡ‘”÷ ≈®Ε»ΘΚ “ρ¥Υ”–ΘΚ ’β―υΘ§”–ΘΚ ≤ιΗΏΥΙΚ· ΐ±μΒΟΘΚ Εχ‘ΎΖΔ…δΫαxjeΈΣ5ΠΧm¥Π”–ΘΚ ‘Ό≤ιΗΏΥΙΚ· ΐ±μΒΟΘΚ Φ¥”–ΘΚ ”…¥ΥΖΔ…δΫα¥Π÷ ≈®Ε»Ω…≤ι±μΒΟ ΩΦ¬«ΒΫ±Ώ‘ΒΜς¥©Θ§Μς¥©Βγ―Ι”–“ΜΕ®ΒΡœ¬ΫΒΘ§ΒΪ“≤Ρή¬ζΉψBVEBOΓί5 VΓΘΕχ”ΟNC=2ΓΝ1014cm-3NSB=1018cm-3Θ§xje=8ΠΧm±ψΩ…≤ι«ζœΏΒΟ≥ωΜυ«χΒΡΖΫΩιΒγΉηRΓθbΈΣ100 ΠΗΘ·ΩΎΓΘ 2.5 ΖΔ…δ«χΝΉά©…Δ≈®Ε»ΒΡ»ΖΕ® ΈΣΝΥ±Θ÷Λ”–ΉψΙΜΒΡΖ≈¥σœΒ ΐΘ§“Σ«σΖΔ…δ«χΒΡΝΉά©…Δ±μΟφ≈®Ε»‘ΦΈΣ1021cm-3ΓΘ’β‘Ύxje=5ΠΧmΘ§NSB=1018cm-3ΒΡΧθΦΰœ¬Θ§Ω…≤ι«ζœΏΙάΥψ≥ωΖΔ…δ«χΖΫΩιΒγΉηRΓθeΈΣ1 ΠΗΘ·ΩΎΘ§ΒΪ‘Ύ ΒΦ ΙΛΉς÷–Θ§“ΜΑψRΓθe“‘¬ζΉψΖ≈¥σœΒ ΐhEEΈΣ«ΑΧαΓΘ“ρ¥ΥΘ§ΈΣΝΥ±Θ÷ΛTIP41CΖΔ…δ«χά©…Δ”–ΉψΙΜΗΏΒΡ‘”÷ ≈®Ε»Θ§ΖΔ…δ«χά©…Δ≤…”Ο»ΐ¬»―θΝΉ“ΚΧ§‘¥ΙΛ“’ΓΘ 3 TIP41CΨßΧεΙήΒΡ…ηΦΤ≤Έ ΐ TIP41CΒΡΉίœρΚΆΚαœρΫαΙΙ≤Έ ΐ»γ±μ2ΥυΝ–ΓΘΗΟ–ΨΤ§ΒΡΙΛ“’Νς≥Χ»γœ¬ΘΚ  N–ΆΆβ―”Τ§Γζ“Μ¥Έ―θΜ·Γζ“Μ¥ΈΙβΩΧΓζΗ…―θ―θΜ·ΓζBάκΉ”ΉΔ»κΓζ…νΜυ«χά©…ΔΓζΕΰ¥ΈΙβΩΧΓζΝΉ‘ΛΒμΜΐΓζΖΔ…δ«χά©…ΔΓζΧΊ–‘ΙβΩΧΓζΧΊ–‘hFE≤β ‘ΓζPΈϋ‘”(PSG)ΓζPLTO(ΒΆΈ¬―θΜ·)ΓζH2¥ΠάμΓζ»ΐ¥ΈΙβΩΧΓζQCΦλ≤β(hFEΓΔBVCBOΓΔBVCEO)Γζ’τ¬ΝΓζΥΡ¥ΈΙβΩΧΓζ¬ΝΚœΫπΓζQCΦλ≤βVBESATΓζΈε¥ΈΙβΩΧΓζPIΫΚΕέΜ·Γζ÷–≤β≥ιΦλΒγ≤Έ ΐΓζ±≥ΟφΦθ±Γ(220ΠΧm)Γζ’τ“χΓζ÷–≤β≤β ‘Βγ≤Έ ΐΓζ»κΩβ ΆΦ2Υυ Ψ «TIP41CΒΡΉίœρΫαΙΙΆΦΓΘ  ”…”ΎΉς’ΏΥυ‘ΎΒΞΈΜΒΡ…ζ≤ζ≥ΒΦδ…ηΦΤ±»ΫœΦρΒΞΘ§≥ΒΦδΜΖΨ≥ΨΜΜ·≥ΧΕ»≤ΜΗΏΘ§“ρ¥ΥΘ§‘Ύ“Μ¥Έ―θΜ·ΓΔΜυ«χά©…ΔΙΛ“’÷–≤…”ΟTCAΙΛ“’ά¥Ε‘“Μ¥Έ―θΜ·ΓΔΕΰ¥Έ―θΜ·Ιΐ≥Χ÷–Na+ΒΡΈέ»ΨΫχ––”––ßΩΊ÷ΤΘ§ΖΔ…δ«χά©…Δ≤…”ΟP-Έϋ‘”ΙΛ“’ά¥ΩΊ÷Τ»ΐ¥Έ―θΜ·Ιΐ≥Χ÷–Na+ΒΡ≤ζ…ζΘ§±μΟφΕέΜ·‘ρ≤…”ΟPIΫΚΙΛ“’ά¥±Θ÷ΛΆβΫγΜΖΨ≥≤Μ”Αœλ–ΨΤ§±μΟφΘ§Ά§ ±Ϋχ“Μ≤ΫΈϋ ’ΓΔΈ»Ε®―θΜ·≤ψ’ΐΒγ÷––ΡΒΡ“ΤΕ·Θ§¥”Εχ Ι–ΨΤ§ICEO¬©Βγ¥σ¥σΦθ…ΌΘ§ΡΩ«ΑΘ§TIP41CΒΡΒγ≤Έ ΐ¥οΒΫΙζΦ œ»ΫχΥ°ΤΫΓΘ 4 Ϋα χ”ο ¥σΝΩ…ζ≤ζ ΐΨί±μΟςΘ§Έ“ΥΨ…ηΦΤΒΡTIP41CΨßΧεΙή–ΨΤ§…ζ≤ζ≥…±ΨΒΆΘ§–ΨΤ§≥Ώ¥γ1.78ΓΝ1.78 mm2(ΈΣΡΩ«Α –≥ΓΉν–Γ)Θ§…ζ≤ζ‘≠≤ΡΝœΆξ»Ϊ≤…”ΟΙζ≤ζ≤ΡΝœΘ§ΡΩ«ΑΘ§ΗΟ–ΨΤ§ΒΡΙΊΦϋΒγ≤Έ ΐ(¥σΒγΝςΧΊ–‘ΚΆ±ΞΚΆ―ΙΫΒ)“―¥οΒΫΙζΦ œ»ΫχΥ°ΤΫΘ§“ρΕχΨΏ”–ΦΪ«ΩΒΡ –≥ΓΨΚ’υΝΠΓΘ |

Άχ”―Τά¬έ