ЛљгкFPGAЕФViterbiвыТыЦїЩшМЦМАЪЕЯж

ЗЂВМЪБМфЃК2015-11-12 10:17

ЗЂВМепЃКdesignapp

|

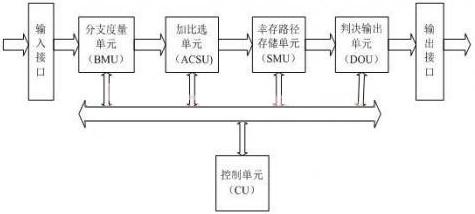

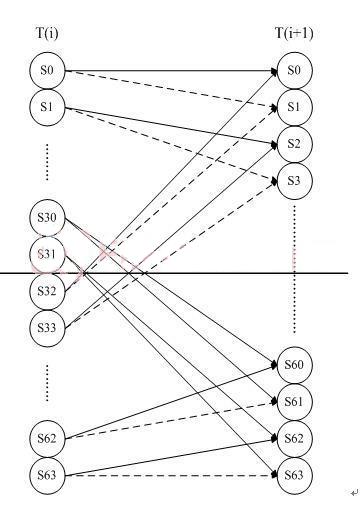

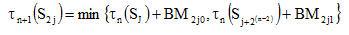

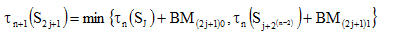

ЁЁЁЁОэЛ§ТыЪЧЙуЗКгІгУгкЮРаЧЭЈаХЁЂЮоЯпЭЈаХЕШИїжжЭЈаХЯЕЭГЕФаХЕРБрТыЗНЪНЁЃViterbiЫуЗЈЪЧвЛжжзюДѓЫЦШЛвыТыЫуЗЈЁЃдкТыЕФдМЪјЖШНЯаЁЪБЃЌЫќБШЦфЫќИХТЪвыТыЫуЗЈаЇТЪИќИпЁЂЫйЖШИќПьЃЌвыТыЦїЕФгВМўНсЙЙБШНЯМђЕЅЁЃЫцзХПЩБрГЬТпМММЪѕЕФВЛЖЯЗЂеЙЃЌЦфИпУмЖШЁЂЕЭЙІКФЁЂЪЙгУСщЛюЁЂЩшМЦПьЫйЁЂГЩБОЕЭСЎЁЂЯжГЁПЩБрГЬКЭЗДИДПЩБрГЬЕШЬиадЃЌЪЙFPGAж№ВНГЩЮЊViterbiвыТыЦїЩшМЦЕФзюМбЗНЗЈЁЃЯюФПФПЕФЪЧгУFPGAЪЕЯжвЛИіViterbiвыТыЦїЁЃ ЁЁЁЁвЛЁЂвыТыЦїЙІФмЗжЮі ЁЁЁЁвыТыЦїЪЧвЛжжОпгаЁАЗвыЁБЙІФмЕФТпМЕчТЗЃЌетжжЕчТЗФмНЋЪфШыЖўНјжЦДњТыЕФИїжжзДЬЌЃЌАДееЦфдвтЗвыГЩЖдгІЕФЪфГіаХКХЁЃViterbiвыТыЦїЪЧвдViterbiЫуЗЈЮЊЛљДЁЩшМЦЕФвЛжжвыТыЦїЃЌвыТыЦїжївЊгЩЮхВПЗжзщГЩЃКЗжжЇЖШСПЕЅдЊ(Branch Metric Unit)ЁЂМгБШбЁЕЅдЊ(Add-Compare-Select Unit)ЁЂавДцТЗОЖЙмРэЕЅдЊ(Survivor Management Unit)ЁЂХаЪфГіЕЅдЊ(Decide-Output Unit)КЭПижЦЕЅдЊ(Control Unit)ЁЃЦфећЬхНсЙЙШчЭМ1ЁЃ ЁЁЁЁ  ЁЁЁЁЭМ1 выТыЦїНсЙЙПђЭМ ЁЁЁЁИїЕЅдЊжЎМфЕФЯрЛЅЙиЯЕШчЯТЃКНгЪеЕНЕФЪфШыЪ§ОнЪзЯШБЛЫЭШыИїЗжжЇЖШСПЕЅдЊжаМЦЫуГіЯргІЕФЗжжЇТЗОЖОрРы;МгБШбЁЕЅдЊНЋОЩЕФзДЬЌТЗОЖЖШСПгыЯргІЕФаТВњЩњЕФЗжжЇТЗОЖОрРыЯрМгЃЌЭЈЙ§БШНЯКѓбЁдёЕНДяЭЌвЛзДЬЌЕФСНИіТЗОЖЖШСПжЕжаНЯаЁЕФЗжжЇРДИќаТТЗОЖЖШСП;вчГіДІРэЗРжЙМгБШбЁЕЅдЊжаЕФТЗОЖЖШСПРлМгжЕЗЂЩњвчГі;авДцТЗОЖЙмРэЕЅдЊНЋМгБШбЁЕЅдЊЩњГЩЕФТЗОЖаХЯЂНјааДцДЂЙмРэ;ХаОіЪфГіЕЅдЊИљОнМгБШбЁЕЅдЊбЁдёЕФТЗОЖЖШСПЃЌДгжабЁдёвЛИізюаЁжЕЃЌВЂЪфГіИУзюаЁжЕЖдгІЕФавДцТЗОЖЁЃЫљгаетаЉЕЅдЊЖМдкПижЦЕЅдЊЕФаЕїЯТЙЄзїЁЃ ЁЁЁЁ1 ЗжжЇЖШСПЕЅдЊ ЁЁЁЁЗжжЇЖШСПБэеїИУЗжжЇНгЪеЕНЕФТыдЊгыЦкЭћТыдЊжЎМфЕФВюБ№ЁЃЖдгкгВХаОіЃЌетжжВюБ№жИВЛЭЌТыдЊЕФИіЪ§ЁЃгВХаОіЗжжЇЖШСПжЕПЩвдБэЪОЮЊЃК ЁЁЁЁ  ЁЁЁЁ(ЪН1) ЁЁЁЁЦфжаЃЌyЮЊНгЪеТызжЃЌcЮЊБОЕиОэЛ§ТыЪфГіТызжЁЃЖдгкТыТЪЮЊ1/2гВХаОівыТыЗНЪНЃЌБрТыЦїЪфГіаХКХПЩФмЮЊ00ЁЂ01ЁЂ10ЁЂ11ЃЌЦфТЗОЖЖШСПШЁжЕ(ККУїОрРы)жЛга0ЁЂ1ЁЂ2Ш§жжПЩФмЃЌвђДЫашвЊгУвЛИі2bitЕФМФДцЦїРДДцДЂЗжжЇЖШСПжЕЁЃ ЁЁЁЁдкБОЮФжаЃЌВЩгУСЫ4ИіACSЕЅдЊ(УПИіACSЕЅдЊгаСНИіРлМгЦї)ВЂааМЦЫуЃЌвђДЫашвЊ8ИіЗжжЇЖШСПЕЅдЊВЂааМЦЫу8ИіЬѕжЇТЗЕФЖШСПжЕЃЌВЂНЋЖШСПжЕЫЭжСACSжаЕФРлМгЦїЁЃ ЁЁЁЁ2 МгБШбЁЕЅдЊ ЁЁЁЁACSЕЅдЊгУРДРлМгТЗОЖЖШСПжЕВЂБШНЯКЭбЁдёНјШыФГвЛзДЬЌЕФСНЬѕЗжжЇЁЃБОЮФжаВЩгУ4ИіACSЕЅдЊВЂааМЦЫуЃЌУП16ИізДЬЌИДгУвЛИіACSНсЙЙЃЌЭЌЪБМцЙЫСЫУцЛ§КЭЫйЖШЁЃ ЁЁЁЁ  ЁЁЁЁЭМ 2 (2,1,7)ОэЛ§ТыЕФзДЬЌЭМ ЁЁЁЁвыТыЦїЕФКЫаФВПЗжЪЧACSЕЅдЊЃЌДЋЭГЕФвыТыЦїНсЙЙУПВњЩњвЛЮЛвыТыашвЊНјаа2(n-1)ДЮМгБШбЁдЫЫуЃЌМД2ЁС2(n-1)=2nДЮМгЗЈдЫЫуКЭ2(n-1)ДЮБШНЯбЁдёдЫЫуЁЃЖдгк(2,1,7)ОэЛ§ТыРДЫЕЃЌашвЊНјаа128МгЗЈдЫЫуКЭ64ДЮБШНЯбЁдёдЫЫуЃЌетНЋеМгУКмЖрЕФзЪдДВЂВњЩњКмДѓЕФЙІКФЃЌвђДЫЃЌШчЙћФмЙЛЭЈЙ§ИФНјACSЕЅдЊЕФНсЙЙРДНЕЕЭЦфЙцФЃКЭЙІКФЃЌНЋЛсЪЙећИівыТыЦїЕФгВМўЙцФЃКЭЙІКФДѓДѓНЕЕЭЁЃ ЁЁЁЁДгЭМ2ЫљЪОЕФ(2,1,7)ОэЛ§ТыЕФзДЬЌЭМжаПЩвдПДГіЃКдкT(i+1)ЪБПЬЕНДязДЬЌS0КЭS1ЕФЪЧT(i)ЪБПЬЕФзДЬЌS0КЭS32ЃЌЁЁЃЌдкT(i+1)ЪБПЬЕНДязДЬЌS62КЭS63ЕФЪЧT(i)ЪБПЬЕФзДЬЌS31КЭS63ЁЃвВОЭЪЧЫЕЃЌT(i)ЪБПЬЕФзДЬЌSjКЭSj+32ЛсДяЕНT(i+1)ЪБПЬЕФЯрСкЕФСНИізДЬЌЃЌВЂЧветСНИізДЬЌЪЧS2jКЭS2j+1(31ЁнjЁн0)ЁЃетвВОЭЪЧЭМаЮЕЅ(ButterfllyUnit)ЁЃ ЁЁЁЁ  ЁЁЁЁЭМ3 ЛљЖўЕћаЮЕЅдЊ ЁЁЁЁдкЭМ3жаЃЌT(i)ЪБПЬЕФзДЬЌSjКЭSj+32ЖМЪЧдкЪфШы0ЕФЪБКђзЊвЦЕНT(i+1)ЪБПЬЕФзДЬЌS2jЃЌдкЪфШы1ЕФЪБКђзЊвЦЕНT(i+1)ЪБПЬЕФзДЬЌS2j+1ЁЃетвВОЭвтЮЖзХACSЕЅдЊжаЕФБШНЯЦїЫљБШНЯЕФСНИіТЗОЖЖШСПжЕ(BM)РДздЪ§жЕЩЯЯрВю32ЕФСНИізДЬЌЁЃТЗОЖЖШСПЕФМЦЫуОЭЪЧЗжжЇЖШСПМгЩЯгыетЬѕЗжжЇЯрСЌЕФЧАвЛЪБПЬЕФзДЬЌбЁдёЕФТЗОЖЖШСПЃЌЫљвдЃЌаТзДЬЌЕФТЗОЖЖШСПЮЊЃК ЁЁЁЁ  ЁЁЁЁ(ЪН2) ЁЁЁЁ  ЁЁЁЁ(ЪН3) ЁЁЁЁДгвдЩЯЕФЗжЮіжаЮвУЧПЩвдЕУГівЛИіКмживЊЕФНсТлЃКДгT(i)ЪБПЬЕФзДЬЌSj(2(n-1)ЁнjЁн0)ЩњГЩЕФСНЬѕжЇТЗЃЌЮЈвЛВЛЭЌЕФаХЯЂОЭЪЧИУЪБПЬзДЬЌSjЕФЪфШыЪ§ОнЃЌSjЕФЩЯжЇТЗЪфШыЕФЪЧ0ЃЌЯТжЇТЗЪфШыЕФЪЧ1ЁЃвђДЫЃЌвЛИізДЬЌПЩвджЛЩњГЩвЛЬѕжЇТЗ(ЩЯжЇТЗ)ЃЌСэвЛЬѕжЇТЗ(ЯТжЇТЗ)ЕФаХЯЂвбОАќРЈдкетЬѕжЇТЗжаЃЌвЊЛжИДГіЯТжЇТЗжЛашвЊНЋЩЯжЇТЗЕФЪфШыЪ§ОнШЁЗДМДПЩЁЃЭМ4.2ЫљЪОЕФACSЕЅдЊНсЙЙжаЕФРлМгЦїПЩвдМѕЩйвЛАыЕФЙЄзїСПЃЌЖдгкБОЮФжаЕФ(2,1,7)ОэЛ§ТыЕФвыТыЦїЃЌМДгЩУПВњЩњвЛЮЛвыТыЙЄзї16ИіЪБжгжмЦкМѕЩйЮЊ8ИіЪБжгжмЦк(ПЩНЋЪБжгЦЕТЪНЕЮЊдРДЕФ1/2)ЃЌМѕЩйСЫИДгУДЮЪ§ЃЌНЕЕЭСЫACSЕЅдЊЕФИДдгЖШКЭЙІКФЁЃЭЌЪБЃЌгЩгкACSЕЅдЊНсЙЙЕФгХЛЏЃЌУПИізДЬЌжЛашвЊЩњГЩвЛЬѕТЗОЖЃЌДцДЂЕФавДцТЗОЖЪ§вВгЩдРДЕФ128ЬѕМѕЩйЮЊ64ЬѕЃЌвВЭЌбљЪЙНсЙЙБфЕУМђЕЅЃЌЙІКФгаЫљНЕЕЭЁЃ ЁЁЁЁгЩЪН(2)КЭЪН(3)ПЩжЊЃЌЪфШыЪ§Он(datain)ВЛЭЌЃЌОэЛ§ТыЕФЪфГіC0КЭC1вВВЛЭЌЃЌвђДЫЃЌЭЌвЛзДЬЌЩЯжЇТЗЕФЪфГігыЯТжЇТЗВЛЭЌЃЌЩЯЯТжЇТЗзДЬЌЪфГіМАвыТыЦїЕФЪфШыЪ§ОнжЎМфЕФЙиЯЕШчБэ1ЫљЪОЃК ЁЁЁЁ  ЁЁЁЁРћгУЩЯЯТжЇТЗЗжжЇЖШСПжЕЕФЙиЯЕОЭПЩвдДгЩЯжЇТЗТЗОЖЖШСПРлМгжЕжаМЦЫуГіЯТжЇТЗТЗОЖЖШСПРлМгжЕЃЌгУVerilog HDLгябдУшЪіЮЊЃК ЁЁЁЁcase(up_branch_metric) ЁЁЁЁ2'b00: down_path_add_metric  ЁЁЁЁЭМ4 ХаОіЪфГіЕЅдЊНсЙЙЭМ ЁЁЁЁ5 ПижЦЕЅдЊ ЁЁЁЁПижЦЕЅдЊ(CU)ВњЩњПижЦИїФЃПщЕФЪБжгаХКХЃЌЪЧЫљгаФЃПщЕФгаађдЫааЕФЛљДЁЁЃИїЪБжгаХКХЙІФмШчЯТЃКclk_loadгУгкЖСШЁЧАвЛЪБПЬИїзДЬЌМФДцЦїЕФФкШнЃЌВЂВњЩњИїзДЬЌЩЯжЇТЗЕФзДЬЌЪфГіжЕ;clk_BMгУгкМЦЫуИїзДЬЌЩЯжЇТЗЕФЗжжЇЖШСПжЕВЂЖСШЁЧАвЛЪБПЬИїзДЬЌЕФТЗОЖЖШСПжЕ;clk_AddгУгкМЦЫуИїзДЬЌЩЯжЇТЗЕФТЗОЖЖШСПжЕ;clk_restoreгУгкднДцИїзДЬЌЩЯжЇТЗЖШСПжЕВЂЛжИДЯргІзДЬЌЯТжЇТЗЕФТЗОЖЖШСПжЕ;clk_C_SгУгкБШНЯВЂбЁдёДяЕНЭЌвЛзДЬЌЕФСНжЇТЗЕФТЗОЖЖШСПжЕЕФНЯаЁепЃЌВЂДцДЂИїзДЬЌбЁдёЕФавДцТЗОЖ;clk_MNSгУгкбЁдёИїзДЬЌДцДЂЕФТЗОЖЖШСПжЕжаЕФзюаЁжЕЃЌВЂБЃДцИУзюаЁжЕЖдгІЕФзДЬЌ;min_sel_1КЭmin_sel_2ЗжСНВНбЁдё4ИіMNSUбЁдёНсЙћЕФзюаЁжЕЃЌВЂбЁГізюжеЕФзюаЁжЕЖдгІЕФзДЬЌ;Decode_OutputгУгкЖСШЁИУзюаЁжЕЖдгІзДЬЌДцДЂЕФавДцТЗОЖЃЌВЂЪфГівыТыНсЙћЁЃ ЁЁЁЁЖўЁЂЯюФПЪЕЪЉЗНАИ ЁЁЁЁViterbiвыТыЦїДѓжТПЩвдЗжЮЊЫФИіВПЗжЃКжЇТЗЖШСПФЃПщ(BMU)ЁЂМгБШбЁФЃПщ(ACS)ЁЂавДцТЗОЖЙмРэФЃПщ(SMU)КЭЪфГіВњЩњФЃПщЁЃЦф жажЇТЗЖШСПФЃПщгУгкЭъГЩвыТыЦїЪфШыаХКХгыЭјИёЭМЩЯЕФПЩФмТЗОЖаХКХЕФЗжжЇЖШСПМЦЫу;МгБШбЁФЃПщжївЊАбЧАвЛИізДЬЌЕФТЗОЖЖШСПгыЕБЧАЪфШыаХКХЕФЗжжЇЖШСПЯрМгЃЌвдЕУЕНИУЗжжЇЕФТЗОЖЖШСПЃЌШЛКѓБШНЯВЛЭЌЗжжЇТЗОЖЖШСПЕФДѓаЁЃЌЭЌЪБевГізюаЁЕФЖШСПжЕЃЌВЂИќаТИУзДЬЌЕФЖШСПжЕЃЌзюКѓЪфГізДЬЌзЊвЦаХЯЂ;ТЗОЖЙмРэФЃПщПЩЖдМгБШбЁЕЅ дЊЪфГіЕФзДЬЌзЊвЦаХЯЂНјааДІРэЃЌвдБуЮЊЪфГіХаОізізМБИЁЃЪфГіФЃПщПЩИљОнавДцТЗОЖЙмРэЕЅдЊЕФЪфГіНјааЪфГіХаОіЃЌзюКѓЪфГівыТыаХЯЂЁЃViterbiвыТыЦїЛљБОдРэПђЭМШчЯТЫљЪОЁЃ ЁЁЁЁ  |

ЭјгбЦРТл