基于SOPC的通用型JTAG调试器的设计

发布时间:2015-11-10 14:07

发布者:designapp

|

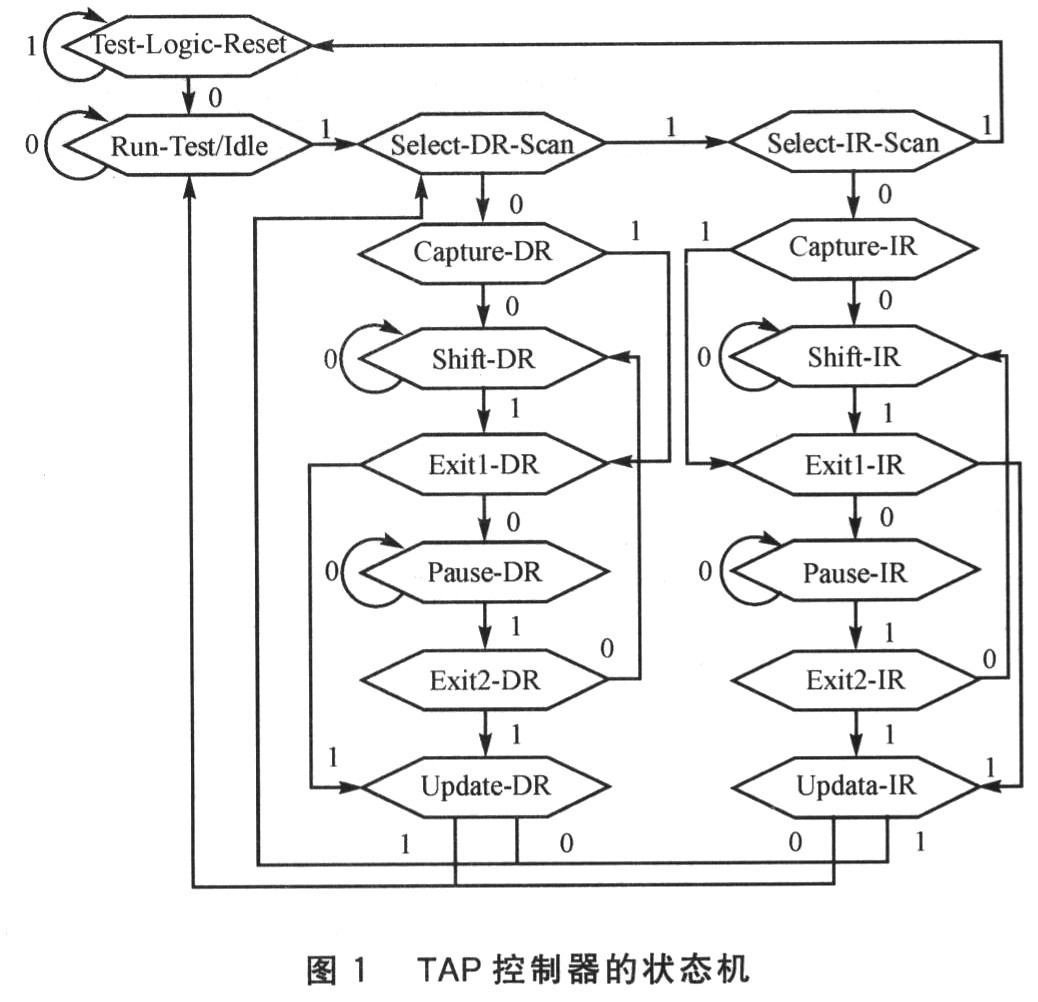

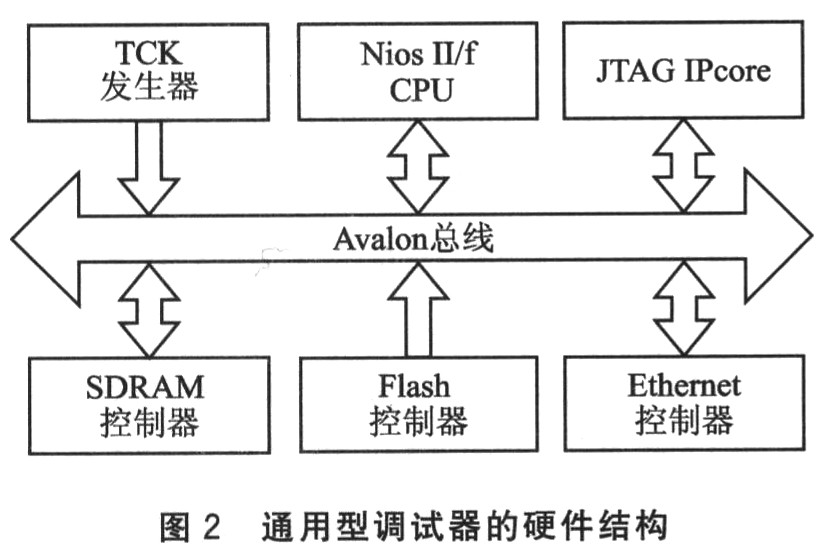

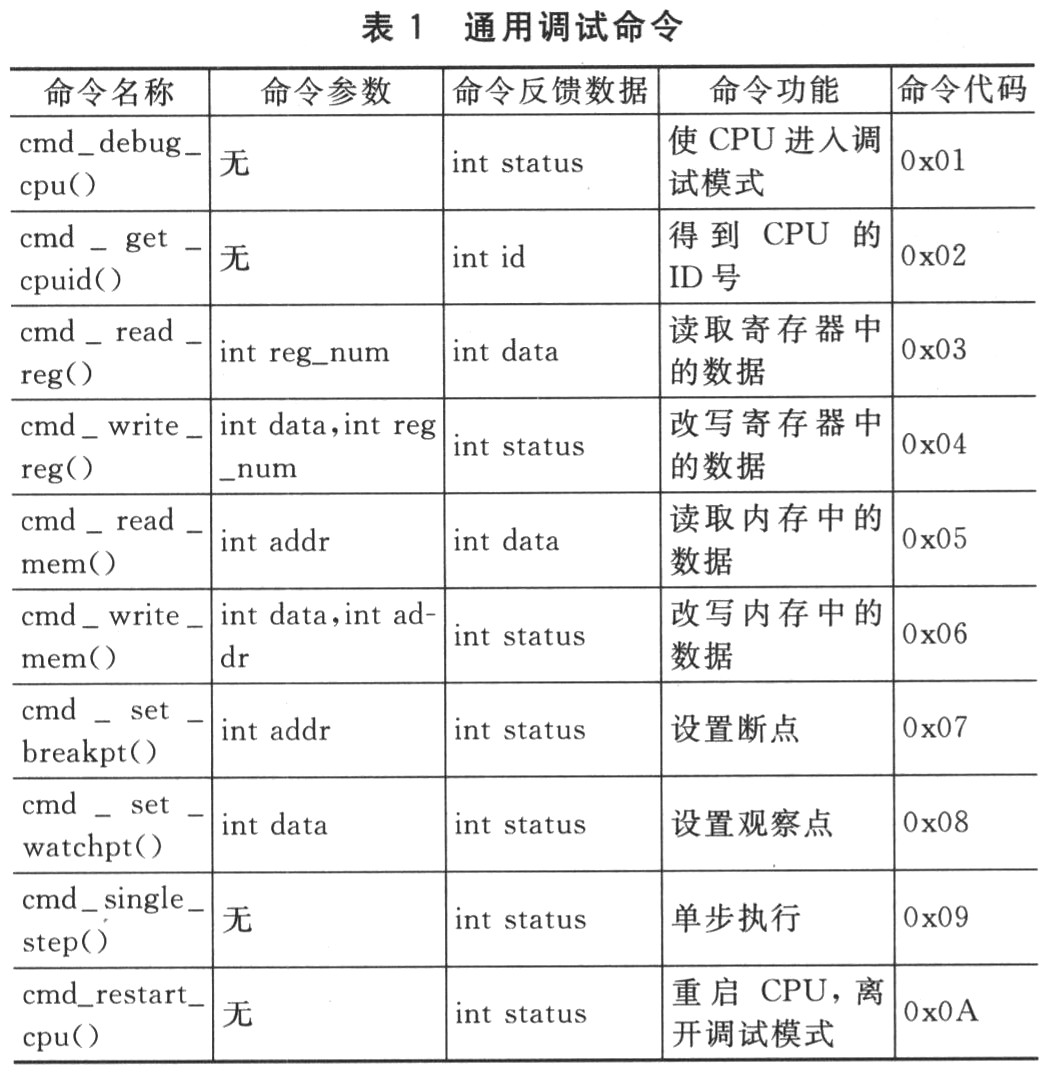

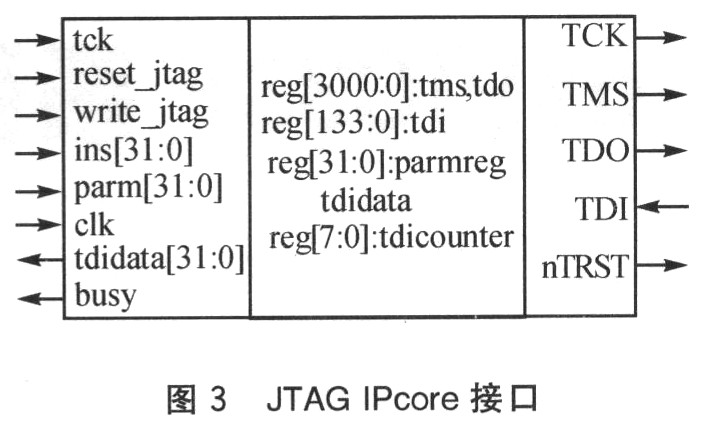

SOPC技术的发展,给仿真器指出了新的发展方向。所谓SOPC技术,就是指用可编程技术将整个系统放在一块硅片上。在传统设计中电路级相互独立的各个系统被集成到一块FPGA芯片中。 SOPC的可重用性是一种先进的设计思想。为了降低用户的负担,避免重复劳动,将一些在数字电路中常用但比较复杂的功能模块,比如SDRAM控制器等,设计成可修改参数的模块,用户在设计系统时可以直接调用这些模块。这些特定的功能模块被称为IPcore(知识产权核)。由于IPcore通常是很成熟的,因此降低了开发风险。 本文利用SOPC技术的特点,设计一种通用型调试器。根据待调试目标板的CPU型号,将相应的调试IPcore和其他通用IPcore一起编译生成一个嵌入式调试系统,下载到FPGA上,实现一个通用型调试器。在使用同一个硬件系统的情况下,可以选择不同的调试IPcore来调试不同的CPU,而不同的IPcore可以方便的互相替换。该方法在设计灵活性、开发成本、开发周期、工作性能等方面都具有优越性。具体的实现采用了Cyclone开发板和Altera开发套件。 1 JTAG调试原理 目前在线仿真调试器中使用最多的调试方法都是基于JTAG标准。1986年,联合测试行动组发表了最早的边界扫描测试规范(Boundary Scan Testing),经不断改进,1990年被批准为IEEE Std 1149.1a标准,简称JTAG标准。现在大多数复杂的IC芯片都带有JTAG调试接口。本文所讨论的调试方法也基于JTAG标准。下面首先简单介绍一下JTAG调试原理。 JTAG调试原理的基础是边界扫描测试。它通过在芯片的每个I/0脚附加一个边界扫描单元(BoundaryScan Cell,BSC)以及一些附加的测试控制逻辑来实现。每个BSC有两个数据通道:一个是测试数据通道——测试数据输入TDI(Test Data Input)、测试数据输出TD0(Test Data 0utput);另一个是正常数据通道——正常数据输入NDI(Normal Data Input)、正常数据输出ND0(Normal Data Output)。在正常工作状态,输入和输出数据可以自由通过每个BSC,正常工作数据从NDI进,从NDO出。在测试状态,可以选择数据流动的通道:对于输入引脚,可以选择从NDI或从TDI输入数据;对于输出引脚,可以选择从BSC输出数据至NDO或至TDO。芯片输入输出引脚上的边界扫描寄存器单元可以相互连接起来,在芯片周围形成一个扫描链。利用边界扫描链就可以控制芯片的输入,观察芯片的输出。一般来说,芯片都提供了若干条扫描链来完成测试功能。例如ARM7TDMI核提供了3条扫描链。 JTAG控制器主要由3部分组成:测试端口控制器(Test Access Port,TAP)、指令寄存器和数据寄存器。其中,TAP控制器是JTAG的核心控制器,需要以下5个控制信号:TCK(边界扫描时钟)、TMS(JTAG测试模式选择)、TDI(串行边界扫描输入数据)、TDO(串行边界扫描输出数据)和TRST(JTAG测试逻辑复位)。正是通过TAP控制器状态的不断变化,JTAG控制器得以控制CPU的运行。TAP控制器的状态机如图1所示。  2 系统设计与实现 2.1 硬件设计与实现 本文采用A1tera的FPGA器件实现了图2所示的硬件结构。  上图列出了所需要的各类IPcore,其中大部分在Altera的开发包中可以找到,主要包括: Nios II/f CPU,50 MHz,Altera提供的免费软核CPU。 Avalon总线,用于数据通信。 Flash控制器,用于控制和操作Flash芯片。Flash芯片中静态存放操作系统、1wIP协议栈及其他调试代码。本系统中使用的Flash芯片为Am29LVl60D,容量为2MB。 SDRAM控制器,用于控制和操作SDRAM芯片。SDRAM芯片用于动态执行调试程序。本系统中使用的SDRAM芯片为三星公司的K4S640432,容量为8 MB。 Ethernet控制器,用于控制和操作网卡芯片。仿真器使用这个以太网口与PC部分的集成开发环境通信。本系统中使用的网卡芯片为LAN91C111。 ARM7TDMI JTAG IPcore,仿真调试IPcore,需要自主开发。其内部逻辑用Verilog语言实现,然后按照Altera IPcore的标准编写IPcore描述文件,最后挂在三态总线上,完成全部调试功能。 TCK发生器,TCK脉冲产生逻辑,需要自主开发。它利用Nios的时钟生成TCK信号,作为时钟来驱动ARM7TDMI JTAG IPcore。它被做成一个小的功能模块,通过PIO与三态总线通信。 上述所介绍的IPcore使用Altera公司的开发工具Quartus II编译,最后下载到Altera FPGA中。本系统使用的CPGA芯片是Cyclone系列的EPlCl2。该芯片包含12 060个逻辑单元,具有239 616位RAM,片上集成2个锁相环,最大用户I/O引脚达到249个。 该硬件结构很好地体现了SOPC的概念,所有的IPcore(包括Altera公司发布和自主开发的)集成在一片FPGA上。一个片上系统就基本包含了在线仿真器的绝大部分功能,任何硬件结构设计的变化都在该片FPGA上,这使得通用在线仿真器这个概念得以实现。对其他芯片在线仿真,只需更改ARM7TDMI JTAG IPcore模块,重新下载到FPGA中,便可以对另一种处理器芯片进行在线仿真。该IPcore用Verilog语言实现,保存为armjtag.v文件。通过Quartus II里的SOPC Builder可以将该文件生成组件,再将其加入Nios系统中。器件引脚分配好后,就在Quartus II里全编译,最后生成ice.pof文件。将该文件通过编程器烧写到配置芯片EPCS4里面。这样硬件系统就完成了。 2.2 软件设计与实现 本系统的软件部分包括2个模块:一是PC端的开发调试界面,二是调试器里面的控制程序。2个模块通过TCP/IP协议通信。 PC端开发调试界面的主要功能是接收用户的调试命令,并显示调试结果。这是系统与用户进行交互的唯一方式。开发调试界面对上给用户提供统一的调试功能接口,对下给调试器提供统一的调试命令。本系统使用VisualC++开发。 调试器里的控制程序主要功能是将上层用户调试命令转换成特定的JTAG指令序列,并控制IPcore将其发送出去,同时接收JTAG反馈信息并发送回用户界面。本系统使用Nios IDE来开发。在Nios IDE的工程属性中加入LwIP和μC/OS组件。主程序首先初始化μC/0S,初始化LwIP协议栈,再启动μC/OS。所有程序控制放在μC/OS的OSStart()任务里。该任务首先建立一个套接字,然后在死循环中等待数据到来。当收到来自PC端的调试命令后,从数据包中分离出命令字和参数,将命令字转换成IPcore需要的调试命令,通过Avalon总线将其发送到IPcore,并等待IPcore工作完成。最后将IPcore传回的数据打包发回PC端。 目前提供的通用调试命令如表1所列。  在TCP/IP数据包中,有效数据为12字节。第1至4字节是命令代码,第5至8字节为命令参数1,第9到12字节为命令参数2。命令参数1和命令参数2是否有效取决于命令代码。主控制程序收到数据包后,将命令代码发往JTAG IPcore的指令端口地址,并根据命令代码向参数端口地址发送命令参数1。如果该命令代码需要命令参数2,则在下一个周期发送。 在SOPC的硬件系统设计中,所有的外设都是统一编址。将JTAG IPcore的指令端口地址和参数端口地址分别设置成0x00910850和0x00910860,端口位宽为32位。因此在程序里,往IPcore发送指令只需要往地址0x00910850写32位数据;往IPcore发送参数只需要往地址Ox00910860写32位数据。反馈数据端口地址设置成Ox00910870,端口位宽为32位。因此在程序里,读取JTAG反馈数据只需读取地址0x00910870的32位数据。 2.3 JTAG IPcore的实现 JTAG IPcore是本调试器的核心,下面简单介绍一下该部分的实现。 IPcore的接口如图3所示。  该IPcore的对外接口由两部分组成:一是与Avalon总线通信的接口部分,即图中的左边部分;二是与被调试CPU通信的接口部分,即图中的右边部分。另外,在整个实现中,定义了一些重要的寄存器。 “reg[3000:O]tms,tdo"分别用来存放完成当前操作的tms序列和tdo序列。像访问存储器这样的操作需要很长的tms序列和tdo序列,因此用了3001位。IPcore每次从这2个寄存器读取1位后,就向对应的引脚发送数据。tdi寄存器只用了134位,因为不是每个tdi输入对JTAG调试都有用。parmreg寄存器用来存放总线上传来的参数。tdidata寄存器用来存放从tdi引脚读取的有效数据,将被发送到Avalon总线。tdicolJnter寄存器用来对tdi输入数据计数。 Avalon总线上来的指令发送到ins[31:0]端口。在调试器主程序里判断指令,做出相应的动作。当IPcore读取到某个指令后,根据命令代码查找对应的TMS命令序列,找到以后将命令序列送到tms寄存器。同时,通过parm[31:O]端口读取命令参数,根据命令参数生成对应的TDO序列,将其送到tdo寄存器。当两个寄存器的内容准备好后,在TCK时钟的控制下,通过TMS引脚和TD0引脚分别串行输出。在TDO引脚输出的同时检测TDI引脚,并在适当时机将TDI引脚上的数据读入IPcore,经过处理后发送回总线。 由于TMS序列长度较长且其对应于各个调试命令是固定不变的,因此在本设计中,将TMS序列作成一个表,存放在IPcore里,而不是通过总线发送。需要时,根据不同的命令代码来读取。这样可以节约时间,提高调试速度。 结 语 本文介绍了一个基于SOPC的通用调试器的设计方案与实现过程。在开发过程中,IP复用、软硬件协同设计等先进的嵌入式设计思想对缩短开发时间、降低开发风险起到了很好的作用。同时,自主开发的ARM7TDMIJTAG IPcore和C8051 JTAG IPcore体现了该调试器的通用性。接下来还将推出基于ARM其他系列和PowerPC系列的IPcore,本调试器的应用价值将得到进一步提高。 |

网友评论