FPGA设计开发软件ISE使用技巧之:典型实例-ChipScope功能演示

发布时间:2015-11-10 11:15

发布者:designapp

|

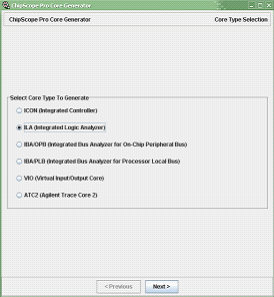

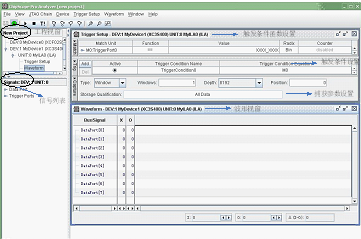

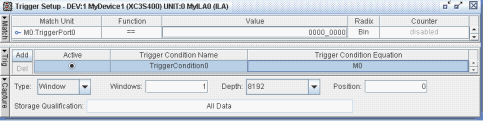

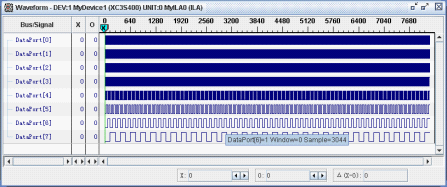

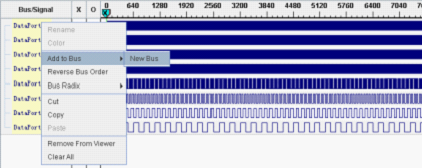

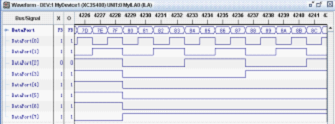

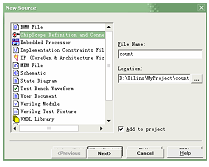

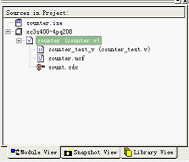

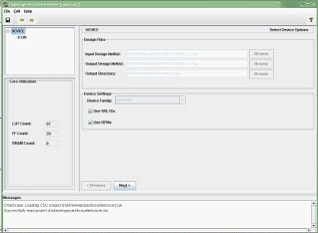

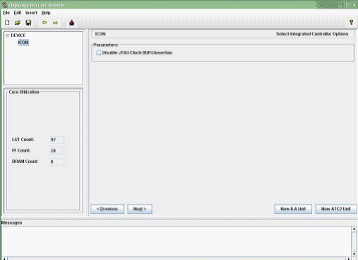

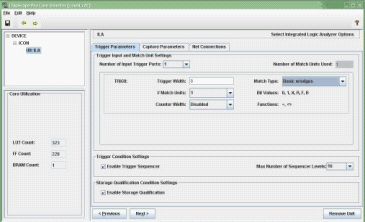

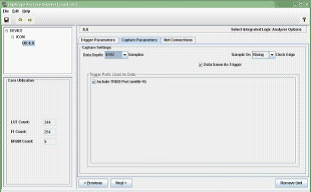

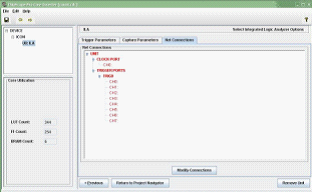

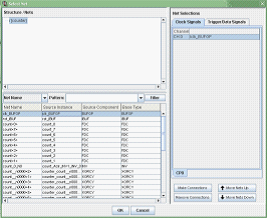

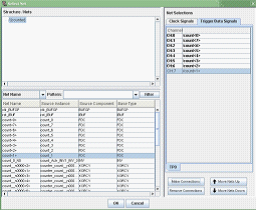

6.8 典型实例11:ChipScope功能演示 6.8.1 实例的内容及目标 1.实例的主要内容 本节通过一个简单的计数器,使用ChipScope的两种实现流程,基于Xilinx开发板完成设计至验证的完整过程。本实例的工作环境如下。 · 设计软件:ISE 7.1i。 · 综合工具:ISE自带的XST。 · 仿真软件:ModelSim SE 5.8C。 · 在线调试:ChipScope Pro 8.2i。 · 硬件平台:红色飓风II代Xilinx开发板。 · 实例内容:计数器。通过ChipScope Pro观测计数器的计数值,代码参见本书实例代码的“典型实例11”文件夹。其中count_new文件夹对应采用流程1实现的工程,count文件夹对应用流程2实现的工程。 使用ChipScope Pro进行在线调试主要有两种实现流程。 (1)基于ChipScope Pro Core Generator的实现流程。 · 调用ChipScope Pro Core Generator生成逻辑分析仪的网表文件。 · 修改用户RTL,插入逻辑分析仪代码。 · 综合,实现,下载bit配置文件。 · 调用ChipScope Pro Analyzer观察波形。 (2)基于ChipScope Pro Core Inserter,通过新建资源的实现流程。 · 对工程文件进行综合,生成网表文件。 · 调用ChipScope Pro Core Inserter,插入逻辑分析核。 · 布局、布线,生成bit配置文件并下载。 · 调用ChipScope Pro Analyzer观察波形。 由上面可以看出,两种实现方式的主要区别在于生成逻辑分析核的方式不同。本实例将分别采用这两种方式应用ChipScope Pro观测FPGA内部信号。 为了便于读者的理解,本实例将编写一个简单的计数器,通过ChipScope Pro观测计数的数值。代码的功能仿真结果如图6.59所示。  图6.59 计数器功能仿真结果 其中,count为8位计数值,采用循环计数方式。 2.实例目标 通过本实例,读者应达到下面的目标。 · 熟悉ChipScope工具的使用方法。 · 熟悉基于ChipScope Pro Core Generator的实现流程。 · 熟悉基于ChipScope Pro Core Inserter的实现流程。 6.8.2 基于ChipScope Pro Core Generator的实现流程 基于ChipScope Pro Core Generator实现流程的具体步骤如下。 (1)新建工程,添加源代码。 新建ISE工程后,将源代码文件counter_new.v及约束文件counter.ucf添加至工程中,如图6.60所示。 (2)启动ChipScope Pro Core Generator。 运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Core Generator”命令,启动ChipScope Pro Core Generator,出现如图6.61所示界面。   图6.60 新建工程结果 图6.61 ChipScope Pro Core Generator用户界面 (3)选择集成控制核(ICON核)。 首先在核类型选择页面中选择生成ICON核,如图6.61所示。 (4)选择目录及器件。 如图6.62所示,在本实例中选择Spartan3器件。输出路径选择新建工程所在的文件夹。控制端口的数目为1,控制端口的数目可以根据用户的需要设置。如需要观察多组数据时,可以设多组控制端口。这里只需要观察内部计数器的计数值,因此设置为1。 (5)选择语言类型和综合工具。 如图6.63所示,本实例中设置语言类型为Verilog,综合工具为Xilinx XST。  图6.62 ICON输出路径和FPGA系列设置对话框  图6.63 设置语言和综合工具 (6)生成ICON核。 如图6.64显示为生成的ICON核的相关信息,如发现有误,可以单击“Previous”按钮做修改后重新生成。  图6.64 生成ICON核 (7)选择集成逻辑分析仪(ILA核)。 生成ICON核后,单击“Start Over”按钮,回到核类型选择页,如图6.65所示,选择需要生成的核为ILA。  图6.65 生成集成逻辑分析仪 (8)设置输出路径、器件参数和时钟参数。 如图6.66所示为设置路径为新建工程所在路径,器件为Spartan3,采样时刻为时钟的上升沿。  图6.66 设置ILA输出路径、FPGA器件、采样时刻对话框 (9)设置触发参数。 触发参数的设置包括:触发端口数目(Number of input Trigger ports)、每个触发端口的触发宽度(Trigger Width)、触发条件判断单元个数(Match Units)和类型(Match Type)等。 此外,“Enable Trigger Sequencer”选项用于使能触发条件链。即设置触发条件为一“条件链”,只有依次满足“条件链”上的各个条件时才会被触发。如图6.67所示,如有与图中参数设置不一致之处,请自行修改。 (10)设置存储深度和数据位宽。 存储深度即在满足触发条件后要采集多少数据,存储深度的大小由FPGA的RAM资源大小决定。由于ChipScope所采集的数据都是保存在FPGA内部,因此存储深度的大小不能超过FPGA的RAM的最大值。如图6.68所示,选择“Data Same As Trigger”选项表示数据信号与触发信号相同,数据位宽即为触发端口的触发宽度。 (11)设置语言类型和综合工具。 如图6.69所示,本实例中选择Verilog及Xilinx XST。 (12)生成ILA核。 单击图6.69中的“Generate Core”按钮,生成逻辑分析仪(ILA),如图6.70所示。  图6.67 设置触发参数对话框  图6.68 设置存储深度和数据位宽对话框  图6.69 设置生成实例的语言类型和综合工具  图6.70 生成ILA核 (13)将ICON和ILA插入设计。 完成上述步骤后就完成了集成控制核(ICON)和逻辑分析仪(ILA)的生成,系统生成的主要文件如表6.5所示。 表6.5 ChipScope生成文件列表 icon.edn集成控制器的网表文件 icon.ncf集成控制器的网表约束文件 icon_xst_example.v集成控制器的嵌入式例子代码 ila.end集成逻辑分析仪的网表文件 ila.ncf集成逻辑分析仪的网表约束文件 ila_xst_example.v集成逻辑分析仪的嵌入式例子代码 用户需要做的是根据提供的例程代码来修改自己的代码,将生成的集成控制核和集成逻辑分析仪插入到设计当中。具体修改时,需要在源文件中添加如下代码: icon i_icon // ICON core instance,实例化ICON核 ( .control0 (control0) ); wire [7:0] trig0; ila i_ila // ILA core instance,实例化ILA核 ( .control (control0), .clk (clk), .trig0 (trig0) ); assign trig0 = count; 从代码中可以看出要做的工作主要是实例化ICON核和ILA核。注意要将观察的信号(在这里为count)与ILA核的输入信号相连接,系统时钟与ILA核的时钟输入相连接,ICON的输出控制信号与ILA的输入控制信号相连接。这样就可以通过修改RTL代码来插入集成逻辑控制器和集成逻辑分析仪了。 (14)综合,布局布线,生成配置文件并下载。 具体的操作步骤可以参看2.6节的介绍,这里不再详述。需要注意的是ChipScope Pro要通过JTAG接口与器件连接。生成配置文件时,时钟要设置为JTAG Clock。 (15)启动ChipScope Pro Analyzer。 可通过直接运行“开始”/“程序”/“ChipScope Pro 8.2i”/“ChipScope Pro Analyzer”,也可以在ISE集成环境下,在进程浏览器中双击“Analyze Design Using ChipScope”启动。启动后界面如图6.71所示。 (16)打开JTAG连接。 单击  图标,打开JTAG并口连接电缆,在此之前要保证已将JTAG与器件连接好,如果连接无误,正常连接后会出现如图6.72所示的界面。 (17)设置触发条件。 触发条件设置如图6.73所示。  图6.71 ChipScope Pro Analyzer用户界面  图6.72 成功连接后用户界面  图6.73 设置触发条件对话框 设置触发条件函数为“==”,数值为0000_0000(也就是说,触发端口的信号值为0000_0000时开始采集数据)。设置采集深度为8192。这里只有一个触发件M0,只需采用默认即可。当有多个条件时,要在“Trig”选项卡下设置起作用的正确条件,也可将触发条件设置为几个条件的逻辑组合。 (18)开始采样调试。 单击左上角的  运行按扭,开始采样。捕获触发条件后,ChipScope将采集所设置存储深度的波形,如图6.74所示。  图6.74 采集信号的波形图 在波形显示窗口下可对波形进行放大  和缩小  ,也可以进行局部放缩  。当要观察总线数据时,可以先选中所有总线数据,然后单击右键,选择“Add to Bus”/“New Bus”即可如图6.75所示。  图6.75 组合总线数据 添加成功后,就可以在新生成的Bus下看到总线数据,如图6.76所示。图中DataPort为新生成的总线,设计者可以根据需要修改总线的名称。  图6.76 总线数据生成结果 通过上述步骤就完成了应用ChipScope Pro的一个完整的流程,这种流程是通过修改源代码来添加逻辑分析仪的。下面的流程可以不用修改设计代码,直接将逻辑分析仪插入到设计的网表文件中,使用方便,应用比较广泛。 6.8.3 基于ChipScope Pro Core Inserter的实现流程 基于ChipScope Pro Core Inserter实现流程的具体步骤如下。 (1)新建工程,添加源代码。 参见第一种实现流程的同一步骤。 (2)新建ChipScope Pro 资源。 选择ISE的“Project”/“New Source”,再选择“ChipScope Definition and Connection”选项,输入新建资源的名称:count,生成count.cdc资源文件。如果有现成的扩展名为cdc的文件,也可以通过“Project”/“Add Source”来添加,如图6.77所示。 完成后在工程浏览器中可以看到包含的count.cdc文件,如图6.78所示。   图6.77 新建.cdc资源对话框 图6.78 新建.cdc资源结果 (3)综合。 与前一种设计流程不同,这里要先对源文件进行综合,在这种设计流程中,ILA核是直接插入到设计综合后生成的逻辑网表中的,因此要先对源文件进行综合。 (4)设置ICON及ILA各项参数。 在工程浏览器中双击count.cdc文件,打开ChipScope Pro Core Inserter工具,如图6.79所示。  图6.79 ChipScope Pro Core Inserter用户界面 在图中可以看到,这里无需再设置输入网表文件的路径,系统会自动找到网表文件,并设置输出文件的路径。 单击“Next”按钮进入ICON核设置页面,如图6.80所示。  图6.80 “Select Integrated Controller Options”ICON对话框 其中,“Disable JTAG Clock BUFG Insertion”用于指定是否禁止在JTAG时钟上插入BUFG。如果选中此项,JTAG时钟将使用普通布线资源,而不是全局时钟布线。这里此项不选,用全局时钟布线。 完成ICON核的设置以后,选择单击“Next”按钮,进入ILA核设置页面,如图6.81所示。  图6.81 “Trigger Parameters”选项卡设置 在触发器设置页面中,设置触发端口数、触发宽度、触发条件单元函数和个数等。如有不一致,请读者对照上图修改,设置完毕后单击“Next”按钮出现如图6.82所示对话框。  图6.82 “Capture Parameters”选项卡设置 如图6.82所示,设置存储深度为8192,采样时刻为上升沿。选中“Data Same As Trigger”,即数据信号与触发信号相同。设置完毕后单击“Next”按钮,可以看到已经定义的ILA,如图6.83所示。  图6.83 “Net Connection”选项卡设置 此时由于还没有对网表进行映射,因此网络线都是呈红色显示。单击“Modify Connection”按钮,设置时钟信号和TRIG信号与要观测的信号的映射关系,如图6.84及6.85所示。  图6.84 设置时钟信号连接  图6.85 设置数据连接 信号连接主要完成时钟信号的连接和触发信号的映射。将clk_BUFGP与Clock Signals中的CH0连接,将count~count的内部信号与Trigger Data Signals的CH0~CH7相连。连接方法很简单,选中要连接的信号,单击“Make Connections”按钮即可。 当所有信号都连接完毕,“Net Connection”选项卡下显示的网路线会由红色变为黑色。如果仍有信号未连接,则仍为红色,直到所有信号连接完毕。 设置完毕后,单击“Return To Project”。此时逻辑分析仪已经插入到了工程网表文件当中了,不需要用户再对源代码进行修改。 (5)布局布线,生成配置文件并下载。 对工程进行综合、布线布局,之后生成配置文件并下载。 (6)启动ChipScope Pro Analyzer进行观察。 启动ChipScope Pro Analyzer后,剩下的步骤与前一种方法完全一致,这里就不再重复说明。 6.8.4 小结 本节通过一个具体的实例,详细演示了ChipScope Pro的两种使用方法。希望读者能够按照这两种流程动手练习一下,熟练掌握这一工具的使用。 在具体应用当中,第二种方法应用得比较广泛,因为无需修改源代码,而且修改逻辑分析仪的各项参数也很方便,因此推荐读者使用第二种方法。ChipScope Pro是个功能很强大的在线逻辑分析工具,熟练地掌握它的用法并应用于自己的设计当中,将会给调试过程带来极大的方便。 |

网友评论