FPGA在数字信号处理中的简单应用

发布时间:2015-11-9 14:22

发布者:designapp

|

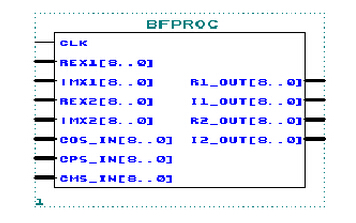

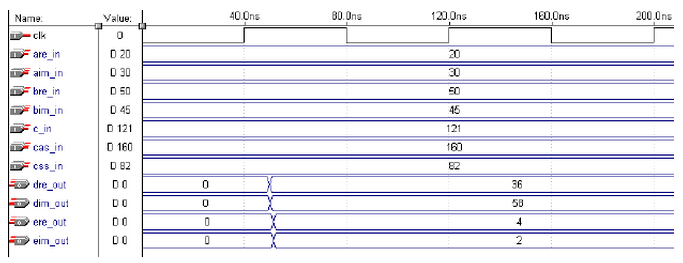

数字信号处理技术已经成功运用于信号地滤波、语音、图像、音频、信息系统、控制和仪表设备。可编程数字信号处理器在20 世纪70 年代地引入更是使DSP 技术突飞猛进,取得巨大成功,这些PDSP 都是基于精简指令集(RISC)计算机范例的架构。它的优势源于大多说信号处理算法的乘-累加运算(MAC)都是非常密集的。通过多级流水线架构,PDSP 可以获得仅受阵列乘法器的速度限制的MAC 速度。由此可以认为FPGA 也能够用来实现MAC 单元,且具有速度优势,但是,如果PDSP 能够满足所需要的MAC 速度,那么PDSP 在成本问题上更具有成本优势,但随着FPGA 成本降低,这个优势正在缩小。另一方面,现在我们还发现了许多高带宽的信号处理应用领域,例如:无线电、多媒体或卫星通信,FPGA 技术可以通过一个芯片上的多级MAC 单元来提供更多的带宽。此外,在诸如CORDIC($1087.5000)、NTT 和差错校正算法等算法中,FPGA 较PDSP 更有效率优势。 FPGA 技术的关键就是利用强有力的设计工具以: ▲ 缩短开发周期。 ▲ 提高器件资源利用率。 ▲ 提供综合器的选择,例如:在最佳速度和设计规模之间做出选择。 FPGA兼有串、并行工作方式和高集成度、高速、高可靠性等明显的特点,其时钟延迟可达纳秒级,同时,在基于芯片的设计中可以减少芯片数量,缩小系统体积,降低能源消耗,提高系统的性能指标和可靠性。正是由于FPGA具有这些优点,FPGA在超高速应用领域和实时测控方面有非常广阔的应用前景。在高可靠应用领域,如果设计得当,将不会存在类似于MCU的复位不可靠和PC可能跑飞等问题。FPGA的高可靠性还表现在,几乎可将整个系统下载于同一芯片中,实现所谓片上系统,从而大大缩小了体积。与AMU设计相比,FPGA显著的优势是开发周期短,投资风险小、产品上市速度快,市场适应能力强和硬件升级回旋硕士学位论文余地大,而且当产品定型和产量扩大后,可将在生产中达到充分检验的VHDL设计迅速实现ASIC投产。 随着大规模现场可编程逻辑器件的发展,系统设计进入“片上可编程系统”(SOPC)的新纪元;芯片朝着高密度、低压、低功耗方向挺进:在SOC芯片上可以将微处理器、数字信号处理器、存储器、逻辑电路、模拟电路集成在一个芯片上。而如果将可编程逻辑电路IP核集成到SOC芯片上则会大大提高SOC芯片的灵活性与有效性,并且缩短了SOC芯片的设计周期。因此国际各大公司都在积极扩充其IP库,以优化的资源更好的满足用户的需求,扩大市场。 综上所述,与ASIC和通用DSP相比,FPGA器件能够以高速、实时、低成本、高灵活性的优点应用于数字信号处理领域,利用FPGA实现数字信号处理成为数字信号处理领域的一种新的趋势,它可以完全取代通用DSP芯片或作为通用DSP芯片的协处理器进行工作。如果将通用处理器和FPGA融合在一起,把需要多个时钟周期的运算交给FPGA完成,DSP芯片主要完成单时钟的运算和控制FPGA的“可再配置计算”功能,会更好地将两者的优势发挥出来。 蝶形运算单元的FPGA实现 蝶形运算单元是FFT处理器的基本单元,用来计算两点的FFT。由于蝶形运算单元是由一个复数加法器、一个复数减法器和一个旋转因子复数乘法器组成,所以利用上面设计的旋转因子复数乘法器和MAX+PLUSII中的lpm_add_sub模块可以设计实现蝶形运算单元。基-2 FFT蝶形运算单元的VHDL代码见附录B。从代码中可以看出,蝶形处理器是由一个加法器、一个减法器和一个实例化为组件的旋转因子乘法器实现的。对应硬件实现的输入输出框图如下图所示:  蝶形处理器的输入输出框图 对输入值为A=20+30J、B=50+45j、旋转因子C+jS=256×e∧jpi/9=121+j39时进行仿真。仿真波形如下图所示:  蝶形运算单元的VHDL仿真波形 可见,所设计的蝶形处理器在MAX+PLUSII中对于输A=20+30J、B=50+45j、旋转因子C+jS=256×e∧jpi/9=121+j39时进行仿真得到的输出结果和理论上计算得到的结果是完全相符的,从而说明基于VHDL语言设计的蝶形处理单元的正确性。 本文通过设计一种基于FPGA的FFT探讨了FPGA在数字信号处理中的应用。本文重点设计实现了蝶形运算单元,并且进行了仿真,通过比较可以看出仿真结果与理论值吻合的很好。本系统的最大优势在于利用FPGA器件丰富的逻辑资源,内嵌的RAM, ROM块及其灵活的可编程特性使运算速度较传统方法有了很大提高。当然付出的代价是用这种并行的结构需求的硬件资源很多。 随着芯片集成度的不断提高,用这种并行结构实现的FFT运算其优越性将越来越明显。而且用这种结构实现的FFT很容易扩展,只需要增加蝶形的个数和循环次数即可。基于FPGA的FFT/IFFT处理器由于其硬件上的并行性,速度远远快于一般的通用DSP。FPGA具有成千上万的查找表和触发器,因此,FPGA平台可以利用更低的成本达到比通用DSP更快的速度。采用FPGA技术,还可以获得高性能,满足成本要求,并享有快速有效地对新设计进行优化的灵活性。这种基于并行算法的FFT/IFFT处理器,可以广泛应用在高速信号处理系统中。并且由FFT处理器的设计可以看出,前端的可编程数字信号处理算法,例如FIR和IIR滤波器,都可以利用FPGA构建。 用FPGA实现数字信号处理在现代通信中将得到很广泛的应用。DSP IP是3G无线通信、数字音频和视频图像处理、广播、多信道多点分布服务(MMDS)以及正交频分复用(OFDM)系统等新兴应用的理想选择。可编程逻辑和软IP核的灵活性让各个公司能够让他们的设计快速地适应新标准。 目前,Altera已经设计实现了DSP功能块。Altera的DSP IP套装包括标准DSP功能(如Turbo($2175.0000)译码器)。IP核是静态参数化的,这样MegaWizard Plug-In Manager根据给定的一组参数生成最高效的硬件。这些插件允许设计者无需改变设计源代码就可以定制IP。而且,软IP能够立刻导入新的Altera FPGA器件系列中。这一解决方案可满足设计和生产部门两方面的要求。 可见,硬件和软件设计者可以利用可编程逻辑开发各种DSP应用解决方案,可编程解决方案可以更好的适应快速变化的标准、协议和性能需求。随着新的FPGA体系的出现,DSP IP核和工具数量的增加,采用可编程逻辑的DSP应用继续增加。FPGA器件能够以高速、实时、低成本、高灵活性的优点应用于数字信号处理领域,它可以完全取代通用DSP芯片或作为通用DSP芯片的协处理器进行工作。 |

网友评论