基于DDS的短波射频频率源设计与实现

发布时间:2015-11-3 14:43

发布者:designapp

|

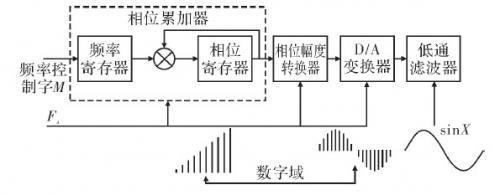

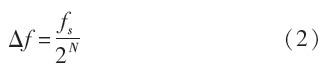

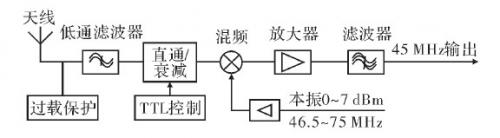

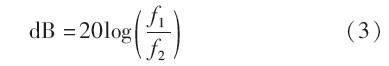

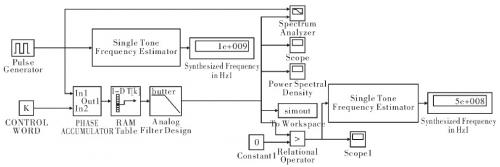

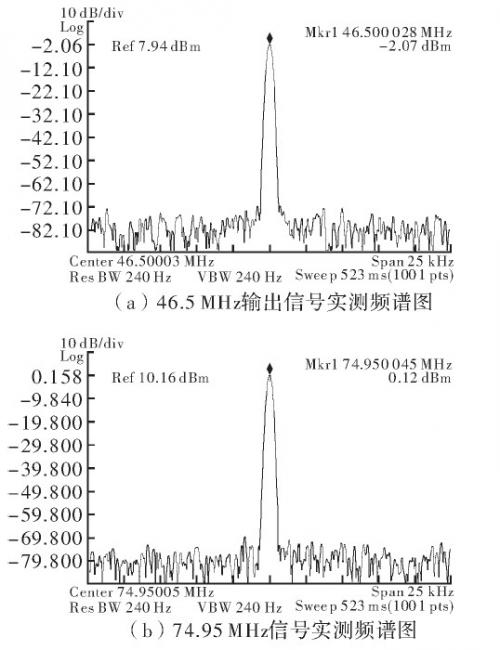

介绍了直接数字频率合成(DDS)的结构和原理,并将DDS技术应用于短波射频通信频率源中。实现了一种基于单片机+DDS可编程低噪声频率源,输出信号范围46.5~75 MHz.实验结果表明,该频率源具有频率分辨率高、相位噪声低等优点,满足短波射频通信系统对频率源的设计要求。 频率源是现代短波射频通信系统的核心,对整个系统的正常运行起着决定性的作用。作为射频电路与系统的核心设备,频率源的好坏关系着整个系统的稳定性。现在的频率合成技术正朝着杂散和相位噪声更低的方向发展,同时还要求有更宽的频带和更高的频率分辨率。直接数字频率合成(DDS)正是在这种需求背景下发展起来的,它具有极微小的频率调谐和相位分辨能力。融合了模拟和数字技术的DDS是产生高质量、高频谱纯度、宽频带频率的理想方法。文中基于ADI公司的AD9912芯片提出一个直接频率合成方案,输出频率范围为46.5~75MHz. 1 DDS基本工作原理 直接频率合成器DDS本质上是一种高分辨率的数字分频器。通过频率调节字来分频系统时钟,以输出所需的频率。DDS有两个显着特点:(1)DDS工作在数字域,其输出频率、相位和幅度可以在数字处理器的控制下,精确而快速地变换;(2)其频率分辨率主要取决于频率调节字的位数,可以达到极高的频率分辨率。 典型的DDS原理框图如图1所示。它主要包括:相位累加器,相位-幅度变换器,数/模变换器和低通滤波器。  图1典型的DDS原理框图 (1)相位累加器。 对于正弦波而言,虽然幅度不是线性的,但其相位却是线性变化的,这正是DDS能够合成正弦波的基础。DDS根据频率调节字的位数N,把0°~360°的相位变化平均分成2N等份。假设系统参考时钟为fs;输出频率为fout.在每个时钟周期转过一个角度360°/2N,则可以产生一个频率为fs/2N的正弦波的相位增量。因此,只需选择恰当的频率调节字M,使得fout/fs=M/2N,就可以得到所需的输出频率fout.  由式(1)可以得到DDS的最小频率分辨率为  (2)相位幅度转化器。 根据相位累加器的输出,可以得到合成fout频率所对应的相位信息,相位幅度转化器可以把累加器输出的数字相位信息变换成相应的幅度值。这个数值以二进制的形式被送入DAC进行数模转换。此相位到幅度的转换通过查表操作完成。 (3)D/A数模变换器。 从相位幅度转换器得到的二进制数字信号被送入数/模(D/A)转换器中,变换成模拟信号输出。此处D/A变换器的位数对输出频率的分辨率并没有影响。输出频率的分辨率由频率调节字的位数决定。 2系统设计 设计中采用低抖动、低杂散的直接数字频率合成器DDS作为短波射频通信系统的本振源。整个短波射频系统的原理框图如图2所示。  图2短波射频系统的原理框图 设计采用ADI公司的高端产品AD9912.它最高支持1 GHz的采样时钟,并且内置了一个14 bit的D/A变换器,支持48 bit的频率调节字,最高频率分辨率为4μHz.AD9912的突出特点是拥有能编程的辅助直接数字频率合成器通道,可以降低输出频谱中谐波杂散的等级,改进了DDS固有的杂散和噪声大的缺点。 本设计中采用MSP430F2012单片机作为AD9912频率输出的控制器。在启动DDS芯片前,首先要配置信号IO_UPDATE、PWRDOWN、HOLDOVER及S1~S4时钟使能信号,使AD9912正常工作。DDS上电启动后,单片机通过SDO、CSB、SCLK向AD9912写入频率调节字,输出HSTL电平的时钟信号。信号经选择和电平转换后,经过输出驱动器输出。 AD9912内部集成了采样时钟倍频器,即锁相环(PLL)。在使用PLL的情况下,采样时钟源中的任何噪声或杂散都会在PLL的环路带宽以20lo gx关系被放大,x是频率放大的倍数。由于输入时钟的杂散在输出的相位噪声会随着输出频率不同而改变,在采样时钟相同的情况下,输出两个不同频率时的相位噪声关系为  从式(3)可以看出,在固定输出频率的前提下,尽量提高采样时钟速率可以提高输出频率的相位噪声性能。在设计中,为达到最佳的性能,放弃了内部PLL环路,而采用外部高性能PLL输出的1GHz采样时钟。 2.1外部环路滤波器设计 外部环路滤波可以将DAC输出的杂波和镜像频谱滤掉,可以平滑输出波形,对信号的输出质量有较好地改善作用。外部环路滤波器采用椭圆函数低通滤波器。电路设计时采用分立LC元件构成截止频率为400 MHz的低通滤器。电路原理及仿真结果如图3所示。  图3环路滤波器的原理图及仿真结果 2.2编程控制 对AD9912编程是为了实现频率的步进控制,处理由外部控制输入的频率值,由单片机生成频率调节字,经SPI方式送入DDS中,合成系统所需的频率。数据写入时SCLK、SDI、CSB信号由单片机产生,写入时序严格按照SPI协议进行。 3仿真及测试结果 DDS输出波形的仿真采用Matlab中的Simulink工具。根据DDS的工作原理及AD9912的数据手册,可以建立AD9912在Simulink中的模型。AD 9912的Simulink模型如图4所示。  图4 AD 9912在Simulink下的仿真模型 设置频率调节字M=14073748835532后,得到DDS输出信号的频率为50 MHz,Simulink仿真功率谱密度如图5所示。  图5 M=14073748835532的功率谱密度分布图 射频短波通信系统中对频率源的输出的频带宽度要求为46.5~75 MHz,步进频率为50 kHz.AD9912的输出分辨率为fDDS=f/248,本设计中采样时钟1 GHz,最小分辨率可达3.55μHz,完全可以达到设计指标。图6是安捷伦频谱分析仪实测的DDS输出信号频谱图。  图6 DDS输出信号频谱图 4结束语 针对射频短波通信系统中的频率源要求,分析了整个频率源的实现方法。搭建了单片机+DDS的实现方法,采用具有杂散抑制通道的新型DDS芯片AD9912,时钟输入采用外部低杂散高性能的PLL信号,增加外部环路滤波网络,有效提高了输出信号的质量。通过对输出信号的测试,验证了该方案在输出频带46.5~75 MHz内具有相位噪声小、频率值精准、频率分辨率高等特点,满足短波射频通信对频率的指标要求。 |

网友评论