Xilinx FPGA入门连载18:蜂鸣器开关实例

发布时间:2015-10-28 10:25

发布者:rousong1989

|

Xilinx FPGA入门连载18:蜂鸣器开关实例 特权同学,版权所有 配套例程和更多资料下载链接: http://pan.baidu.com/s/1jGjAhEm

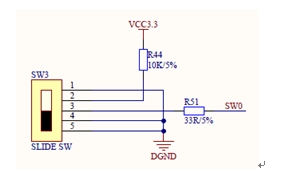

我们已经在sp6_ex2中,知道了蜂鸣器工作的基本原理,即FPGA输出高电平就发出响声,FPGA输出低电平就停止发声。在本节中,我们增加一个拨码开关做控制,让拨码开关的ON或OFF状态相应的去控制蜂鸣器的发声与不发声。 拨码开关SW3的电路图如下所示。拨码开关与FPGA相连接的SW0信号的电平值取决于拨码开关当前的位置,若它连接了2-3脚,那么SW0就是高电平状态,若它连接了3-4脚,就是低电平状态。

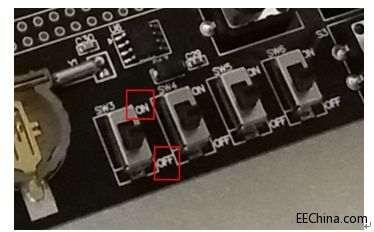

如图所示,每一个拨码开关的右侧都有“ON”和“OFF”的丝印标示。“ON”对应的是3-4脚连接状态,“OFF”对应的是2-3脚连接状态。

综上所述,也就是当拨码开关处于“ON”状态时,SW0输出低电平;当拨码开关处于“OFF”状态时,SW0输出高电平。 而我们要实现的功能是,当拨码开关处于“ON”状态时,蜂鸣器发声;当拨码开关处于“OFF”状态时,蜂鸣器不发声。 对于已有的例程,打开工程通常有两种方式。 第一种方式如图所示。直接到sp6ex3工程文件夹下,找到sp6.xise文件,双击它就能够直接启动ISE打开该工程。

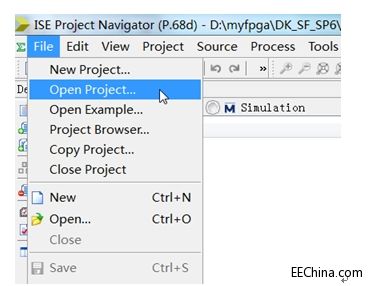

第二种方式,先打开ISE。然后如图所示,在菜单中选择“File à Open Project…”。

弹出窗口中,找到sp6ex3工程文件夹,选择sp6.xise文件,单击“打开”。

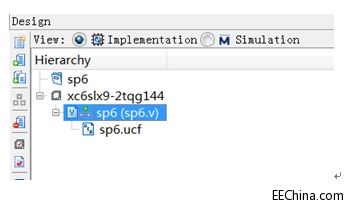

打开工程以后,如图所示,在“Design à Implementation”窗口下,可以双击查看工程源码sp6.v,或者查看工程的引脚约束脚本sp6.ucf。

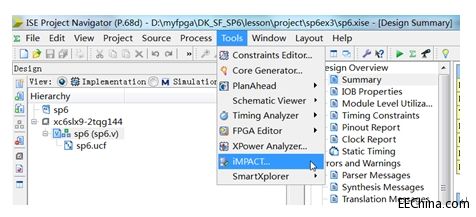

如图所示,在ISE菜单栏点击“Tools à iMPACT...”,启动专门用于FPGA下载配置的iMAPCT工具。

其他相关操作,可以参考lesson17。最终需要将sp6ex3工程下的sp6.bit文件下载到FPGA中。下载完成后,可以尝试拨动拨码开关SW3,看看蜂鸣器的发声是否有变化。 |

网友评论