Xilinx FPGAШыУХСЌди12ЃКPWMЗфУљЦїЧ§ЖЏжЎв§НХЗжХф

ЗЂВМЪБМфЃК2015-10-14 11:15

ЗЂВМепЃКrousong1989

|

Xilinx FPGAШыУХСЌди12ЃКPWMЗфУљЦїЧ§ЖЏжЎв§НХЗжХф ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1jGjAhEm

ИДжЦsp6ex1ећИіЮФМўМаЃЌНЋЦфИќУћЮЊsp6ex2ЁЃШЛКѓЮвУЧДђПЊЁАЁ\sp6ex2\source_codeЁБЮФМўМаЯТЕФsp6.vдДДњТыЮФМўЁЃ ЩОГ§sp6.vЮФМўдгаЕФДњТыЃЌНЋЩЯвЛИіlessonЕФдДТыећИіИДжЦНјШЅЁЃШчЭМЫљЪОЁЃ

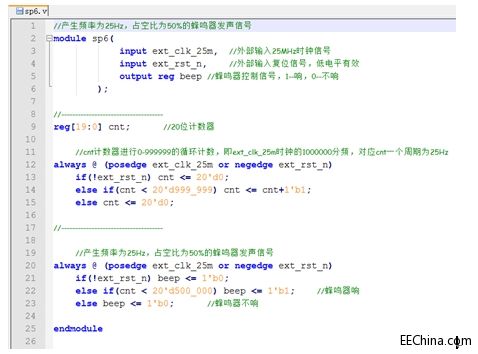

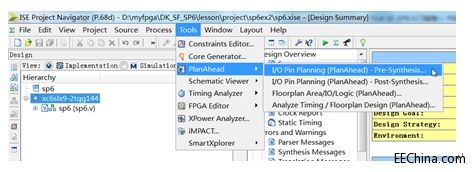

НгзХЪЙгУISEДђПЊИеИевЦжВКУЕФsp6ex2ЮФМўМаЯТЕФЙЄГЬЁЃ етИіР§ГЬЕФЖЅВудДТыРяга3ИіНгПкЃЌМДЃК input ext_clk_25m, //ЭтВПЪфШы25MHzЪБжгаХКХ input ext_rst_n, //ЭтВПЪфШыИДЮЛаХКХЃЌЕЭЕчЦНгааЇ output reg beep //ЗфУљЦїПижЦаХКХЃЌ1--ЯьЃЌ0--ВЛЯь ет3ИіаХКХЖМЪЧFPGAв§НХЩЯЖЈвхКЭЭтВПЩшБИСЌНгЕФаХКХЃЌвђДЫЮвУЧашвЊНЋетаЉаХКХКЭFPGAЕФв§НХНјаагГЩфЁЃ ШчЭМЫљЪОЃЌЕуЛїISEВЫЕЅЩЯЕФЁАTools ЈЄ PlanAhead ЈЄ I/O Pin Planning(PlanAhead) ЈC Pre-SynthesisЁЁБбЁЯюЁЃ

ШєЕЏГіШчЯТВЫЕЅЃЌЕуЛїЁАYesЁБМЬајЁЃ

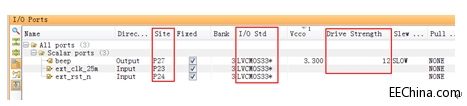

ШчЭМЫљЪОЃЌдкPlanAeadНчУцзюЯТУцГіЯжСЫЁАI/O PortsЁБСаБэжаЃЌгаЮвУЧЕФ3ИіаХКХНгПкЃЌетРяЁАSiteЁБвЛСаПЩвдЪфШыЫќУЧЖдгІFPGAЕФв§НХЃЛЁАI/O StdЁБвЛСаПЩвдЪфШыI/OЕчЦНБъзМЃЛЖдгкЪфГіаХКХЃЌЁАDrive StrengthЁБвЛСаЛЙПЩвдЩшжУЪфГіЧ§ЖЏЕчСїЧПЖШЁЃ

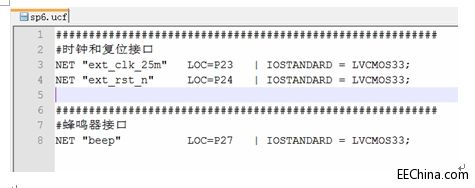

ВщПДSF-SP6ПЊЗЂАхЕФдРэЭМЃЌШчЭМЫљЪОЃЌетРяBEEPЖдгІFPGAв§НХКХЪЧ27ЃЌФЧУДЧАУцЮвУЧОЭдкSiteСаЪфШыP27ЃЛRST_NКЭCLK_25MЗжБ№ЮЊ24КЭ23ЃЌдђЪфШыP24КЭP23ЁЃ

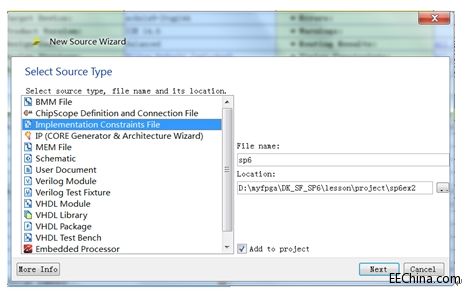

ЭъГЩЗжХфКѓЃЌБ№ЭќМЧБЃДцКѓЭЫГіPlanAeadНчУцЁЃ Г§СЫЪЙгУPlanAeadетжжЭМаЮНчУцЗНЪНЗжХфв§НХЃЌвВПЩвджБНгЪЙгУНХБОгяЗЈЗжХфв§НХЁЃЯТУцЯШаТНЈетИіНХБОЮФМўЃЌМДucfЮФМўЃЌЮвУЧЧАУцдкPlanAeadНчУцЗжХфЕФв§НХаХЯЂвВЛсДцДЂдкетИіucfЮФМўжаЁЃ дкЁАDesign ЈЄImplementation ЈЄ HierarchyЁБЕФШЮвтПеАзДІЕЅЛїгвМќЃЌбЁдёЁАNewSourceЁЁБЃЌШчЭМЫљЪОЁЃ

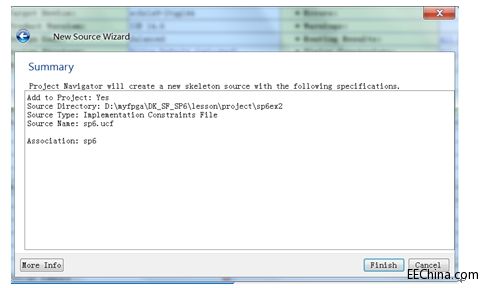

ШчЭМЫљЪОЃЌбЁдёЁАImplementation Contraints FileЁБЃЌЪфШыЮФМўУћКЭТЗОЖЃЌШЛКѓЕуЛїЁАNextЁБЁЃ

НгзХЕЏГіБЈИцЃЌЕуЛїЁАFinishЁБЭъГЩДДНЈЁЃ

ШчЭМЫљЪОЃЌДЫЪБЕФsp6.vЯТУцЖрСЫвЛИіsp6.ucfЮФМўЃЌбЁжаЫќЃЌНгзХдкProcessesЯТУцЫЋЛїЁАEditConstraints(Text)ЁБЁЃ

ISEЛсЕїгУNotepad++ДђПЊsp6.ucfЮФМўЃЌШчЭМЫљЪОЃЌетРяЕФНХБОКЭЮвУЧЧАУцЪЙгУPlanAheadНјааЕФв§НХЗжХфдМЪјЪЧвЛбљЕФЁЃ

|

ЭјгбЦРТл