Xilinx FPGAШыУХСЌди10ЃКModelsimЗТецбщжЄ

ЗЂВМЪБМфЃК2015-9-25 11:40

ЗЂВМепЃКrousong1989

|

Xilinx FPGAШыУХСЌди10ЃКModelsimЗТецбщжЄ ЬиШЈЭЌбЇЃЌАцШЈЫљга ХфЬзР§ГЬКЭИќЖрзЪСЯЯТдиСДНгЃК http://pan.baidu.com/s/1jGjAhEm

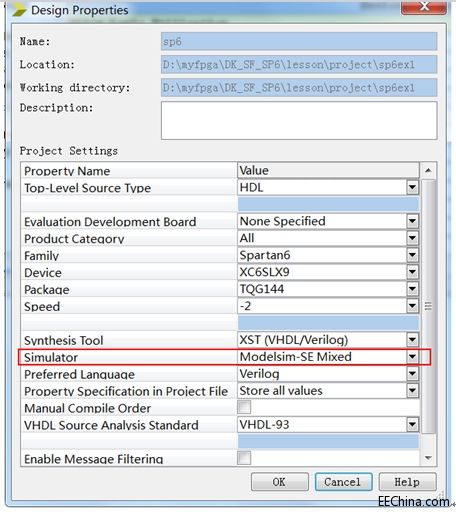

КУЃЌМШШЛЮвУЧЕФгяЗЈМьВщЭЈЙ§СЫЃЌФЧУДНгЯТРДЮвУЧВЛЗСаЁЪдХЃЕЖЃЌШУЗТецЙЄОпModelsimРДЪфГіВЈаЮбщжЄЩшМЦНсЙћКЭЮвУЧЕФдЄЯыЪЧЗёвЛжТЁЃ дкгУModelsimЗТецЧАЃЌдкISEжаашвЊШЗШЯМИИіЩшжУЁЃ 1. ШчЭМЫљЪОЃЌЕуЛїВЫЕЅЕФЁАProjectЈЄ Design PropertiesЁЁБЁЃ

ШчЭМЫљЪОЃЌШЗШЯетРяЁАSimulatorЁБЕФбЁдёЮЊЁАModelsim-SEMixedЁБЃЌетдкаТНЈЙЄГЬЪБЮвУЧвбОЩшЖЈКУСЫЃЌЮЊБЃЭђЮовЛЪЇЃЌЮвУЧЛЙЪЧШЗШЯвЛЯТЁЃ

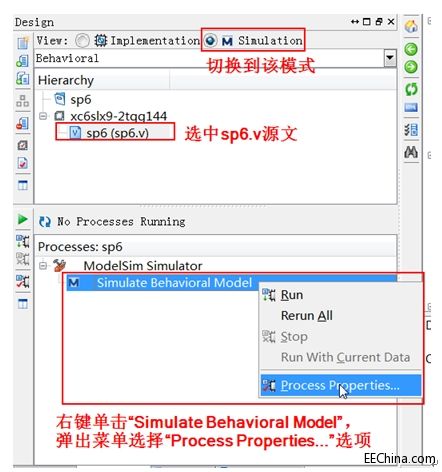

2. ШчЯТЭМЫљЪОЃЌДгЩЯЕНЯТвРДЮжДаа3ВНВйзїЁЃ

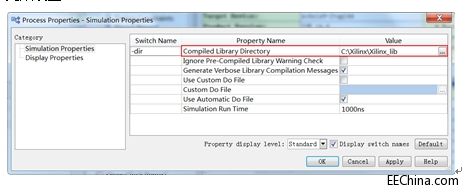

ЕЏГіЁАProcess PropertiesЁБЩшжУДАПкЃЌдкгвБпЕФЁАCompiled Library DirectoryЁБКѓУцЬюШыжЎЧАБрвыПтЪБЩшжУЕФвбБрвыПтЕФТЗОЖЃЌЕуХдБпЕФЁАЁЁБАДХЅРДбЁЖЈвВааЁЃЮвУЧЧАУцlessonжаНЋПтТЗОЖЩшжУЮЊЁАC:\Xilinx\Xilinx_libЁБЃЌвђДЫетРявВетУДЩшжУЁЃЦфЫћбЁЯюФЌШЯЩшжУМДПЩЃЌЕуЛїЁАOKЁБ ЭъГЩЩшжУЁЃ

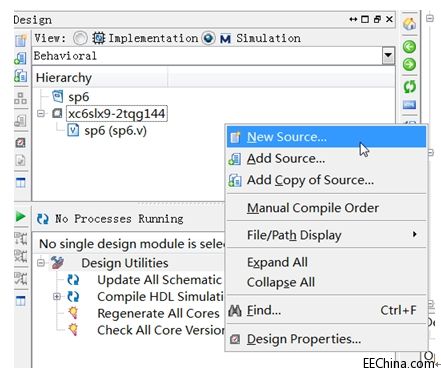

ЛиЕНЁАSimulation ЈЄ HierarchyЁБДАПкжаЃЌдкШЮвтПеАзДІЕЅЛїгвМќЃЌЕЏГіВЫЕЅжабЁдёЁАNew SourceЁБЃЌШчЭМЫљЪОЁЃ

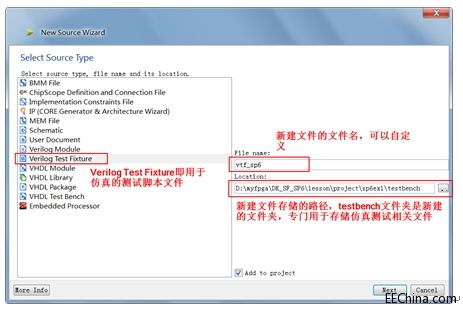

ШчЭМЫљЪОЃЌбЁдёаТНЈдДЮФМўРраЭЪЧЁАVerilog Test FixtureЁБЃЌдкЙЄГЬТЗОЖЯТаТНЈвЛИіУћЮЊЁАtestbenchЁБЕФЮФМўМаЃЌЭЌЪБНЋаТНЈЮФМўЕФТЗОЖЖЈЮЛЕНетИіЮФМўМаЯТУцЁЃКЭЧАУцЕФlessonаТНЈsource_codeЮФМўМаЕФГѕждвЛбљЃЌаТНЈtestbenchЮФМўМаЕФФПЕФвВжЛЪЧЮЊСЫБугкЮФМўЕФЗжРрКЭЙмРэЁЃЛЙгаЁАAdd to projectЁБЭЈГЃБиаыЙДбЁЩЯЃЌФЌШЯМДЙДбЁЁЃЕуЛїЁАNextЁБЕНЯТвЛВНЁЃ

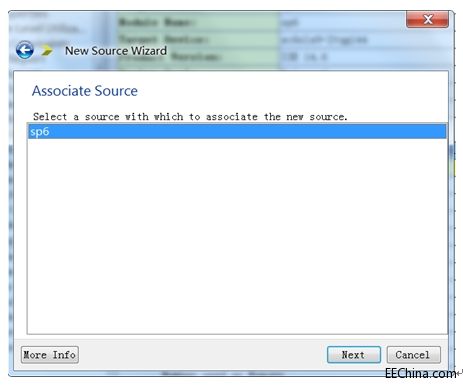

етРяЁАAssociate SourceЁБЪЧбЁдёВтЪдНХБОЖдгІЕФЩшМЦдДЮФМўЃЌЮвУЧжЛгавЛИіЩшМЦдДЮФМўЃЌФЧОЭБ№ЮобЁдёСЫЃЌбЁжаsp6.vЃЌШЛКѓЕуЛїЁАNextЁБЁЃ

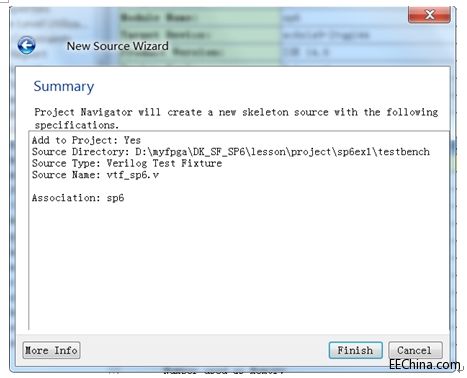

ШчЭМЫљЪОЃЌТоСаГіЧАУцЩшжУЕФБЈИцЃЌУЛЮЪЬтОЭЕуЛїЁАFinishЁБЭъГЩЮФМўДДНЈЁЃ

ШчЭМЫљЪОЃЌВтЪдНХБОЮФМўдкNotepad++жаДђПЊСЫЁЃетРяЕФВтЪдНХБОжЛЪЧвЛИіЛљБОЕФФЃАхЃЌЫќАбЩшМЦЮФМўsp6ЕФНгПкдкетИіФЃПщРяУцР§ЛЏЩъУїСЫЃЌЮвУЧЛЙашвЊздЖЏЖЏЪжЬэМгИДЮЛКЭЪБжгЕФМЄРјЁЃ

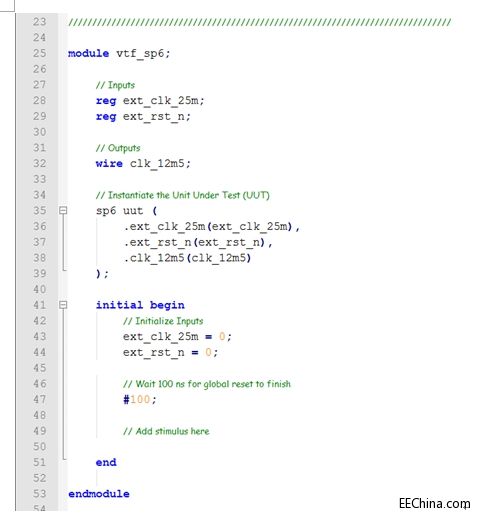

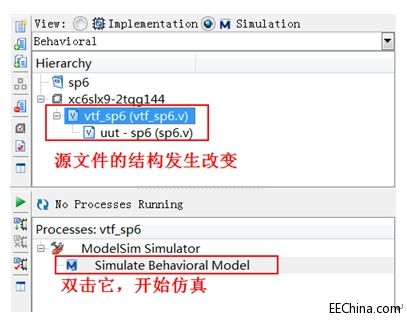

гаХѓгбПЩФмЪЧЕквЛДЮНгДЅВтЪдЗТецЃЌЙигкЗТецЕФЛљБОИХФюЧыВщПДЁЖFPGAЩшМЦЪЕеНбнСЗЃЈТпМЦЊЃЉ- ch9 - ЩшМЦЗТец.pdfЁЗЁЃ Vtf_sp6.vЮФМўашвЊзівЛаЉБрМЃЌдіМгИДЮЛКЭЪБжгаХКХЃЌаоИФКѓДњТыШчЯТЁЃ module vtf_sp6; // Inputs reg ext_clk_25m; reg ext_rst_n; // Outputs wire clk_12m5; // Instantiate the Unit Under Test(UUT) sp6 uut ( .ext_clk_25m(ext_clk_25m), .ext_rst_n(ext_rst_n), .clk_12m5(clk_12m5) ); initial begin // Initialize Inputs ext_clk_25m = 0; ext_rst_n = 0; // Wait 100 ns for globalreset to finish #100; ext_rst_n = 1; // Add stimulus here #2000; $stop; end always #20 ext_clk_25m = ~ ext_clk_25m; //ВњЩњ25MHzЪБжгдД endmodule БЃДцаоИФКѓЕФДњТыЁЃЮвУЧЛиЕНISEжаЁЃ ДЫЪБЃЌШчЯТЭМЫљЪОЃЌvtf_sp6.vвбОГЩСЫетИіЗТецHierarchyЕФЖЅВуСЫЃЌЫќЯТУцЪЧЩшМЦЮФМўsp6.vЁЃЮвУЧбЁжаvtf_sp6.vЮФМўЃЌШЛКѓЫЋЛїЁАSimulation Behavioral ModelЁБЃЌЫцКѓModelsimНЋБЛЕїгУЃЌЦєЖЏЗТецЁЃ

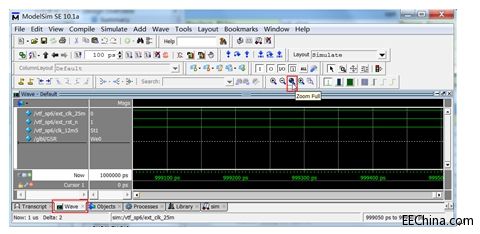

ЕЏГіModelsimКѓЃЌЮвУЧПЩвдДђПЊWaveВщПДЃЌЭЌЪБЕуЛїЁАZoom FullЁБАДХЅЃЌModelsimЕФЪЙгУВЂВЛФбЃЌДѓМввЊЖрЖЏЪжЃЌЫљгаЕФВЫЕЅАДХЅЖММђЕЅвзЖЎЃЌгааЉЕиЗНгвМќВЫЕЅвВгаКмЖрЙІФмЃЌШчЙћетРявЛвЛНщЩмПжХТашвЊвЛБОЪщЃЌЫљвдДѓМвздЖЏЖЏЪжЃЌЙѓдкГЂЪдЃЌКмПьОЭЛсЩЯЪжЁЃ

ШчЭМЫљЪОЃЌетБуЪЧЮвУЧЩшМЦЕФЖўЗжЦЕаЇЙћЁЃ

дѕУДбљЃЌЭЈЙ§етИіМђЕЅЕФЙЄГЬЃЌДѓМвЪЧВЛЪЧеЦЮеСЫЪЙгУISEНјааЙЄГЬДДНЈЁЂЩшМЦЮФБОДДНЈКЭБрМЁЂВтЪдНХБОДДНЈКЭБрМЁЂЪЙгУModelsimНјааЗТецЕШЛљБОЕФММФмЁЃЕБШЛСЫЃЌетжЛЪЧИеИеАбФњСьНјУХЃЌШУФњЪьЯЄвЛЯТЙЄОпЕФвЛаЉЛљБОВйзїЁЃетИіР§ГЬОЭЕНетРяЃЌЮвУЧВЛЭљЯТНјааАхМЖЕФЪЕбщЃЌДѓМвМЬајИњзХНЬГЬЭљЯТЃЌИУеЦЮеЕФЖМЛсеЦЮеЕЮЁЃ |

ЭјгбЦРТл