MIMO 系统的快速原型设计与验证

发布时间:2010-7-15 22:23

发布者:conniede

|

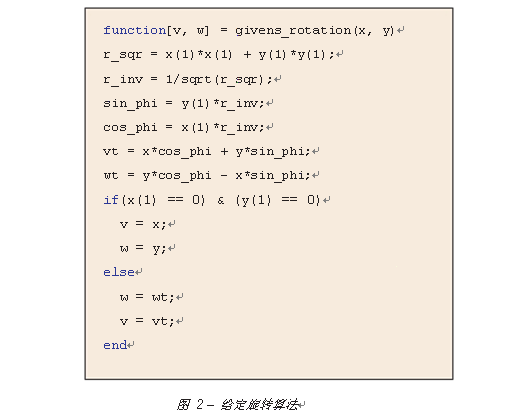

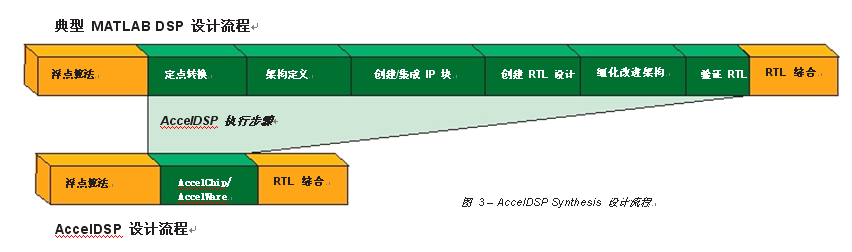

空间复用式多输入多输出 (MIMO) 发射器与接收器据称可比其现有的单输入单输出 (SISO) 对应器件提升更大的无线通信系统性能。下一代无线标准,如 802.11n,将支持高达 600 Mbps 数据传输速率和超过 1 GHz 的无线局域网传输速率。 然而这些系统的设计,却必须在成本和功耗方面做出折衷,这对使用电池运行的手持设备具有重要影响。设计团队需要面对的挑战就是针对他们的特定应用寻求这些设计要求之间的最佳平衡。 此项技术的核心是多径概念,即射频 (RF) 信号在物理环境中的反射。虽然多径问题降低了现有的 802.11 设备的性能,但空间复用式正交频分复用 (OFDM) MIMO——802.11n 标准中的一个关键要素——却利用了这些反射来“调谐”发射器,最大程度地减小误差,和提高总体性能。但在这些带宽上,位于传输路径中的物体对微波的散射、衍射和吸收是一个重要的考虑因素。设计 MIMO 系统时要求将这些影响尽可能精确地以信道模型的形式描绘出来。 有三种基本的信道模型来源:基于软件的数学模型,一般来自标准委员会;基于硬件的 MIMO 信道模拟器,自行设计或由 诸如 Azimuth 之类的公司提供;最好的则是MIMO 系统将要运行的真实世界环境。在真实世界中验证 MIMO 系统,要求能够在面向 MIMO 的 FPGA 硬件平台上,如 Lyrtech 公司的 VHS-ADC-V4 卡,快速构建起发射器和接收器原型。 MIMO 性能优点 空间复用式 MIMO 技术的优点是能够通过天线的数量提高传输速度。目前已有 SISO 系统的数据速率由以下公式决定: R = Es * Bw 其中 R 为数据速率(位/秒),Es 为频谱效率(位/秒/赫兹),Bw 为通信带宽 (Hz)。例如,对于 802.11a 标准,峰值数据速率由以下公式决定: Bw = 20 MHz Es = 2.7 bps/Hz R = 54 Mbps 使用 MIMO 时,需要为该公式引入一个附加变量 “Ns”,它代表使用相同带宽而通过不同空间路径同时发射的独立数据流的数量。现在频谱效率将按传输/流 Ess 来计算,于是 MIMO 系统的数据速率变为: R = Ess * Bw * Ns 我们把以前 802.11a 的例子和当前 802.11n 提案所能获得的结果进行一次比较,采用 20 MHz 带宽和四个天线: Bw = 20 MHz Ess = 3.6 bps/Hz Ns = 4 R = 288 Mbps MIMO 技术的使用让所体案的802.11n标准实现了 5.3 倍数据速率的提升。 MIMO 系统硬件复杂度 空间复用式 MIMO 系统的性能提升是以增加硬件复杂度为代价获得的。采用多个天线的发射/接收系统不只在相应天线之间发射数据,而且还在相邻天线之间发射数据。在图 1 中您可以看到,数据是以“MIMO 信道矩阵”的形式接收的。 在空间域对信道矩阵进行去耦,并恢复发射的数据过程中,需要使用到线性几何技术如奇异值分解 (SVD) 或矩阵求逆等。对 802.11g 标准的后向兼容性要求使 802.11n 标准的天线数量限制为两个或四个,从而使信道矩阵的尺寸限制为 2 x 2 或 4 x 4。 在硬件上开发执行实际系统数据速率的 MIMO 系统原型需要使用基于 FPGA 的硬件平台。赛灵思® Virtex™-4 系列 FPGA 通过提供多达 512 个可执行并行运算的硬件乘法器,对此类应用提供了远远优于 DSP 处理器的性能。但是在设计这种原型系统时,您将面对两项较大挑战:第一项挑战是要使用硬件来设计象 SVD 或矩阵求逆那样复杂的东西,第二项挑战是调整实现,使之达到最优性能。 FPGA 上实现矩阵运算 实施中选择专用 SVD 或矩阵求逆算法将是数值稳定性和硬件效率之间的折衷。您需要开发一个高级 MATLAB 模型来确定适合某个特定应用的最高效的算法。 对于 SVD 的情况,这可能涉及到在适应估计技术、矢量旋转或其他因具有对称等特性的信道矩阵而产生的简化技术之间进行选择。 一旦最终确定算法,您将需要调整硬件性能,使之符合总体系统要求。在硬件上实现 MIMO 系统性能的最大化,要求在设计中将会对总体性能产生最大影响的关键地方采用部分并行乘法运算来实现。图 2 中所示的给定旋转算法,给出了通过并行乘法运算实现性能提升的一个良好范例。  通过使用 MATLAB 算法作为 FPGA 开发的金色源码和免除重新编写为其他语言或设计环境的工作,减少了开发和验证的循环次数。给定旋转通常用于解决对称特征值问题,并且是 QRD 矩阵求逆的关键构造块。 您可以使用乘法器或 CORDIC 近似法来实现该算法。赛灵思 AccelDSP™ Synthesis 综合工具的设计探索功能被用于通过向架构中嵌入并行机制而无需重写代码来提高性能。如表 1 所示,这种方法可以获得比并行 CORDIC 实现高达 10 倍的性能提升。基于给定旋转的算法近来受到更大的关注,因为它们本身很适合并行实现。  一种基于 MATLAB 的 FPGA 设计流程 The MathWorks 公司的 MATLAB 为空间复用式 MIMO 系统的设计和实现提供了一个真正独一无二的环境。对循环、复数、矢量和矩阵运算的内在语言支持,以及数学函数,为 MIMO 所需的线性几何算法提供了一种高效的建模环境。 图 3 演示了 AccelDSP Synthesis 综合工具的优点, 包括使用浮点 MATLAB 在 FPGA 上为空间复用式 MIMO 系统定义和实现定制架构的灵活性。  浮点到定点的自动转换功能,可以帮助解决由线性几何函数如 SVD 等的迭代性质而产生的复杂的量化问题。一旦您确定了可接受的定点模型,您就可以通过算法综合快速地探讨性能和硬件之间的折衷,快速地增加专用硬件乘法器的数量以提高性能和充分利用 Virtex-4 架构的灵活性。 从 AccelDSP Synthesis 生成的 RTL 自动针对金色源码 (golden-source) MATLAB 进行验证,以确位真 (bit-true) 功能正确性。 结论 通过在信道矩阵 DSP 硬件开发中采用基于 MATLAB 的设计流程,极大地简化了用于真实世界验证的空间复用式 MIMO 系统的原型设计。通过使用 MATLAB 算法作为 FPGA 开发的金色源码和免除重新编写为其他语言或设计环境的工作,减少了开发和验证的循环次数。此外,MATLAB 的高级性质还使得 AccelDSP Synthesis 综合工具能够快速探索适合一个算法的硬件替代方法,包括 DSP 块、RAM 和流水线的使用。 AccelDSP Synthesis 综合工具和 Lyrtech 原型设计环境均含有到 Xilinx System Generator for DSP 设计环境的接口,以提供一种自动化的 MATLAB 到原型设计的设计流程。 |

网友评论