FPGA实战演练逻辑篇57:VGA驱动接口时序设计之4建立和保持时间分析

发布时间:2015-8-2 19:02

发布者:rousong1989

|

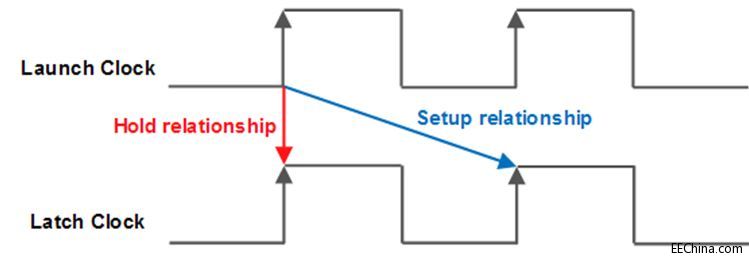

VGA驱动接口时序设计之4建立和保持时间分析 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt 下面我们可以简单的来分析一下数据的建立时间和保持时间应该满足怎样的关系才能保证被时钟lcd_clk稳定的锁存到ADV7123芯片中。首先,我们需要来看看这个实例的时钟launch edge和latch edge的概念。如图8.31所示,这是一个源寄存器和目的寄存器传输时钟一致的理想路径,他们所对应的launch edge和latch edge的示意。我们可以这么理解,对于setup时间,launch edge是latch edge的上一个时钟节拍,latch edge通常是要去采样launch edge已经采样过的数据。而对于hold时间,launch edge和latch edge通常是同一个时钟沿,latch edge的hold时间不被冒犯,也就意味着latch edge不采样它前一拍的数据。(特权同学,版权所有)

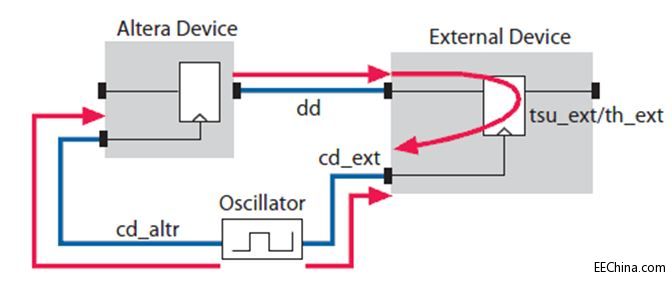

图8.31 时钟launch edge和latch edge 对于建立时间,有基本的时序关系需要满足,其公式如下: Launch edge + Tc2t + Tco + Tr2p+Tdpcb < latch edge + Tc2r - Tsu 对于保持时间,有基本的时序关系需要满足,其公式如下: Launch edge + Tc2t + Tco + Tr2p +Tdpcb> latch edge + Tc2r + Th 前面我们已经约束好了源时钟和目的时钟(虚拟时钟),因此,latch edge和launch edge都是FPGA已经明确的时序参数。同样的,Tco、Tc2t、Tr2p和Tc2r的FPGA内部的延时,也都是FPGA能够本身就能够确定的,并且FPGA会通过设计者的约束,来控制这些内部的时序延时,使得前面给出的两个基本公式得到满足。但是,FPGA并不知道这两个公式中FPGA外部的路径延时参数,所以我们下一步的数据路径约束要做的就是把这些参数告诉FPGA。Quartus II软件内部集成的TimeQuest中的set output delay约束的功能就是要传递这个信息。我们下面来看看set output delay的值如何计算。(特权同学,版权所有) 如图8.32所示,这是Altera的Handbook给出了set output delay的max和min值计算方法。

图8.32 Altera官方给出的reg2pin时序分析模型 这个路径中,output delay参数值的计算公式如下: output delay max = dd_max + tsu_ext +(cd_altr_min - cd_ext_max) output delay min = dd_min – th_ext +(cd_altr_max – cd_ext_min) 都说具体问题具体分析,如果我们不问青红皂白,依葫芦画瓢的照搬这个模型的公式进行计算,我们往往要碰一鼻子灰,很多参数我们可能找不到或者找错了。那么,对于每一个特定的路径,我们往往需要根据实际情况进行适当的变通,万变不离其宗,reg2pin的分析原理和官方给出的这个模型肯定是一致的。下面我们变通一下,看看我们的实例又是如何做分析的。(特权同学,版权所有) |

网友评论