使用HART兼容性简化模拟电流环路设计

发布时间:2015-7-17 14:01

发布者:看门狗

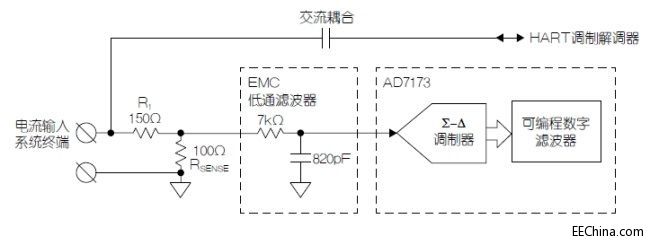

在工厂环境中,4mA至20mA模拟电流环路很常见。虽然各种应用中的基本信号调制均相同,但带宽要求却有很大的不同。工厂控制系统可能需要几百Hz环路带宽(来自位置和位移传感器),而典型的过程控制系统仅需几Hz更新速率,且一般都支持HART(可寻址远程传感器高速通道)。HART协议允许在传统的模拟4mA至20mA电流环路内实现双向1.2/2.2 kHz FSK(频移键控)调制数字通信。设计同时满足两种情况的4mA至20mA输入可能会有一定难度。图1中的电路图是一个支持HART的模拟输入的传统部署方法。

图1:集成无源滤波器且支持HART的输入。 图中,R1和RSENSE组成一个250Ω系统端接阻抗。HART FSK信号从该处到HART调制解调器为交流耦合。通过精密100Ω的RSENSE电阻,将4mA至20mA模拟信号转换为0.4V至2V信号。然后,模拟低通滤波器衰减模拟信号中的HART FSK成分,接着将其输入ADC。二阶低通模拟滤波器带宽为25Hz,滚降为-40dB/十倍频程。该电路符合HART规范,可将HART FSK信号衰减至4mA至20mA满量程以下超过-60dB电平,确保HART FSK通信输入扰动不超过0.1%。 另一方面,该模拟低通滤波器在系统输入端的满量程跳变之后,建立至0.1%以内需大约70ms。这种较长的建立时间和低带宽性能不适合要求高速工作且不需要HART通信的系统。确实可以旁路模拟滤波器,但需要额外的模拟电路,比如开关或多路复用器。图2显示了支持HART的模拟输入的替代方案。

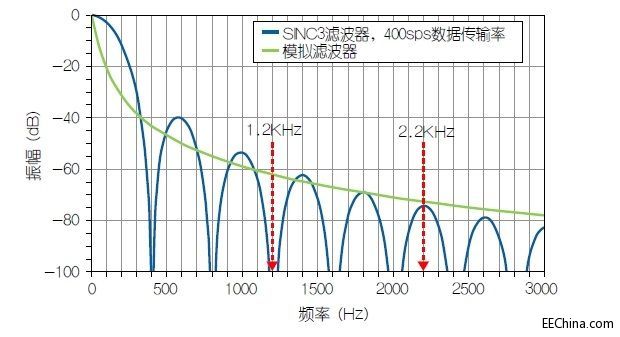

图2:支持HART的灵活带宽输入。 与上一个电路类似,HART FSK信号交流耦合至250Ω输入阻抗,而4mA至20mA信号通过100Ω的精密RSENSE电阻转换为0.4V至2V信号。然而本电路中,一个轻度的低通滤波器将信号带宽限制为27kHz左右,以便为系统提供免疫性和电磁兼容性(EMC)。系统输入端满量程跳变后,滤波器在40μs时间内建立至0.1%。 信号会被传递到带有内置数字滤波器的Σ-Δ型ADC,比如 ADI公司的AD7173。数字滤波器可编程设置为较慢的工作速度模式和最优HART FSK信号抑制模式,或者在要求快速模拟输入时设置为快速工作模式。 AD7173支持多种工作模式。其中一种模式适合用来抑制HART FSK信号,将SINC3滤波器的陷波频率设为400Hz,或者可在较低HART FSK频率(1.2kHz)时提供深滤波器陷波并可在较高频率(2.2kHz)时提供大幅衰减的分数频率。图3中的曲线显示该数字滤波器的频率响应,及其与图1中模拟滤波器的比较。

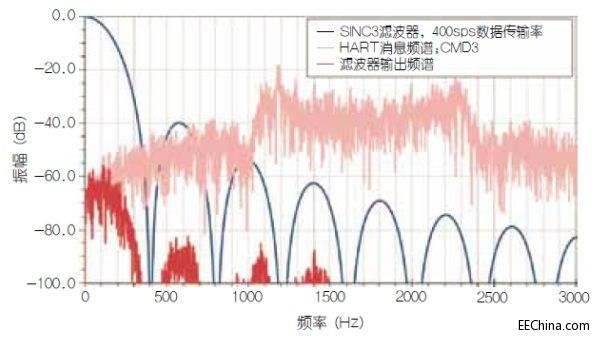

图3:集成无源滤波器且支持HART的输入。 不幸的是,真实情况远没有那么简单。当一条完整的消息经过HART发送后,HART FSK调制信号频谱不仅在基频调制频率处包含电能,且在1.2kHz与2.2kHz载波之间、下方和上方包含频率分量。图4显示了HART FSK消息在ADC输入端的典型频谱,以及通过SINC3滤波器以400Hz陷波衰减时的频谱。本例中,主机发送HART命令3,从机响应该命令。

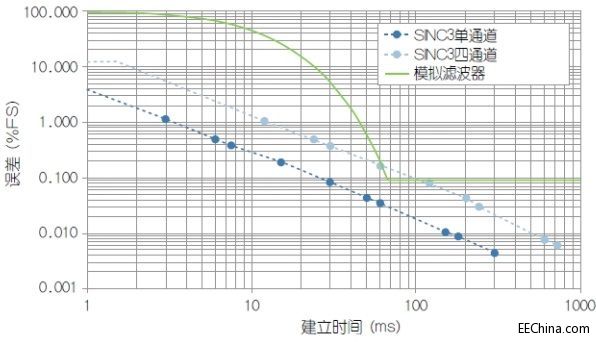

图4:HART消息频谱。 由图4可以看出,HART消息的一部分(尤其在较低频率处)依然可以出现在A/D输出数据中。也就是说,可以轻松更改数字滤波器设置,以便实现HART FSK采样输入速度和抑制之间的正确平衡。图5显示了系统性能,其测量值在4mA至20mA满量程范围内以百分比误差表示,同时比较模拟滤波器(图1)和SINC3数字滤波器(图2)的系统速度。

图5:SINC3滤波器与模拟滤波器。 模拟滤波器在硬件中固定,并具有固定的建立时间。对于系统输入端的快速变化模拟信号而言,模拟滤波器输出误差由其较慢的建立时间决定。例如,如果系统输入每40ms改变满量程,则滤波器输出不会建立至正确值1%以内。对于较慢的输入信号而言,模拟滤波器输出误差由其抑制HART FSK信号低频分量的能力决定。对于典型HART命令3消息而言,该误差测量值约为4mA至20mA满量程的0.09%。 此外,数字SINC3滤波器的建立时间是一个用户设置的参数,滤波器输出误差是由于HART FSK调制对应的滤波器设置决定的。例如,400 Hz陷波的SINC3滤波器对应7.5ms建立时间,当传输HART命令3时,A/D上测得的扰动不足4mA至20mA满量程的0.4%。在具有四个模拟输入的系统中,SINC3滤波器在通道之间顺序切换。同样的400Hz陷波SIN3滤波器现在需要4×7.5= 30ms才能扫描全部四个通道。这便是四通道系统的曲线在30ms处均显示出约为0.4%误差的原因。 对于更精确的4mA至20mA输入而言,SINC3滤波器可设为30ms建立时间,该设置对应100Hz陷波且将HART信号抑制在不足满量程的0.1%。如果速度更为重要,则6ms建立时间(约500Hz陷波)的SINC3滤波器依然可以将HART通信信号抑制在4mA至20mA输入的0.5%以下。此外,如果只要求速度且无需进行HART通信,则前文提及的AD7173能够以每通道161μs的建立时间达到3 ksps的采样速率。 传统的模拟低通滤波器较容易理解,而某些情况下,每通道略为增加几个元器件可在多通道系统中实现较好的模拟输入性能。另一方面,Σ-Δ型ADC的集成数字SINC滤波器具有极大的灵活性,而这种灵活性是一路直到终端系统用户都可提供的。数字解决方案所需硬件较少,并且若设置得当,则其在HART FSK信号滤波性能方面优于单通道系统中的模拟解决方案,而与最多四通道的系统相比具有接近或更佳的性能。 |

网友评论