НЕЕЭSoCжаЛЅСЌВПЗжЕФЙІКФ

ЗЂВМЪБМфЃК2015-7-17 11:36

ЗЂВМепЃКПДУХЙЗ

|

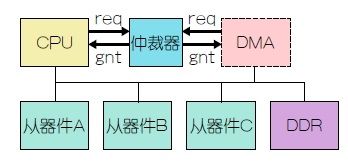

зїеп: Jonah Probell,Arteris ЫфШЛЖдЯЕЭГМЖаОЦЌПЊЗЂШЫдБРДЫЕЕчдДЙмРэЕФживЊаддНРДдНИпЃЌЕЋгаИіЙиМќЧјгђОГЃБЛКіЪгЃЌФЧОЭЪЧЛЅСЌЁЃЫфШЛДѓЖрЪ§ЕчдДЙмРэЙЄзїМЏжагкSoCЕФдЫЫуВПЗжЃЌЕЋВЩгУИќМгФЃПщЛЏЛЅСЌЕФЩшМЦЪІПЩвдМѕаЁТуЦЌГпДчЁЂМѕЧсВМЯпгЕШћЃЌетОЭПЩвдНЋзмЕФаОЦЌЙІКФзюЖрНЕЕЭДя0.7mwЁЃШчДЫЯджјЕФЙІКФЯТНЕНЋГЩЮЊЯТвЛДњвЦЖЏКЭЙІКФУєИаадЪ§ОнжааФгІгУЯЕЭГжаЕФгЮЯЗЙцдђИФБфепЁЃ ФЃПщЛЏИХФюгаБ№гкЦфЫќРраЭЕФЛЅСЌЃЌвђЮЊЫќгЩЗжВМЪНМмЙЙЕФПЊЙиЁЂЛКГхЦїЁЂЗР Л№ ЧНЁЂЙмЯпНсЙЙвдМАЪБжгКЭЕчдДгђНЛВцзщГЩЁЃЭЈЙ§дкаОЦЌЩЯЕФЫљгаЖРСЂЕЅдЊжЎМфЪЙгУЭЈгУДЋЪфавщЃЌФЃПщЛЏЗНЗЈПЩвдАяжњЩшМЦЪІЪЕЯжЕЅдЊМЖЪБжгбЁЭЈЃЌДгЖјЯћГ§УЛгаЪТЮёДІРэЧјгђЕФЪБжгЪїПЊЙиЙІКФЁЃ ФЃПщЛЏЦЌЩЯЭјТчМЖаОЦЌ(NoC)ММЪѕЛЙФмЭЈЙ§ТпМОжВПЛЏЁЂОЁСПЫѕЖЬГЄЕФзпЯпВЂБЃГжЕЭЕчШнРДНЕЕЭЙІКФЁЃЯывЊНјвЛВНдіЧПSoCЩшМЦЕФЕчдДЙмРэФмСІЕФЩшМЦЪІПЩвдВЩШЁвЛЖЈЕФДыЪЉМѕаЁаОЦЌЕФУцЛ§КЭаЙТЉЙІКФЃЌЗНЗЈЪЧЪЙгУNoCДЋЪфавщЕФМђвзадЪЕЯжЪ§ОнТЗОЖЕФДЎааЛЏЃЌНјЖјзюДѓГЬЖШЕиМѕЩйТпМгУСПЁЃ ЕЭЙІКФ ФПЧАГЃгУЕФЖЅВуЛЅСЌНсЙЙвЛАуЖМвЊвРРЕгкНЯГЄЕФзпЯпЃЌЖјетаЉзпЯпЛсЯћКФгыЫќУЧдкаОЦЌЩЯеМгУЕФТпМЧјгђУцЛ§ВЛГЩБШР§ЕФЙІКФЁЃЪБжгЪїЭЈГЃЪЧЛЅСЌФкзюДѓЕФЙІКФдДЃЌЖјЪБжгбЁЭЈЬсЙЉСЫНЕЕЭЙІКФЕФзюДѓЧБСІЁЃСэЭтЃЌТЉЕчЙІКФЪЧЕкЖўДѓЙІКФдДЃЌМѕаЁетжжНсЙЙЫљашЕФТпМУцЛ§ПЩвдзюДѓЯоЖШЕиМѕаЁТЉЕчЙІКФЁЃ ВЩгУФЃПщЛЏNoCЛЅСЌЕФЩшМЦЪІПЩвдДгБОЮФжаСЫНтЕНЪБжгЪїЙмРэЕФОжВПЛЏЁЂЪ§ОнТЗОЖЕФДЎааЛЏКЭОЋШЗЖЈЮЛЕФЙмЯпНсЙЙЫљДјРДЕФЙІКФКЭУцЛ§ЗНУцЕФКУДІЁЃ змЯпКЭНЛВцОиеѓЃКЛЅСЌРњЪЗМђНщ СЫНтЛЅСЌНсЙЙЕФРњЪЗОЭФмжЊЕРФЃПщЛЏNoCЩшМЦЕФгЩРДСЫЃЌЫќФмНтОіПЩРЉеЙадЮЪЬтЁЃ SoCЪЧвЛжжКЌCPUКЭЭтЩшЕФаОЦЌЃЌПЊЗЂШЫдБЬсГіЕФНгПкавщБъзМПЩвдНЋИїЕЅдЊСДНгдквЛЦ№ЁЃНшжњаТдізмЯпжїЦїМўЕФЭЦГіЃЌЕНЭтЩшЕФСЌНгПЩвдЕУЕНЙВЯэЁЃПижЦЖдзмЯпЕФЗУЮЪвЊЧѓвЛИіжабыжйВУЦїЃЌБШШчдкАхМЖавщжаЪЙгУЕФжйВУЦїЁЃ

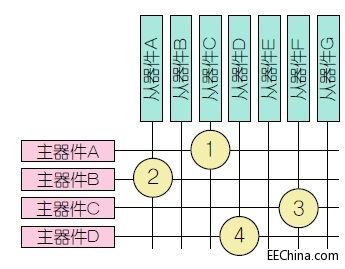

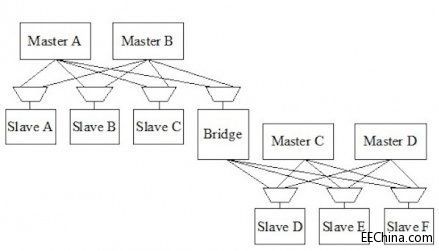

ЭМ1ЃКДјжйВУЦїЕФЙВЯэаЭзмЯпеЙЪОСЫЗУЮЪПижЦЮЊКЮвЊЪЙгУжабыжйВУЦїЁЃ ЫцзХЪБМфЕФЭЦвЦЃЌSoCЩшМЦдіМгСЫдНРДдНЖрЕФIPФкКЫЁЃгЩгкетаЉЩшМЦБфЕУдНРДдНИДдгЃЌЫћУЧвЊЧѓИќЖрЕФзмЯпНгПкЁЃЕБЖдНгПкНјааУмМЏВйзїЪБЃЌзмЯпжїЦїМўПЩФмЛсРЫЗбКмЖрЪБМфЕШД§ЖдзмЯпЕФЗУЮЪШЈЃЌМДЪЙдкВЛЭЌЕФжїЦїМўЧыЧѓВйзїВЛЭЌЕФДгЦїМўЪБЃЌвВЪЧШчДЫЁЃ ЮЊСЫНтОіЕШД§бгЪБЮЪЬтЃЌНЛВцОиеѓПЊЙигІдЫЖјЩњЃЌЫќУЧжЇГждкЦЌЩЯЛЅСЌФкВЛЭЌЕФжїКЭДгЦїМўжЎМфПЊеЙВЂааЗУЮЪЁЃЯТУцетИіТпМПђЭМЯдЪОСЫ4ИіжїЦїМўЭЌЪБЖд4ИіВЛЭЌДгЦїМўНјааЪТЮёВйзїЁЃ

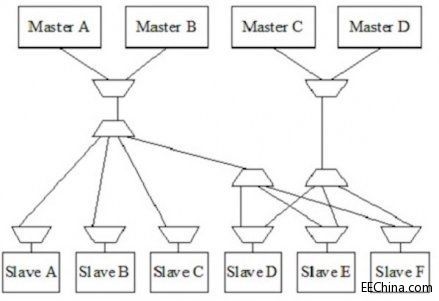

ЭМ2ЃКSoCЩшМЦжаЕФНЛВцОиеѓПЊЙиТпМЪгЭМЃЌеЙЪОСЫУПИіДгЦїМўЖЫИДгУЦїЕФЙиЯЕЁЃ ДгЮяРэЩЯПДЃЌНЛВцОиеѓПЊЙиЪЧгУУПИіДгЦїМўЖЫЕФИДгУЦї(mux)ЪЕЯжЕФЁЃУПИіИДгУЦївдЗжВМЪНжйВУЛњжЦгыжйВУЦїЯрёюКЯЁЃ

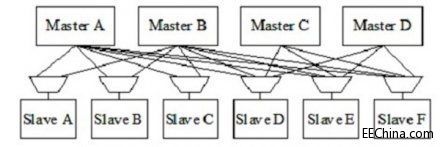

ЭМ3ЃК4ИіжїЦїМўЁЂ6ИіДгЦїМўЕФНЛВцОиеѓЪЕЯжБэУїЃЌдкSoCжмЮЇВЩгУЭъећЪ§ОнТЗОЖЕФГпДчТЗгЩЪЧВЛЧаЪЕМЪЕФЁЃ етжжЗНЗЈзюЖржЛФмРЉеЙЕНМИИіжїКЭДгЦїМўНгПкЁЃШЛЖјЃЌГ§СЫЬиЖЈЪ§СПЭтЃЌдкSoCжмЮЇТЗгЩЭъећЪ§ОнТЗОЖЕФГпДчЖдВМОжВМЯпРДЫЕвВБфЕУВЛЧаЪЕМЪЁЃ

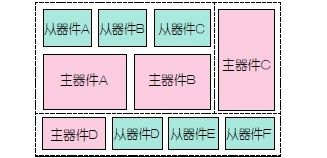

ЭМ4ЃКЫцзХЙІФмЧхЕЅЕФдіГЄКЭIPФЃПщЕФдіМгЃЌSoCЕзВуЙцЛЎБфЕУИќМгИДдгЁЃ ЖдгкОпгаКмЖрИіжї/ДгНгПкЕФИќМгИДдгЕФаОЦЌРДЫЕЃЌгаБивЊдкЖрИіЮяРэЧјгђЩшМЦЖРСЂЕФЛЅСЌЃЌОпЬхШЁОігкIPФкКЫЗжзщЕФВМОжЧщПіЁЃВЛЭЌЧјгђжЎМфЕФЧХНгЬсЙЉСЫжїЦїМўКЭДгЦїМўжЎМфБивЊЕФЛЅСЌЁЃ

ЭМ5ЃК4ИіжїЦїМўгы6ИіДгЦїМўЕФЛЅСЌЃЌгУСЫвЛИіЧХГадиТпМбгЪБПЊЯњЁЃ ЧХЛсЮЊЪ§ОнДІРэЕФдіМгбгЪБжмЦкЃЌвђЮЊЫќУЧГадиСЫТпМбгЪБВПЗжЁЃ НЛВцОиеѓЛЅСЌПЩвдНтОіВЂааЗУЮЪДјРДЕФЯЕЭГМмЙЙЮЪЬтЃЌЕЋдкгаДѓСПжїКЭДгIPФЃПщЕФЧщПіЯТЃЌгжЛсдьГЩаОЦЌжаЕФЮяРэЪЕЯжЮЪЬтЁЃ ФЃПщЛЏЩшМЦКЭNoC ЮЊСЫМѕаЁбгЪБЃЌЕижЗПЩвддкжїНгПкВрНтТыЃЌВЂзЊЛЛЮЊМђЕЅЕФТЗгЩIDКХЁЃЦЌЩЯЕФжйВУЦї-ИДгУЦїКЭТЗгЩЦї-НтИДгУЦїЭјТчПЩвдЪЙгУМђЕЅЕФТЗгЩIDЃЌВЂЭЈЙ§СДТЗаОЦЌжмЮЇЕФМђЕЅЮБПЊЙиИДгУЦїРЉеЙТЗгЩЗжВМЁЃетбљзіЛЙФмЪЕЯжИќКУЕФЛЅСЌТпМВМОжЁЃЖдгкаОЦЌжадНРДдНЖрЕФзпЯпРДЫЕЃЌВМОждНРДдНживЊЃЌвђЮЊЫќЛсЪЙТЗгЩИќМгШнвзЁЃ NoCЛЅСЌПЩвдЭЌЪБНтОіетСНИіЮЪЬтЃЌвђДЫдкЪжЛњгІгУДІРэЦїЁЂЪ§зжЕчЪгКЭЛњЖЅКаПижЦЦїЕШЯШНјЩшМЦжаЕУЕНСЫЙуЗКЪЙгУЁЃ

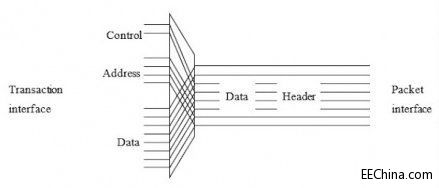

ЭМ6ЃКРћгУвЛИіNoCЪЕЯжЕФ4ИіжїЦїМўгы6ИіДгЦїМўЕФЛЅСЌЁЃ ЩшМЦЪІвЛжББЛвЊЧѓдкSoCжаМЏГЩИќЖрЕФЙІФмЃЌвђДЫЖдЛЅСЌММЪѕЕФашЧѓгыШеОудіЁЃЮЊСЫИњЩЯаЮЪЦЃЌЖдвдЯТЙІФмЕФашЧѓЗЧГЃЦШЧаЃК ЁёЕНВЛЭЌЪТЮёДІРэавщЕФНгПк ЁёПЊЙи(НтИДгУ-ТЗгЩЦїКЭжйВУЦї-ИДгУЦї) ЁёQoS(гХЯШМЖ) ЁёЛКГхЦї ЁёЪ§ОнТЗОЖДЎааЛЏ ЁёЭГМЦадЬНВт ЁёЕїЪдИњзй ЁёЗР Л№ ЧН ЁёМФДцЦїЦЌ(ЙмЯпНсЙЙ) ЁёЪБжггђНЛВц ЁёЕчбЙгђ ЁёЕчдДгђ етЖдЛЅСЌЩшМЦЬсГіСЫаТЕФЬєеНЁЃЩшМЦЪІЯЃЭћIPПЩвджиИДЪЙгУВЂЧвПЩвджиИДХфжУЁЃЖјдкНЛВцОиеѓТпМжажЇГжВЛЖЯдіМгЕФЙІФмвЊЧѓНЋЛсЬсИпИДдгадЃЌМѕТ§ЙиМќТЗОЖЫйЖШЁЃСэЭтЃЌаэЖрзпЯпМДЪЙдкЩйСПЪ§ОнВйзїЪБвВЛсБЛДЅЗЂЃЌвђДЫЯћКФСЫгыжЎВЛГЩБШР§ЕФЙІКФЁЃШЛЖјЃЌПЩИДгУЕФФЃПщЛЏЛЅСЌЩшМЦдкМђБуадЁЂЫйЖШЁЂУцЛ§КЭЙІаЇЗНУцгаКмДѓЕФгХЪЦЃЌПЩПЫЗўДЋЭГзмЯпКЭНЛВцОиеѓММЪѕЕФИДдгадЁЃ ЪТЮёЁЂДЋЪфКЭЮяРэВу NoCММЪѕВЩгУСЫвЛжжШ§ВуавщЃЌЦфжаЪТЮёВузїЮЊзюИпВуЁЃИУММЪѕЪЙгУAMBAЁЂPIFЁЂOCPЛђЦфЫќЙЄвЕБъзМавщжДааЫљвЊЧѓЕФЖСаДВйзїЃЌЭЌЪБвВЪЧЖдгкЭЈЙ§ЛЅСЌСЌНгЕФIPФЃПщЕФЩшМЦЪІРДЫЕЃЌвВЪЧПЩМћЕФНгПкЁЃ NoCжаЕФДЋЪфВуавщгЩЭјТчНгПкЕЅдЊ(NIU)НјааЙмРэЁЃЫќЮЊУПИіЪТЮёДДНЈвЛИіЛђЖрИіЪ§ОнАќЁЃЫљгаЪ§ОнАќЖМвЛИіАќЭЗЁЃЖСЪ§ОнАќКЭаДЪ§ОнАќЖМдкАќЭЗКѓАќКЌЪ§ОндиКЩЁЃАќЭЗНЋЕижЗЁЂЪТЮёВЮЪ§КЭБпДјаХКХзїЮЊгђНјааНтТыЁЃNIUПижЦЯджјЕФЪТЮёКЭДјБъЧЉЕФађСаЁЃАќЭЗИёЪНЪЧзюаЁЕФЃЌВЂеыЖдУПИіNoCзїСЫВЛЭЌГЬЖШЕФгХЛЏЁЃАќЭЗдкЛЅСЌФкЕФУПИіЮБПЊЙиДІНЋРДздЗЂЦ№епЕФЧыЧѓТЗгЩЕНФПБъЃЌВЂНЋРДздФПБъЕФЯьгІТЗгЩЕНЗЂЦ№епЁЃЧыЧѓКЭЯьгІТЗОЖЪЧЖРСЂЕФЃЌвђДЫПЩвдЯћГ§ТпМКЭМмЙЙЗНУцЕФвРРЕадЃЌДгЖјБмУтЫРЫјЁЃ

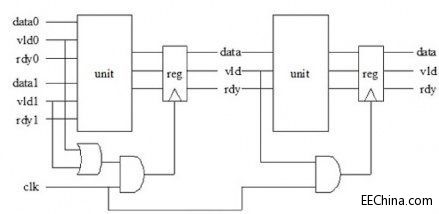

ЭМ7ЃКНЋЕижЗ/ПижЦаХКХгыЪТЮёНгПкКЭАќДЋЪфНгПкМфЕФЪ§ОнИДгУЦ№РДПЩвдМђЛЏЛЅСЌЩшМЦЁЃ ФЃПщЛЏЩшМЦжЇГжЪЙгУЗЧГЃМђЕЅЕФавщдкЮяРэВуЩЯДЋЪфДЋЫЭАќЁЃетжжавщгЩвдЯТаХКХзщГЩЃК ЁёData [N ЮЛ] (гЩЗЂЫЭепЧ§ЖЏ) ЁёValid [1 ЮЛ] (гЩЗЂЫЭепЧ§ЖЏ) Ёё Ready [1 ЮЛ] (гЩНгЪеепЧ§ЖЏ) ЁАValidЁБКЭЁАReadyЁБЪЕЯжСїГЬПижЦЃЌжЇГжКѓбЙЪНЗДРЁЁЃетжжМђЕЅЕФЮеЪжавщДцдкгкNoCЕФЫљгаЕЅдЊжЎМфЁЃМђЕЅНгПкБъзМЛЏКѓдЪаэЫљгаЕЅдЊПЩНЛЛЛЕиСЌНгдквЛЦ№ЃЌОЭЯёЖљЭЏЕФЛ§ФОвЛбљЁЃ ЪБжгЪїбЁЭЈ РћгУжкЫљжмжЊЕФаОЦЌЩшМЦЗНЗЈЃЌПЩвддкВЛвЊЧѓДЅЗЂЕФжмЦкФкбЁЭЈУПИіДЅЗЂЦїЖЫЕФЪБжгЁЃетжжЗНЗЈЪЪгУгкВЩгУЫљгаЛЅСЌММЪѕЕФДЅЗЂЦїЃЌВЛЙ§ВЛФмНтОіЪБжгЪїЙІКФЮЪЬтЁЃ ЪБжгЪїЪЧИіЕЅвЛаХКХЃЌвђДЫБШЪ§ОнТЗОЖвЊеЕУЖрЁЃШЛЖјЃЌЮЊСЫЕНДяЫљгаЮяРэЩЯЗжВМЕФДЅЗЂЦїЃЌЪБжгЪїБШУПИіЪ§ОнТЗОЖЮЛгаЖрЕУЖрЕФЛљБОЬиеїЁЃИљОнЖЈвхЃЌЪБжгдкУПИіЪБжгжмЦкФкЛсДЅЗЂСНДЮЃЌвђДЫЪБжгЪїЕФЙІКФвЛАувЊЯджјДѓгкЪ§ОнТЗОЖЁЃ дкНЛВцОиеѓжаЃЌУПИіЪБжгЭјТчМДЪЙдкЪ§ОнВЛСїЖЏЪБвВЛсДЅЗЂЁЃЫфШЛРэТлЩЯдкНЛВцОиеѓжаЕФШЮКЮЕиЗНЖМУЛгаЪ§ОнДЋЫЭЪБШдФмдкжмЦкжаЪЕЯжЕНЫљгаНЛВцОиеѓТпМЕФЪБжгбЁЭЈЃЌЕЋгааЉВЛЧаЪЕМЪЁЃЫќвЊЧѓЖдЖрИідЖЖЫаХКХНјааДѓЕФЪБжгбЁЭЈИДгУЃЌвдВњЩњМЄЛюаХКХВЂЛиЫЭжСЖрИідЖЖЫДЅЗЂЦїЁЃ вђДЫЃЌгУзщКЯТпМЕФзюМђФЃПщДюНЈЛЅСЌПЩвдЪЕЯжЕЅдЊМЖЪБжгбЁЭЈЙІФмЃЌВЂЧвЦфПХСЃдЖБШЕЅЦЌНЛВцОиеѓжаЕФОЋЯИЕУЖрЁЃ

ЭМ8ЃКЭЈЙ§ФЃПщЛЏЗНЗЈДюНЈЛЅСЌОЭПЩвдЪЙгУзщКЯТпМЕФЕЅдЊМЖЪБжгбЁЭЈЙІФмЁЃ жЛгадкгааЇЕФЮеЪжаХКХгааЇЪБЕЅдЊФкКЭЕЅдЊМфЕФМФДцЦїВХЛсДЅЗЂЃЌгУгкжИЪОЪ§ОнвЕЮёЕФДцдкЁЃбЁЭЈТпМЖдУПИіЕЅдЊРДЫЕЪЧОжВПЕФЃЌвђДЫТЗОЖИќЖЬЃЌВЂЧвзюДѓЯоЖШЕиМѕЩйСЫВњЩњМЄЛюаХКХЫљашЕФИДгУЕчТЗЁЃЪБжгбЁЭЈЪЧЗжВМЪНЕФЃЌФЃПщЛЏЛЅСЌЕФУПИіФЃПщдкПеЯаЪБжгжмЦкЪБЙиБеЃЌЖјВЛЙмЯЕЭГгрЯТВПЗжЕФзДЬЌЁЃетбљПЩвдЪЕЯжНгНќРэЯыЕФзюаЁПЊЙиЙІКФЁЃ ФЃПщЛЏЕФЦфЫќКУДІ Г§СЫЪБжгбЁЭЈЭтЃЌЦфЫќКУДІАќРЈИФНјСЫЛьКЯЪНуажЕЕчбЙ(Vt)злКЯЕФЪЙгУЁЂМѕЩйСЫТЉЕчЙІКФЁЂИФЩЦСЫТпММђвзадЃЌВЂЪЕЯжСЫОжВПЛЏЁЃ дкаЁФЃПщжЎМфЕФШЮКЮЕиЗНВхШыЙмЯпНсЙЙвдТњзузюаЁбгЪБЪБађвЊЧѓЬсИпСЫзлКЯЙЄОпЪеСВЪБађЕФФмСІЁЃгЩгкгаИќДѓЕФгрСПЃЌзлКЯгааЇМѕЩйСЫДгФЌШЯИпVtЕЅдЊЕНИќПьЕФЕЭVtЕЅдЊЕФТЗОЖЪ§СПЁЃетбљЃЌФЃПщЛЏЩшМЦЕЅдЊжЎМфЕФЙмЯпНсЙЙОЭФмМѕЩйТЉЕчЙІКФЁЃСэЭтЃЌИќШнвзЕФЪБађЪеСВвВФмИФЩЦEDAЙЄОпЕФЪЙгУЃЌгажњгкЪЕЯжзюаЁУцЛ§ЗНУцЕФзюгХЛЏ(ИќаЁЕФТуЦЌУцЛ§ПЩМѕЩйТЉЕчЙІКФ)ЁЃ 64ЮЛAXIЪТЮёНгПкавщвЊЧѓжСЩй272ЬѕзпЯпЁЃЖдгкФЃПщЛЏЗНЗЈРДЫЕЃЌвЛИі64ЮЛЪ§ОнАќНгПквЊЧѓ148ЬѕЯп(УПИіЧыЧѓЯьгІЭјТчжага64ЮЛЪ§Он+8зжНкМЄЛю+ready+valid=74)ЁЃвђДЫЃЌНЋЪТЮёДђАќВЂдкЗЂЦ№епКЭФПБъДЋЪфЪБПЩвдНЋаОЦЌЕзВуЙцЛЎФкЕФзпЯпЪ§СПМѕЩй1.8БЖ(272/148=1.8)ЁЃ вђЮЊетжжЗНЗЈеыЖдЕЅдЊжЎМфЕФНгПкЪЙгУЕФЪЧМђЕЅЮяРэВуавщЃЌЫљвдКмШнвзИФБфАќЪ§ОнЕФДЎааЛЏДІРэЁЃШЋВПвЊЧѓОЭЪЧМђЕЅЕФИДгУЦїКЭМФДцЦїЃЌвдБуМѕаЁЪ§ОнТЗОЖПэЖШЁЃ ИФБфЪ§ОнТЗОЖЕФДЎааЛЏДІРэЗНЪНЃЌЪЙжЎВЛГЌЙ§ТњзуаОЦЌВЛЭЌВПЗжЕФДјПэвЊЧѓЫљашЕФПэЖШЃЌПЩвдМѕЩйаОЦЌЫљгаВПЗжЕФЛЅСЌТпМУцЛ§ЃЌЖјЧветаЉаОЦЌЖМвЊЧѓаЁгкзюДѓДјПэЁЃвЛАуРДЫЕЃЌДѓЖрЪ§аОЦЌжаЕФОјДѓВПЗжЖЅВуЛЅСЌВЛвЊЧѓзюДѓДјПэЁЃ ОжВПЛЏ НЋНгПкжЎМфЕФИДгУЦїЕШЕЅдЊЪЕЯжОжВПЛЏДІРэКѓЃЌЕЅдЊжЎМфЕФзпЯпЦНОљГЄЖШНЋБфЖЬЁЃетвтЮЖзХзпЯпЕчШнЪЙЕУЕчСїЕФЯћКФБфЕУИќаЁЁЃетбљЛЙФмМђЛЏКѓЖЫАцЭМЙЄвеЃЌвђЮЊЫќФмМѕЩйдЖОрРыЗХжУЕФТпМжЎМфЖдСЌНгЕФвРРЕадЁЃ ЛњЖЅКа(STB)SoCЩЯЕФНсЙћ жЇГж1080p120жЁЕФжаЖЫЛњЖЅКаSoCОЭЪЙгУСЫФЃПщЛЏNoCЛЅСЌЃЌЫќеЙЪОСЫФЃПщЛЏЗНЗЈЕФгХЪЦЁЃетжжФЃаЭЪЙгУСЫ11ИіжїЦїМўКЭ6ИіДгNIUЕФЛЅСЌЃЌЯћКФЕФТпМУцЛ§ЪЧ183kИіУХЁЃ ЮвУЧЗжЮіСЫШ§жжЪБжгбЁЭЈЪНПЊЙиЛюЖЏГЁОАЁЃЪзЯШЪЧзюВюЕФЪгЦЕДІРэГЁОАЃЌЦфжаБЛЩшЮЊ120HzЯдЪОЪфГіЕФЪгЦЕНтТыЦїКЭCPUЪЧЯЕЭГЕФжївЊИКдиЃЌЫќУЧЯћКФСЫМИКѕЫљгаПЩгУЕФDDRФкДцДјПэЁЃ ЕкЖўжжГЁОАдђГЪЯжСЫЦеЭЈАИР§ЪгЦЕНтТыЦїЕФИДдгадЁЃЕкШ§жжГЁОАУЛгаЪгЦЕНтТыЃЌжЛЪЧгУЭјТчфЏРРЗНЪНЃЌПЩЪЕЯжУПУы30жЁЕФжаЕШЯдЪОЫЂаТТЪЁЃ

НЛВцОиеѓдкDDRЛюЖЏЦкМфЕФУПИіжмЦкЖМБиаывЊМЄЛюЃЌвђДЫдкЕквЛжжЧщПіЯТФЃПщЛЏЩшМЦЭЈЙ§ДЅЗЂDDRЛюЖЏПЩвдНЕЕЭ2.3БЖЕФЙІКФЃЌЕкЖўжжЧщПіЪЧ2.5БЖЃЌЕкШ§жжЧщПіЪЧ3.4БЖЁЃ дкД§ЛњГЁОАЃЌФЃПщЛЏNoCЛЅСЌеЙЪОСЫБШНЛВцОиеѓИќЧПЕФДЅЗЂНкЪЁаЇЙћЁЃСэЭтЃЌИќДѓЕФаОЦЌгаИќЖрЕФжїNIUТпМвЊЗУЮЪЭЌбљЪмЯоЕФЙВЯэзЪдДЁЃетаЉаОЦЌашвЊгУИќДѓБШР§ЕФЪБМфбЁЭЈИќЖрЪ§СПЕФДЅЗЂЦїЁЃвђДЫЖдФЃПщЛЏNoCЩшМЦРДЫЕДЅЗЂНкЪЁаЇЙћЫцзХаОЦЌГпДчЕФдіМгЖјдіЧПЁЃ МѕЩйЪБжгЪїЙІКФ ФЃПщЛЏNoCПЩвдМЋДѓЕиНЕЕЭИпМЏГЩЖШаОЦЌжаЖЅВуЛЅСЌНсЙЙЕФЙІКФЁЃЭЈЙ§ОжВПЛЏЪБжгбЁЭЈЙІФмЃЌЪБжгЪїжЛдкЪ§ОнДЋЫЭЕФТЗЯпЩЯВЂЧвжЛдкДЋЫЭжмЦкФкгаЙІКФЁЃетбљПЩвдЯджјНЕЕЭЪБжгЪїЕФЙІКФЁЃСэЭтЃЌОжВПЕФДЎааЛЏДІРэДгзюДѓГЬЖШЕиМѕЩйСЫжЇГжУПЬѕСДТЗЕФДјПэвЊЧѓЫљашЕФЪ§ОнТЗОЖТпМЁЃетгжНјвЛВНМѕаЁСЫТЉЕчУцЛ§ЁЃСэЭтЃЌФЃПщЛЏжЇГжИќМгОЋЯИЕФЙмЯпПХСЃЃЌПЩвдИќКУЕиЪеСВЪБађЧвВЛРЫЗбгрСПЁЃетгжНјвЛВНдЪаэзлКЯЙЄОпЪЙгУИќаЁЁЂИќМгИпаЇЕФУХЁЃ |

ЭјгбЦРТл