FPGAКөХҪСЭБ·ВЯјӯЖӘ47ЈәПыіэЧйәПВЯјӯөДГ«ҙМ

·ўІјКұјдЈә2015-7-8 10:10

·ўІјХЯЈәrousong1989

|

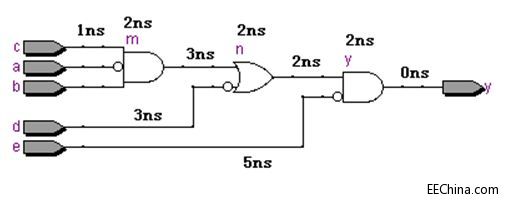

ПыіэЧйәПВЯјӯөДГ«ҙМ ұҫОДҪЪСЎЧФМШИЁН¬С§өДНјКйЎ¶FPGAЙијЖКөХҪСЭБ·ЈЁВЯјӯЖӘЈ©Ў· ЕдМЧАэіМПВФШБҙҪУЈәhttp://pan.baidu.com/s/1pJ5bCtt ФЪХВҪЪ3.2өДЧоәуІҝ·Ц¶ФУЪЧйәПВЯјӯәНКұРтВЯјӯөД»щұҫёЕДоЧцБЛҪППкПёөДҪйЙЬЈ¬ІўЗТБРҫЩБЛТ»ёцКөАэЛөГчКұРтВЯјӯФЪҙу¶аКэЙијЖЦРёьУЙУЪЧйәПВЯјӯЎЈЧйәПВЯјӯФЪКөјКУҰУГЦРЈ¬өДИ·ҙжФЪәЬ¶аИГЙијЖХЯН·МЫөДТю»јЈ¬АэИзХвАпТӘЛөөДГ«ҙМЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© ИОәОРЕәЕФЪFPGAЖчјюДЪІҝНЁ№эБ¬ПЯәНВЯјӯөҘФӘКұЈ¬¶јУРТ»¶ЁөДСУКұЈ¬ХэКЗОТГЗНЁіЈЛщЛөөДЧЯПЯСУКұәНГЕСУКұЎЈСУКұөДҙуРЎУлБ¬ПЯөДіӨ¶МәНВЯјӯөҘФӘөДКэДҝУР№ШЈ¬Н¬Кұ»№КЬЖчјюұҫЙнөДЦЖФм№ӨТХЎў№ӨЧчөзС№ЎўОВ¶ИөИМхјюөДУ°ПмЎЈРЕәЕөДёЯөНөзЖҪЧӘ»»ТІРиТӘТ»¶ЁөДЙПЙэ»тПВҪөКұјдЎЈУЙУЪҙжФЪХвР©ТтЛШөДУ°ПмЈ¬¶аёцРЕәЕөДөзЖҪЦө·ўЙъұд»ҜКұЈ¬ФЪРЕәЕұд»ҜөДЛІјдЈ¬ЧйәПВЯјӯөДКдіцІў·ЗН¬КұЈ¬¶шКЗУРПИУРәуЈ¬ТтҙЛНщНщ»біцПЦТ»Р©І»ХэИ·өДРЕәЕЈ¬АэИзТ»Р©әЬРЎөДВціејв·еРЕәЕЈ¬ОТГЗіЖЦ®ОӘЎ°Г«ҙМЎұЎЈИз№ыТ»ёцЧйәПВЯјӯөзВ·ЦРУРГ«ҙМіцПЦЈ¬ҫНЛөГчёГөзВ·ҙжФЪЎ°Г°ПХЎұЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© ПВГжОТГЗҝЙТФБРҫЩТ»ёцјтөҘАэЧУАҙҝҙҝҙГ«ҙМПЦПуКЗИзәОІъЙъәНПыіэөДЎЈИзНј5.14ЛщКҫЈ¬ХвАпФЪНј5.10ЛщКҫКөАэөД»щҙЎЙП¶ФХвёцЧйәПВЯјӯөДёчМхЧЯПЯСУКұәНВЯјӯГЕСУКұЧцБЛұкјЗЎЈГҝёцГЕСУКұөДКұјдКЗ2nsЈ¬¶шІ»Н¬өДЧЯПЯСУКұВФУРІ»Н¬ЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ©

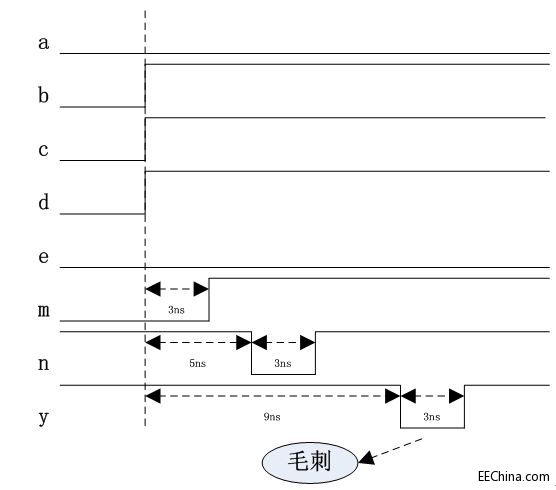

Нј5.14 ЧйәПВЯјӯВ·ҫ¶өДСУКұұкјЗ ФЪХвёцКөАэДЈРНЦРЈ¬ОТГЗІ»ДСјЖЛгіцКдИлРЕәЕaЎўbЎўcЎўdЎўeҙУКдИлөҪКдіцРЕәЕyЛщҫӯ№эөДСУКұЎЈНЁ№эјЖЛгЈ¬ҝЙТФөГөҪaЎўbЎўcРЕәЕөҪҙпКдіцyөДСУКұКЗ12nsЈ¬dөҪҙпКдіцyөДСУКұКЗ9nsЈ¬¶шeөҪҙпКдіцyөДСУКұКЗ7nsЎЈҙУХвР©ҙ«КдСУКұЦРЈ¬ОТГЗҝЙТФНЖ¶ПіцЈ¬ФЪөЪТ»ёцКдИлРЕәЕөҪҙпКдіц¶ЛyЦ®З°Ј¬КдіцyҪ«ұЈіЦФӯАҙөДҪб№ыЈ»¶шФЪЧоәуТ»ёцКдИлРЕәЕөҪҙпКдіц¶ЛЦ®әуЈ¬КдіцyҪ«»сөГОТГЗЖЪНыөДРВөДҪб№ыЎЈҙУұҫКөАэАҙҝҙЈ¬7nsЦ®З°КдіцyұЈіЦФӯҪб№ыЈ¬12nsЦ®әуКдіцy»сөГРВөДҪб№ыЎЈДЗГҙХвАпҫНҙжФЪТ»ёцОКМвЈ¬ФЪ7nsәН12nsЦ®јдөДХв5nsКұјдДЪЈ¬КдИлyҪ«»бКЗКІГҙЧҙМ¬ДШЈҝ ИзНј5.15ЛщКҫЈ¬ХвАпБРҫЩТ»ЦЦіцПЦГ«ҙМөДЗйҝцЎЈјЩЙиФЪ0nsТФЗ°Ј¬КдИлРЕәЕaЎўbЎўcЎўdЎўeИЎЦөҫщОӘ0Ј¬ҙЛКұКдіцy=1Ј»ФЪ0nsКұЈ¬bЎўcЎўdУЙ0ұд»ҜОӘ1Ј¬Кдіцy=1ЎЈФЪАнПлЗйҝцПВЈ¬КдіцyУҰёГТ»ЦұұЈіЦ1І»ұдЎЈө«ҙУОТГЗөДСУКұДЈРНАҙҝҙЈ¬КөјКЙПФЪ9nsөҪ12nsЖЪјдЈ¬КдіцyУР¶МФЭөДөНВціеіцПЦЈ¬ХвІ»КЗөзВ·УҰёГөДЧҙМ¬Ј¬ЛьТІҫНКЗХвёцЧйәПВЯјӯөДГ«ҙМЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ©

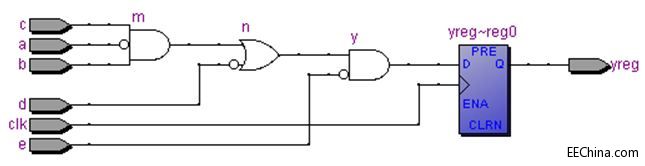

Нј5.15 ВЯјӯСУКұІЁРО јИИ»ОТГЗөД¶аёцКдИлРЕәЕөДұд»ҜЗ°әуИЎЦө¶јұЈіЦёЯөзЖҪЈ¬ДЗГҙХвёцөНВціеөДГ«ҙМЖдКөІ»КЗОТГЗПЈНыҝҙөҪөДЈ¬ТІәЬҝЙДЬФЪәуРшөзВ·ЦРХвёцГ«ҙМөјЦВәуРшөДІЙјҜіцПЦҙнОуЈ¬ЙхЦБК№өГТ»Р©№ҰДЬұ»ОуҙҘ·ўЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© әГБЛЈ¬СФ№йХэҙ«Ј¬ТӘПыіэХвёцГ«ҙМЈ¬НЁіЈУРБҪёц°м·ЁЈ¬Т»ёц°м·ЁКЗУІ°м·ЁЈ¬Из№ыФЪyРЕәЕЙПІўБӘТ»ёцөзИЭЈ¬ұгҝЙЗбЛЙөДҪ«ХвАаВціеҝн¶ИәЬРЎөДёЙИЕВЛіэЎЈө«КЗЈ¬ОТГЗПЦФЪКЗФЪFPGAЖчјюДЪІҝЈ¬»№ХжГ»УРХвСщөДМхјюәНҝЙДЬРФХвГҙҙҰАнЈ¬ДЗГҙЦ»ДЬ·ЕЖъХвЦЦ·Ҫ°ёЎЈБнТ»ЦЦ°м·ЁЖдКөТІҫНКЗТэИлКұРтВЯјӯЈ¬УГјДҙжЖч¶аКдіцРЕәЕҙтТ»ЕДЈ¬ХвЖдКөТІКЗКұРтВЯјӯГчПФУЕУЪЧйәПВЯјӯөДМШРФЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© ИзНј5.16ЛщКҫЈ¬ФЪФӯУРЧйәПВЯјӯөД»щҙЎЙПЈ¬ОТГЗМнјУБЛТ»ёцјДҙжЖчУГУЪЛшҙжЧоЦХөДКдіцРЕәЕyЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ©

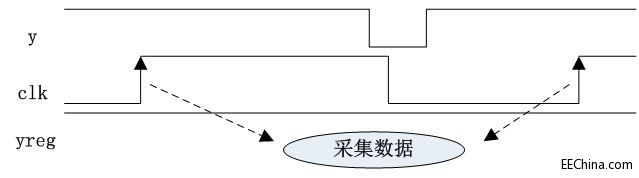

Нј5.16 јДҙжЖчЛшҙжЧйәПВЯјӯКдіц ИзНј5.17ЛщКҫЈ¬ФЪТэИлБЛјДҙжЖчәуЈ¬РВөДЧоЦХөДКдіцyregІ»ФЩЛжТвөДёДұдЈ¬¶шКЗФЪГҝёцКұЦУclkөДЙПЙэСШЛшҙжөұЗ°өДКдіцЦөЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ©

Нј5.17 јДҙжЖчЛшҙжІЁРО ТэИлКұРтВЯјӯәуЈ¬ІўІ»КЗЛөНкИ«ҫНІ»»бІъЙъҙнОуөДКэҫЭІЙјҜ»тЛшҙжЎЈФЪКұРтВЯјӯЦРЈ¬ОТГЗЦ»ТӘЧсСӯТ»¶ЁөД№жФтҫНҝЙТФұЬГвәЬ¶аОКМвЈ¬ИзұЈЦӨКұЦУclkУРР§СШЗ°әуөДКэҫЭҪЁБўКұјдәНұЈіЦКұјдДЪҙэІЙјҜөДКэҫЭКЗОИ¶ЁөДЎЈЈЁМШИЁН¬С§Ј¬°жИЁЛщУРЈ© |

НшУСЖАВЫ