FPGA实战演练逻辑篇30:FT232之UART电路设计

发布时间:2015-5-29 10:17

发布者:rousong1989

|

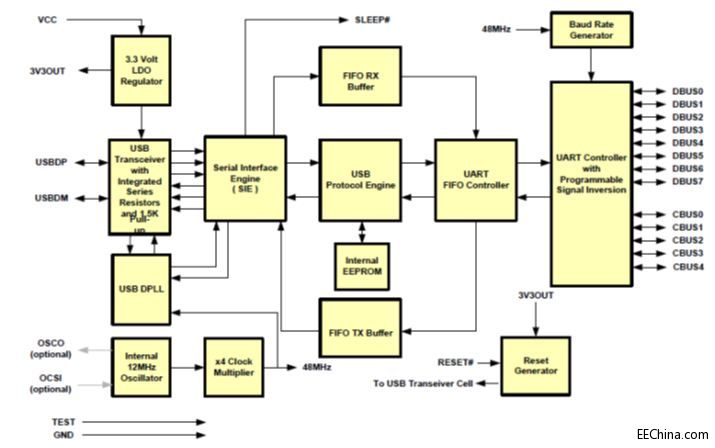

FT232之UART电路设计 本文节选自特权同学的图书《FPGA设计实战演练(逻辑篇)》 配套例程下载链接:http://pan.baidu.com/s/1pJ5bCtt FT232芯片内部功能框图如图6.68所示。它通过USB的D+/D-与PC进行通信,芯片内部能够根据USB协议对数据进行处理,最终通过FIFO将这些数据转换为UART协议和我们的FPGA进行通信。(特权同学,版权所有)

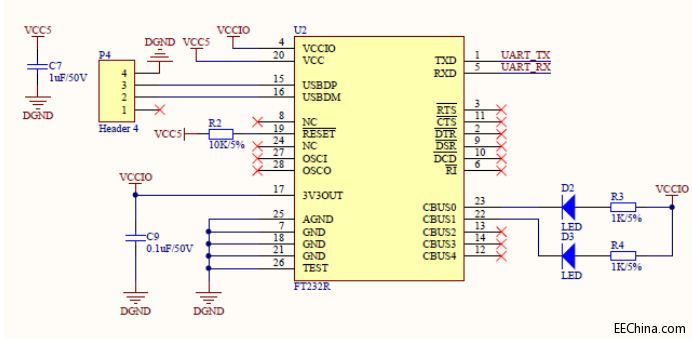

图6.68 FT232芯片内部功能框图 FT232R的接口电路如图6.69所示。P4为USB port,用于连接PC,UART_TX和UART_RX分别为FT232R芯片的UART发送和UART接收信号,对应的,UART_TX就是FPGA的UART接收,而UART_RX就是FPGA的UART发送信号。D2和D3连接着U2-23/22,在UART_RX和UART_TX收发的时候它们会闪烁以指示工作状态。(特权同学,版权所有)

图6.69 FT232接口电路 FT232R的引脚定义如表3.8所示。(特权同学,版权所有) 表3.8 FT232引脚定义

|

网友评论