MACsec IP核大幅提升数据中心安全性

发布时间:2015-4-13 16:35

发布者:eechina

|

作者:Paul Dillien,High Tech Marketing公司顾问(paul@high-tech-marketing.co.uk);Tom Kean博士,Algotronix公司总经理(tom@algotronix.com) 数据中心设备设计人员将结合采用基于FPGA的内核来提供安全的高性能以太网链路。 云存储和IT服务外包对IT经理而言极富吸引力,因为这不仅能降低成本,而且还可减轻支持工作。然而有一个大的顾虑就是,这样做会使敏感数据流出公司防火墙外,造成安全隐患。这种顾虑是完全可以理解的,因为信息对于许多公司而言是最宝贵的资产,无论是会计、客户还是制造相关的数据。 而现在,设备制造商能够通过使用赛灵思基于FPGA的解决方案来提高性能和安全水平。满足以太网新标准MACsec要求的Algotronix综合安全子系统采用基于赛灵思FPGA的高性能、低时延、高能效IP核。 基于FPGA的解决方案比基于软件的解决方案速度要快得多。此外,专用硬件可接管系统处理器,使其处理其它任务,如深度数据包检查等。或者,设计人员也可采用成本更低的处理器。 加密和认证 保护信息的一个显著策略就是当数据在网络中传输和在数据中心周围移动时对其进行加密。一旦数据被非授权方渗透网络链路而拦截,数据加密能够确保其无法被读取。原则上,数据还应经过认证,从而确保其完整性。消息认证旨在检测原始加密数据是否已被篡改,包括因传输错误而造成变更,抑或是被攻击者为从中牟利而恶意破坏。 目前以太网传输已成为主流通信方式,这是一种既高效又具有可扩展性的高速传输方法。随着以太网标准的普及,以太网传输成本不断降低,这一优势使其更加引人注目,进而确保以太网继续成为首选的L2技术。不过,就在几年以前,以太网标准还没有任何加密规范要求,只能采用运行在通信协议栈上层的IPsec等技术来完成加密工作。 现在,根据IEEE 802.1AE标准,最新以太网标准扩展版本新增了大量安全措施。该技术在几年前正式确定,其采用集成式安全系统来加密并认证消息,同时检测并应对一系列网络攻击。该标准被称为“媒体接入控制安全(Media Access Control Security)”标准,常常简称为“MACsec”。Algotronix从几年前就开始努力推出能够根据多种不同数据速率要求提供硬件加速加密功能的IP核。 (Algotronix还可提供面向IPsec的IP核,该产品与MACsec产品的接口类似,对需要支持双重标准的系统而言是不错的选择。) 简要介绍MACsec系统,帮助了解规范的全面性,同时深入说明实现该规范的复杂程度。 信任实体 MACsec指的是由网络上的节点组成的一系列信任实体。每个节点都能接收加密消息和明文消息,而系统策略则用于明确如何处理每条消息。内核包括明文消息的旁通选项,无需认证或验证。与IPsec等作为端到端技术运行在L3/L4的协议不同,只要数据包进入或离开以太网LAN,MACsec就能对每个数据包进行解密和验证。 MACsec适用于星型或总线型LAN等以太网拓扑结构,也可支持点对点系统。 MACsec标准采用安全实体(SecY)方法,也就是每个节点或实体都具备与其以太网源地址相链接的唯一密钥。为支持多个虚拟SecY,我们设计出了该IP核的1G版本。因此,单个以太网MAC能针对多用户LAN等应用配备多个与之关联的MACsec SecY。MACsec通常与IEEE 801.1X-2010或互联网密钥交换(IKE)配合使用,可实现网络周围的安全密钥分配。 数据中心之所以会选择L2连接功能在数据中心内移动数据包,是为了提高速度,并最大程度地降低时延和减少数据包中的开销数据。相比之下,如果用诸如IPsec等安全的L3技术进行通信,消息必须传到协议上层进行处理,而这会增加时延。 此外,L2解决方案也能避免创建L3安全策略这一复杂工作。 数据中心能够采用MACsec提供防火墙后台的保护,或将其用在数据中心之间的直接链路上。系统管理员可授权设备以安全方式进行通信。设备能够检测错误或误用情况,如拒绝服务攻击(DOS)。 符合可编程要求 市场因需求不同,日趋细分化。可定制FPGA解决方案理想适合于MACsec。起初,MACsec的设计是作为一项技术应用于城域网,而现在在数据中心中也找到了其用武之地,这就提高了对基于FPGA的解决方案的整体需求。 Algotronix开发MACsec内核是一个自然演进,因为我们已经打造了一系列称为“AES-GCM”的加密引擎。这些内核的运行速率分别为1G、10G和40G。我们通过流水线、提高时钟速率并从赛灵思Artix器件逐步发展到Kintex器件乃至Virtex FPGA,来实现上述速率的。我们将利用这些技术来推动Virtex UltraScale™器件上的吞吐量,使其达到100G。 我们使用FPGA中的IP核能够实现多种不同性能,可支持从1GbE到10 GbE的不同速率(即,内核在最坏情况下的实际吞吐量)。此外我们还计划推出40G和100G的版本。这比基于软件的系统要快得多。内核通常直连接到硬件MAC(如图1所示),因为FPGA芯片上的嵌入式存储器的软件会尽可能足够快地传输数据,以满足其吞吐量要求。如果在硬件上实现安全功能,同时从未向软件提供未加密密钥,那么系统就不那么容易受到特洛伊木马(Trojan horse)和病毒等常见软件攻击。

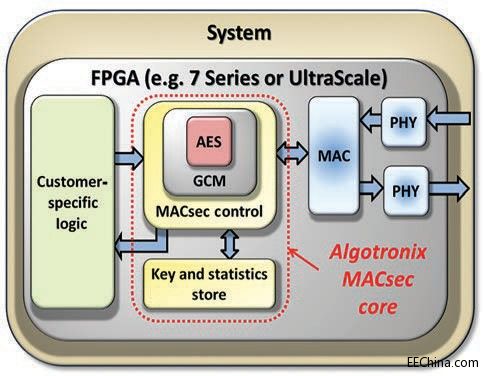

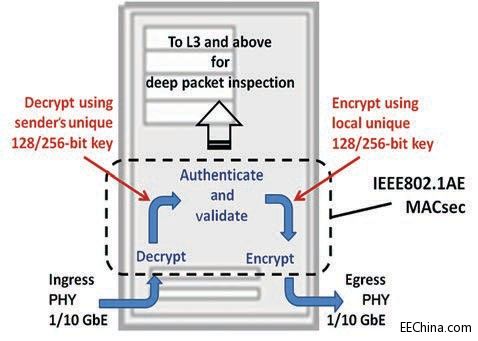

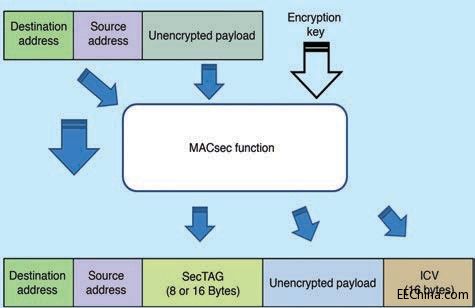

图1 – 整个MACsec IP核位于FPGA内,可实现最大安全性。 这样就算IT专业人士必须考虑系统的整个软件层面的情况时,也能更方便地分析系统漏洞。 另一个重要考虑事项就是FPGA进行算法加速的系统要大幅降低功耗。加速的算法包括加密函数等,免得再用软件去实现加速。FPGA比软件解决方案的能效明显要高得多。 所有Algotronix加密内核都内置了一项重要属性,那就是能够在Block RAM或FPGA架构的查找表(LUT)中实现称为“S-Boxes”的关键模块。有了该属性,客户可通过综合平衡两种资源类型便能利用现有资源实现设计。比方说,如果MACsec内核外的设计未占用大量的BRAM,那么就可用Block RAM来实现S-Boxes,否则就用LUT来实现。 MACSEC细节 MACsec系统的设计理念是:每个数据源使用不同的加密密钥。接收到消息后,接收器会在片上CAM的列表中进行查找,明确用以解密数据包的正确密钥。每个数据包都有编号,确保能检测并拒绝接收重复或重新发送的数据包,这种方法可防范“中间人”攻击。 MACsec还会收集有关被拒收的数据包数量的统计数据以及拒绝的原因。提供统计数据以支持攻击检测是超出基本加密隐私、认证和防止重发功能之外的更高一层的安全性,能让系统管理器主动应对正在进行的攻击。 我们采取的方法是对业经验证的AES-GCM内核周围的MACsec逻辑进行“打包”。就此而言,设计高效快速的加密内核只是设计挑战的一部分。MACsec标准涉及面广,包括许多变量。 举例来说,该标准最初只指定128位的加密密钥。采用128位密钥,数据进行10次转换(被称为“轮”)后在内核中完成加密过程。该标准经修订后可提供256位加密密钥,整个数字加密过程历经14轮。这是通过添加流水线级数并提高密钥存储所需的内存带宽才实现的。 MACsec与以太网流量类型无关,也对更高层协议透明。推出这些内核后,就能方便地将MACsec添加到系统中,从而进一步提高网络防护。配备MACsec的站点仍能与未采用MACsec额外安全保障机制的其它站点进行通信。 从媒体接入控制器(MAC)将以太网数据包提供给MACsec内核。您可结合使用1G MACsec内核、片上收发器和三模以太网MAC(TEMAC)构建高效的小型解决方案。每个数据包都包含发起传输的源码的目的地和地址。该标准保存在MACsec系统中,但一个重要的因素是,在多次反射传输中,“源码”将是传递数据包的最终设备的地址。因此,与可被视为端到端方案的IPsec不同,MACsec是以逐跳方式工作的。对于每次跳跃,MACsec都要求输入端的所有加密数据进行解密,然后使用分配给传输设备的唯一密钥再重新加密。解密的明文可在每一级提供数据包检查功能,如图2所示,也能供流量管理器用以管理数据流。 在MACsec标准中,图3给出的报头包含附加字段“MAC安全标签(SecTAG)”,其可定义EtherType,并标明数据包是否加密。数据附加在ICV字段的消息末尾,则表示已经认证。

图2 – 消息在入端口被解密,并在出端口被加密。

图3 – MACsec帧结构包括MAC安全标签(SecTAG)字段,其可定义EtherType,并标明数据包是否加密。 ICV协同加密密钥,可认证包括报头和MACsec标签的帧,进而确保帧的源地址和目的地地址都不会被篡改。我们在FPGA架构中实现该逻辑,确保其能够具备快速的可预测的时序,从而最大程度地降低时延。 MACsec内核包括连接到每个源地址的查找表。该表包含的密钥必须能够用来成功解密消息,我们精心设计该功能,使其能够高效实现在LUT和器件的Block RAM中。我们充分利用FPGA解决方案的灵活性,采用实现方案选项(如可采用128位或256位密钥,也可修改内核支持的虚拟SecY数量)来设计内核。 新标准的另一个重要特性就是,MACsec可收集数据包级的统计数据。系统管理员能够了解有关信息(如多少数据包因为延迟而被拒收,或者因为无效解密密钥或使用错误密钥而未通过完整性检查),并将这些统计数据与正确传输的数据包数量进行比较。 MACsec标准可面向点对点应用提供精简选项。这样就无需采用CAM从数据包中的显式安全通道标识符和单点到多点操作的选择方案中确定密钥。我们的内核还可支持关联于单个以太网的多个虚拟SecY,这样,不同的密钥就能用来加密从MAC传输到不同目的地的数据。MACsec标准将这种配置定义为多用户局域网,因为这就像这些目的地位于不同以太网LAN上一样。该特性使得系统能够通过使用不同密钥加密输出来对接收设备进行分区。 数据中心可能会采用多个SecY来创建虚拟分区,这样客户A的数据就可通过唯一的加密密钥与客户B的数据划分开。 数据中心内部通信可根据需要进行组织来分隔选定的机架,进而提供虚拟隔离区。这种功能可保护数据完整性,并应对数据中心和云应用中的隔离问题。无论是意外错误连接还是恶意行为(见图4),MACsec系统都能检测到未经认证的数据包,系统管理员可通过设置策略将其隔离或删除。

图4 – MACsec将拒绝通过错误连接抵达的数据包,无论是因为意外情况造成还是恶意行为导致。 所有数据加密和解密都在端口级进行。除了附加的MACsec报头和较少的额外时延,打开端口级加密不会增加开支,也不会对性能造成其它影响。 通过采用符合IEEE 802.1AE要求的加密Ethernet Lecel 2方案,设备厂商现在能用这些内核推动其系统特色化。基于云的用户可能与其他用户相互之间不信任,但他们现在能够从MACsec提供的数据机密大获裨益,并且数据源认证功能可进一步保护他们的数据。设备制造商则能选择可用的IP核来满足1Gb和10 Gb以太网吞吐量的需求。 这种架构设计能通过Kintex或Virtex FPGA器件轻松实现10Gbps的速度。在最坏情况下,该设计只需更改每个数据包的密钥便可支持巨型帧和最小型数据包。内核符合全面规范要求,每个MACsec内核都能支持各种常用的FPGA产品系列。 配套提供源码 Algotronix采取了不同寻常的措施,即为所有许可的内核提供HDL源码。这样做的主要动机是支持客户检查,以便确保代码不含病毒或特洛伊木马代码,而且不会强制进入非授权状态或操作。有了源码,就能降低客户安全审核的成本和复杂性。此外,源码可加速设计进程,因为工程师能够方便地尝试使用诸如加密、解密或加密/解密等不同配置参数和密钥长度,并了解其各自仿真内核中的信号状态。 您可对内核进行配置,通过实现较宽的数据路径来提高吞吐量,或通过选择较窄的数据宽度来最大程度地减小FPGA封装尺寸。拥有源码还有其它更多优势,包括更便于了解内核工作情况;也让文档记录和归档变得更快捷方便。 此外,还配套提供了广泛的验证测试平台,可帮助客户在ModelSim等工具中确认操作是否正确。测试平台包括MACsec的行为模型和MACsec IP核的自检版本,能针对行为模型检查可综合硬件的输出。这种自检设计可在用户仿真中实现实例化,便于测试实际用户设计环境下的内核表现,并在错误驱动的情况下提供有用的诊断信息。 内核可提供许多选项,因此精确的资源数量将取决于您如何选择参数,如数据速率、密钥长度和所选SecY数量以及其它。然而,赛灵思网站IP部分列出的10G MACsec内核采用6,638个slice、20,916个LUT和53个BRAM块。如需获取许可证选项,敬请联系Algotronix。 赛灵思低功耗 FPGA与Algotronix MACsec内核的完美结合为设备制造商实现产品差异化提供了高性能、低时延的解决方案。安全特性使得数据中心能够确保其客户机密,同时还可帮助安全管理员检测并打击恶意行为。 |

网友评论