使用VVCCS且基于比较器的缓冲器

发布时间:2015-1-29 10:54

发布者:designapp

|

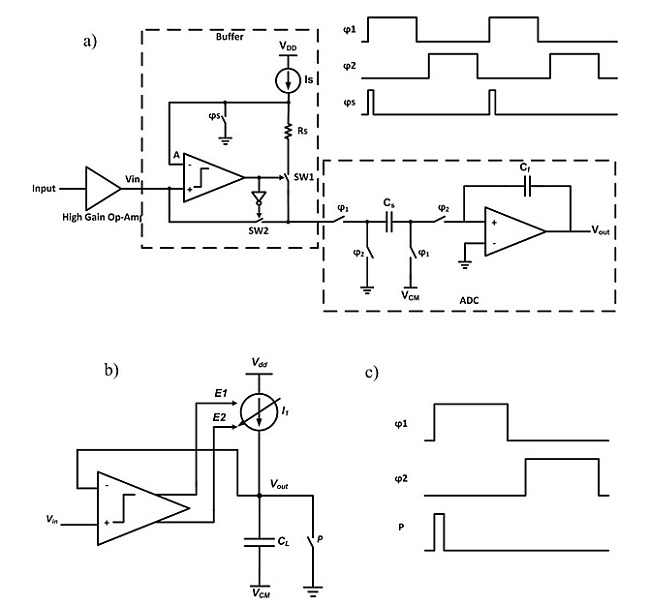

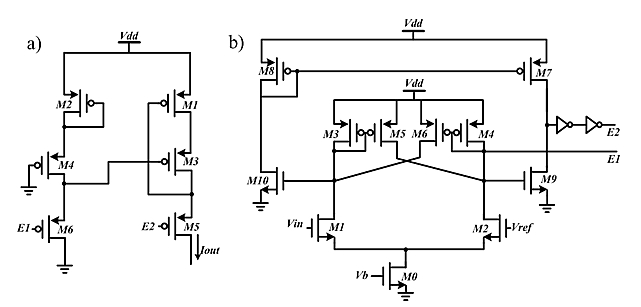

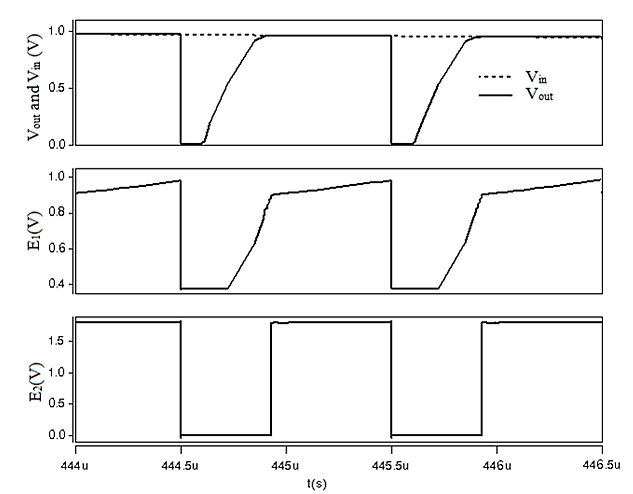

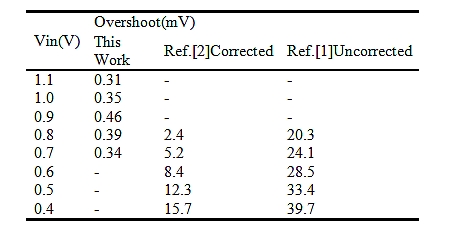

编辑注:博士研究生Seyyed Hossein Pishgar给我看了这篇论文,我相信论文中提出了一些独特且有创造性的电路和架构。我过去见过基于比较器的缓冲器,外部带有阻性纠错电路,它能增强高增益放大器的驱动能力,可以驱动像ADC前端电路中使用的开关电容负载。这种纠错机制使用了一个电阻,该电阻与充电路径和纠错电路串联在一起,可减少放大器输出端的过冲。 在以下论文中,Pishgar和来自伊朗沙希德贝赫什提大学微电子实验室和电子/计算机工程系的同事展示了一种基于比较器的缓冲器电路。该电路使用可变电压控制的电流源来抑制放大器的过冲倾向。这是创建这种放大器以驱动开关电容负载的一种创新方法。好消息是,基于比较器的缓冲器通常是一种功耗比运放低的解决方案。坏消息是,基于比较器的缓冲器容易产生过冲。这些学生们在论文中提出一种利用可变电压控制的电流源(VVCCS)解决这种过冲问题的方法。 下面是这篇完整的论文内容。 原文作者:Seyyed Hossein Pishgar1、Alihossein Sepahvand1、Omid Hashemipour2,伊朗德黑兰沙希德贝赫什提大学微电子实验室(1),伊朗德黑兰沙希德贝赫什提大学电子与计算机工程系(2)。 使用可变电压控制的电流源实现基于比较器的高精度缓冲器 概述:本文介绍了一种使用可变电压控制的电流源(VVCCS)实现的基于比较器的新型缓冲器。可跟踪电流源的应用提供了高精度的性能,不仅能减少输出节点的过冲误差,还能减少过冲误差相对输出电压的变化。同时利用0.18μm CMOS技术的仿真对这种方法进行了验证,推荐电路的总功耗估计为616μW。 引言 现在,减少电池消耗已经成为电路设计师的优先任务之一。最近出现了一种基于新型比较器的开关电容电路[1]。它可以替代运算放大器,而后者与比较器、开关、电流源和逻辑控制门一起占据了总功耗的最大部分。虽然基于运放的电路能够迫使输入节点形成虚拟地,但基于比较器的电路可以实现虚地条件。虽然如此,但这些基于比较器的电路存在过冲误差问题。这种过冲误差主要来源于比较器有限延时、电流源响应时间和逻辑控制固有延时。为了克服这个缺点,可以使用精细电流源来减少过冲误差。在文献[2]的缓冲器电路中应用了基于比较器的开关电容,它推荐了一种不同的方法来减小过冲误差。为了补偿精细电流源的损耗,使用了开关和纠错电阻(图1(a))。不过这种缓冲器仍然存在明显的过冲误差以及过冲误差相对输出电压的变化。 本文提出了可以在基于比较器的缓冲器设计中应用的新方法,它既能减少过冲误差,也能减少过冲误差相对输出的非线性。 基于比较器的推荐缓冲器电路 推荐缓冲器的构建模块和时钟时序图分别如图1.1(b)和(c)所示。双路输出比较器用于控制可变电压控制的电流源。在预置阶段,输出电压保持在电路的最低电压。虽然输出小于输入,但比较器的输出将打开电流源。负载电容被充电,Vout电压上升。在?1阶段开始时,E1和E2为0,此时电路中流动的是电流源最大值。随着Vout的上升,E1成正比增加。接着VVCCS电流值逐渐减小,输出斜率随之减小。 E2可低可高。当Vout越过输入电压值时,E2被置为高,负载电容不再被充电。电路固有延时效应通过VVCCS减小了,因此在输出电压中产生的过冲误差值可以忽略不计。过冲误差可以用高分辨率比较器进一步减小,但会增加功耗。  图1:a)带电阻纠错电路的基于比较器的缓冲器[2]。b)基于比较器的推荐缓冲器电路框图。c)时钟时序图。 可变电压控制的电流源 在推荐电路中使用的定制的可变电压控制电流源[3]如图2(a)所示。当E1和E2处于最低点时,输出电流的最大值将流过输出端。当E1增加时,M2和M4的电流以及Iout将减小。最终当E2被置高时,M5被关断。 定制的比较器 基于比较器的推荐缓冲器中使用的电压比较器如图2(b)所示[4]。为了提高比较器的增益,后置放大器电路与文献[4]有所不同,后者使用NMOS输入放大器。另外,在这个比较器中,信号E1由M2的漏极驱动,这个漏极清楚地再现了信号Vin的变化,而信号E2只有两个状态。在这个比较器中有三个主要模块:由M1和M2组成的前置放大器级,包含M3-M6的判决电路级,以及由剩余电路组成的后置放大器级。第一级电路只是一个基本的差分n沟道放大器,连接着来自第二级的有源负载。第二级电路中的判决过程如下:首先考虑Vin低于Vref的情况。此时M4导通,M3关断。因此所有偏置电流通过M4和M6。在这种情况下,E1和E2处于它们的最低点。随着Vin增加并接近Vref,M4和M6中的电流开始减小,因此E1从地电平开始逐步按比例增加到Vin,而E2仍然是0。当Vin超过Vref电平时,偏置电流将流过M3和M5。现在E2使用判决电路的再生属性快速上升到高电平状态。最后,利用后置放大器级电路增强比较器的分辨率。  图2:a)可变电压控制的电流源,b)推荐架构中的定制比较器。 仿真结果 为了验证基于比较器的推荐缓冲器精度,在HSPICE环境下用0.18μm标准CMOS工艺和1.8V电源电压对电路进行了仿真。假定共模电压、正弦输入信号的幅度和频率分别是0.9V、0.2V和10KHz。电路工作时钟为1MHz,负载为1pf电容。图3显示了推荐电路的输入、输出、E1和E2波形。从图中可以看出,当Vout远小于Vin时,Vout电压以高斜率上升。当Vout接近于Vin电压值时,输出斜率会减小。E1信号应跟踪比较器输出信号的逐步增加。另外,当Vout超过Vin电压值时,E2信号状态被触发。  图3:信号E1、E2和Vout。 将各种输入电压值应用于推荐电路,结果见表1。在信号E2变高过程中对这些结果进行了测试。  表1:过冲误差与输入电压值的关系,并与基于以前比较器的缓冲器结果进行了比较。 本文小结 本文介绍了基于比较器的典型缓冲器的新模型。为了最大限度地减小过冲误差,应用了一个可变电压控制的电流源,并使用了具有两个输出端的定制比较器。通过与以前先进设计的比较向我们展示了推荐电路的更好性能。仿真是在采用0.18μm标准CMOS工艺的HSPICE环境中进行的。推荐缓冲器的功耗估计为616μW。 参考文献 [1] Fiorenza J. K., Sepke T., Holloway P., Sodini C.G., Lee H.S., Comparator-based switched-capacitor circuits for scaled CMOS technologies, IEEE J. Solid-ST. Circ., 41 (2006), No. 12, 2658–2668. [2] Chae J., Temes G.C., Comparator-based buffer with resistive error correction, Electron. Lett., 46(2010), No. 17,1188–1190. [3] Razavi B., Design of analog CMOS integrated circuits, McGraw-Hill Companies, Incorporated, Boston, 2000. [4] Gregorian R., Introduction to CMOS OP-AMPs and comparators, John Wiley and Sons Incorporated, NewYork, 1999. |

网友评论