零基础学FPGA(二)关于触发器

发布时间:2015-1-14 13:37

发布者:wp1981

|

作者:小墨同学 哎呀!好久没有管理博客了,虽然才一篇文章...呵呵。刚过完年,首先祝大家新年快乐!马年大吉!各种马上有!小弟在这给各位大神拜年了! 从放假到年三十吧,大约有20天左右,一直在忙比赛,就是之前博客里提到的比赛,毕昇杯。我和小伙伴们忙了20多天,终于忙出了点结果,搞得我26号才回家,差点被我妈骂死...骂归骂,我们还是有点成果的。队长方面实现了用手机对系统的控制,队友方面把触摸屏搞好了,我是第一次做PCB板,在学校用机器做的,一口气做了6块,光这一块就废了好大劲,对于我这种新手来说...除了PCB板,我负责上的上位机也有很大进展,为了达到创新的目的,我把上位机做成了一个虚拟ipad,可以实现一些小功能,有划屏、计算器、播放器、相册、计算器、小游戏之类的功能,使我们的上位机不仅可以实现对下位机的操控,更重要的是实现了人性化的界面,使人们用起来舒服。总体来说项目完成了85%了,过年回去完成剩下的就好了,也希望团队可以取得好成绩。这几天过年老玩了,整天到处乱跑,好在年也拜的差不多了,该静下心来看看书了。有几个同学已经回学校了,我回来这么晚,也不想惹老妈生气了,打算晚点回去,今天刚开始看书,就看了看触发器这部分,随便写写,当做笔记好了,也希望各位大神给小弟纠纠错,第一次学数电,还蛮好玩~ 太书面化的话我就不说了啊,有些东西就像书上写的,真的看着看着就想睡觉了,还是大白话直白哈。 1、关于触发器的分类 触发器呢大体可以按这几个部分分类:1、按晶体管性质分,可以分为BJT集成电路触发器和MOS型集成电路触发器。2、按工作方式分,可分为异步工作方式和同步工作方式,异步工作方式也就是不受时钟控制,像基本RS触发器,同步方式就是受时钟控制,称为时钟触发器。3、按结构方式分,可分为维持阻塞触发器,延边触发器,主从触发器等。4、按逻辑功能分,可分为RS触发器,JK触发器,D触发器,T触发器,T'触发器等。 2、关于触发器的逻辑功能 触发器总体来说有四种功能:分别是置“0”、置“1”、保持、翻转。前两个不说了,就是高低电平,保持就是维持原状态不变,翻转就是从原状态变为他的反状态。 3、基本RS触发器

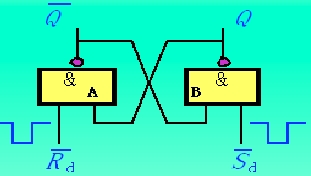

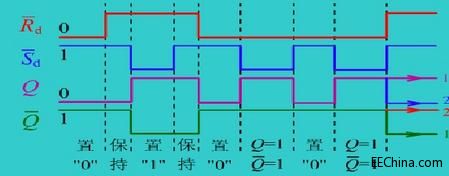

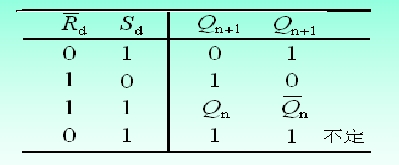

这是基本RS触发器原理图,具体工作原理就不写了吧,个人觉得比较好理解,就说几个我刚开始看的时候有些看不懂的地方吧。 1、关于负脉冲和低电平 所谓负脉冲呢,就是一个信号从高电平置为低电平,然后延迟一段时间后再置为高电平的过程,就像上图所示的脉冲。而低电平就没有返回高电平的过程。 2、关于Q端 我们知道不管是置“1”端还是置“0”端,操作的都是Q端,间接操作Q非端,刚开始我就错误的以为Sd非端控制相应上面的端口,其实不是,Rd非端和Sd非端都是控制Q端,即Sd非端一个负脉冲,Q端置“1”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。Rd非端一个负脉冲,Q端置“0”,Q端如果原状态就是“1”,则加一个负脉冲后原状态不改变。 3、两个端口都加负脉冲的情况下 按理说两个端口是不允许同时加负脉冲的,因为一旦两端同时加负脉冲,则两个输出端就都为“1”,这样与我们认为的两个输出端的值互为反变量的原则就相违背了,但是在画时序图的时候,可以将两个输出端同画为高电平。重点是,当两个输入端都为低电平的时候,再把它们扳回高电平时,这时候输出端就会有两种结果,具体是哪种结果,这要取决于两个门电路的运转速度问题了。下面是时序图

下面是基本RS触发器的真值表

4、同步RS触发器

同步RS触发器是在基本RS触发器的基础上加了两个与非门,CP是时钟。 当CP为“0”时,下面两个门电路相当于被封死,这时第一级门电路的输出端就都为"1",即保持状态。当CP为“1”时,门电路被打开,第一级门电路的输出端分别为Rd非和Sd非,这就和刚才的基本RS触发器一样了。 5、JK触发器 JK触发器的内部原理比较复杂,对于初学者来说,我觉得直接记住他的功能就可以了,这样不至于越学越迷糊,当然有条件的朋友也可以自己去弄明白其中的原理

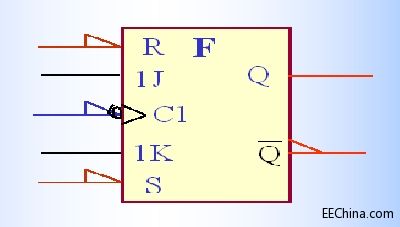

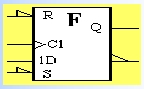

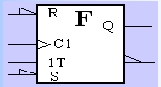

这是JK触发器的逻辑符号,其中C1代表时钟,左边那个箭头代表负脉冲有效,也就是说只有在时钟负脉冲来临的时候Q端才会发生变化(同步工作的情况,异步除外),R,S端为强制置“0”、“1”端,这两个端口不受时钟控制,可以强迫置位,R端负脉冲置“0”,S端负脉冲置“1”,J、K端为信号端。

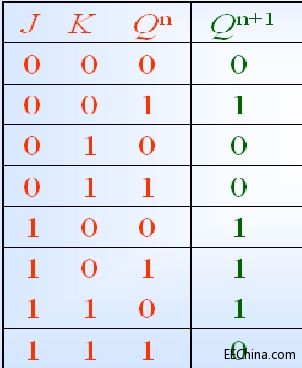

这张是JK触发器真值表,可以看出当R、S端都为“1”的情况下,信号端的J、K才会发挥作用,从上到下依次是“保持”、置“0”、置“1”、翻转。

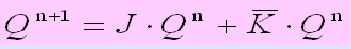

这样就可以得到JK触发器的特性表,有了这个表,我们就可以写出他的特性方程

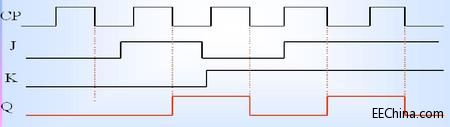

这是时序图,注意Q端只在时钟下降沿出变化 6、D触发器

这是D触发器的逻辑符号,注意时钟是高电平有效,R、S端是强迫置位端,D为信号端 D触发器比较简单,真值表见下图

7、T触发器

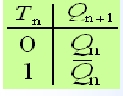

真值表

8、T‘触发器

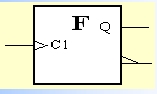

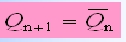

T’触发器的重要应用,可以用作分频 9、最后展示一下我之前的作品,呵呵..

谢谢大家支持,也希望各位大神给予纠错,纯手打... |

网友评论