“ΒΫγΉν–Γ≥Ώ¥γΒΡ PCI Express ±÷” ICΘ§Ω…ΫΪΙΠΚΡΫΒΒΆ60%

ΖΔ≤Φ ±ΦδΘΚ2015-1-12 13:28

ΖΔ≤Φ’ΏΘΚeechina

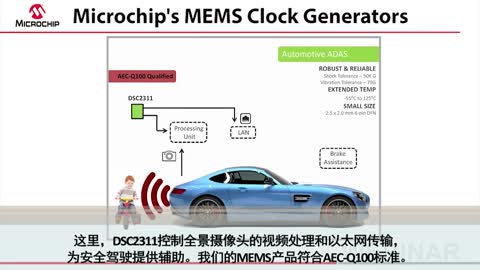

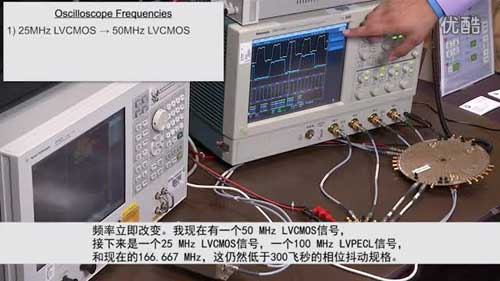

ΗΏ–‘ΡήΡΘΡβ”κΜλΚœ–≈Κ≈ICΝλΒΦ≥ß…ΧSilicon Labs(–ΨΩΤ Β―ι “”–œόΙΪΥΨ)Ϋϋ»’–ϊ≤Φ’κΕ‘œϊΖ―ΒγΉ”ΚΆ«Ε»κ Ϋ”Π”ΟΆΤ≥ω“ΒΫγΉν–Γ≥Ώ¥γΒΡΖϊΚœ PCI Express (PCIe) ±ξΉΦΒΡ ±÷”ΖΔ…ζΤς–ΨΤ§Θ§‘Ύ’β–©”Π”Ο÷–Ω…ΩΩ–‘ΓΔΑεΟφΜΐΓΔΤςΦΰ ΐΝΩΚΆΙΠΚΡΆ®≥Θ «ΤδΙΊΦϋ…ηΦΤ“ΣΥΊΓΘ…ηΦΤ÷Φ‘Ύ¬ζΉψPCIeGen1/2/3 ±ξΉΦΒΡ―œΗώΙφΖΕΘ§–¬–ΆΒΡ Si50122 ±÷”ΤΨΫη Silicon Labs ΒΆΙΠΚΡ PCIe ΚΆCMEMS ΦΦ θΈΣΗςάύ”Π”ΟΧαΙ©ΝΥΫΎΡήΓΔΟβΤ§ΆβΨßΧεΒΡ ±÷”ΫβΨωΖΫΑΗΘ§’β–©”Π”ΟΑϋά® ΐΉ÷¬ΦœώΜζΚΆΨ≤Χ§’’œύΜζΓΔIPΜζΕΞΚ–ΓΔΗΏ«ε ”ΤΒΝς≤ΞΖ≈ΜζΓΔΗΏ«εΈζΕ» ΐΉ÷Βγ ”ΓΔΦ“ΆΞ”ιά÷ΚΆ“τΤΒœΒΆ≥ΓΔΕύΙΠΡή¥ρ”ΓΜζΓΔœϊΖ―άύΚΆ–Γ–Ά…Χ“Β¥φ¥Δ…η±ΗΓΔΦ“ΆΞΆχΙΊΚΆΈόœΏΫ”»κ…η±ΗΒ»ΓΘ Si50122 «ΒΎ“ΜΗωΦ·≥…Silicon Labs CMEMSΉ®άϊΦΦ θΒΡ ±÷”ΖΔ…ζΤς–ΨΤ§ΓΘΤ§ΡΎΒΡCMEMS–≥’ώΤςΈΣ–ΨΤ§ΡΎΒΡCMOS ±÷”Βγ¬ΖΧαΙ©ΝΥ“ΜΗωΈ»Ε®ΒΡΤΒ¬ ≤ΈΩΦΘ§ Γ»ΞΝΥΆ®≥ΘΥυ–ηΒΡ¥σΧεΜΐΓΔΖ÷ΝΔΒΡ ·”ΔΨßΧεΓΘΆ®Ιΐάϊ”Ο CMEMS ΦΦ θΘ§Si50122PCIe ±÷”ΧαΙ©ΝΥΦΪΦ―ΒΡΩΙ≥εΜςΚΆΩΙ’ώΕ·–‘Θ§Φ¥ Ι‘ΎΕώΝ”ΒΡΧθΦΰœ¬(άΐ»γΦΪΕΥΈ¬Ε»±δΜ·)“≤ΡήΙΜ»Ζ±ΘΗΏΩ…ΩΩ–‘≤Δ±Θ÷Λ–‘ΡήΓΘ ÷≥÷œϊΖ―ΒγΉ”≤ζΤΖ»ί“Ή‘β”ω≈ωΉ≤ΜρΒχ¬δΒΡ«ιΩωΘ§ Ι”ΟΈ»ΙΧΒΡ CMEMSPCIe ±÷”ΖΔ…ζΤςΕχ≤Μ «Μυ”ΎΨßΧεΒΡΫβΨωΖΫΑΗΘ§ΡήΙΜœϊ≥ΐ”…”Ύ ·”Δ–≥’ώΤςΥπΜΒΕχΒΦ÷¬œΒΆ≥Ι ’œΒΡΖγœ’ΓΘ ΓΓΓΓ÷ß≥÷ΦΪ–ΓΒΡ2mmx2.5mm 10“ΐΫ≈ TDFN ΖβΉΑΘ§Si50122 «“ΒΡΎœ÷”–ΒΡΉν–Γ≥Ώ¥γΒΡ PCIe ±÷”ΖΔ…ζΤςΘ§“≤ «“ΒΡΎΉνΒΆΙΠΚΡΒΡΟβΤ§ΆβΨßΧεΒΡPCIe ±÷”ΫβΨωΖΫΑΗΓΘΫαΚœΝΥ“ΒΡΎΝλœ»ΒΡ–Γ≥Ώ¥γΚΆ≥§ΒΆΙΠΚΡΘ§Si50122≥…ΈΣ≤…”Ο PCI eΜΞΝΣ±ξΉΦΒΡΩ’Φδ ήœόΒΡ ÷≥÷ΚΆΒγ≥ΊΙ©Βγ–ΆœϊΖ―ΒγΉ”ΚΆ«Ε»κ Ϋ”Π”ΟΒΡΉνΦ―ΫβΨωΖΫΑΗΓΘ ΓΓΓΓΈΣΝΥΫΒΒΆœΒΆ≥≥…±ΨΓΔΙΠΚΡΚΆΤςΦΰ ΐΝΩ≤ΔΦρΜ·Βγ¬ΖΑε…ηΦΤΘ§Si50122PCIe ±÷”ΖΔ…ζΤς≤…”ΟΝΥΒΆΙΠΚΡΒΡΓΑΆΤΆλ(Push-pull)Γ± Ϋ HCSL δ≥ωΜΚ≥εΤςΘ§ Γ»ΞΝΥHCSL δ≥ωΆ®≥ΘΥυ–ηΒΡΥυ”–Άβ≤Ω÷’ΕΥΒγΉηΓΘΕχΨΚ’υΕ‘ ÷–ΨΤ§Ά®≥Θ Ι”Ο¥ΪΆ≥ΒΡ δ≥ωΜΚ≥εΤςΦήΙΙΘ§Τδ–η“Σ1ΗωΒγ‘¥ΒγΉηΤς“‘ΦΑΟΩΗω δ≥ωΕΥΩΎ…œΕύ¥ο4Ηω÷’ΕΥΒγΉηΤςΘ§’βΤ» Ι…ηΦΤ»Υ‘±‘Ύ Ι”Ο2¬Ζ δ≥ωΤςΦΰ ±“ΣΙήάμΕύ¥ο9ΗωΤ§ΆβΒγΉηΤςΓΘΆ®Ιΐ Γ»Ξ÷ΎΕύΒΡΤ§ΆβΤςΦΰΘ§ΆΤΆλΦΦ θ ΙΒΟ…ηΦΤ»Υ‘±ΡήΙΜ‘Ύ δ≥ω“ΐΫ≈ΚΆΫ” ’Τς÷°Φδ Ι”Ο÷±Ν§œΏΘ§¥”ΕχΜώΒΟΗϋΩ…ΩΩΒΡ–≈Κ≈Άξ’ϊ–‘ΓΘΤδΥϊ¥σΕύ ΐ PCIe ±÷”Ι©”Π…ΧΆ®≥Θ≤…”Ο¥ΪΆ≥ΒΡΚψΝς(constant-current)ΦΦ θΘ§œύΫœ÷°œ¬Θ§‘Ύ δ≥ωΜΚ≥εΤς÷–≤…”ΟΆΤΆλΦΦ θΙΠΚΡΩ…ΫΒΒΆ60%“‘…œΓΘ ΓΓΓΓSi50122 PCIe ±÷”–ΨΤ§ΧαΙ©2¬ΖΒΆΙΠΚΡ100MHz≤νΖ÷HCSL δ≥ωΚΆ1¬Ζ25MHzLVCMOS ±÷” δ≥ωΓΘ”…”ΎΥϋ «ΟβΤ§ΆβΨßΧεΒΡΫβΨωΖΫΑΗΘ§“ρ¥ΥΥϋ≤Μ–η“ΣΤ§Άβ25MHz≤ΈΩΦ ±÷”‘¥ΓΘ’ΐ»γSiliconLabs »Ϊ≤ΩΒΡPCIeΦΤ ±IC≤ζΤΖΉιΚœ“Μ―υΘ§Si50122–ΨΤ§Άξ»Ϊ≥§‘ΫΝΥPCIeGen1/2/3±ξΉΦ÷–Ε‘”ΎΕΕΕ·–‘ΡήΒΡ“Σ«σΘ§≤Δ«“÷ß≥÷Ω…―ΓΒΡά©ΤΒΒς÷ΤΙΠΡή“‘Ϋχ“Μ≤ΫΫΒΒΆΒγ¥≈Η…»≈(EMI)ΓΘ ΓΓΓΓSiliconLabs ΦΤ ±≤ζΤΖ”ΣœζΉήΦύ JamesWilson ±μ ΨΘ§ΓΑΥφΉ≈Β±ΫώΙΠΚΡΚΆΩ’Φδ ήœόΒΡœϊΖ―ΒγΉ”ΚΆ«Ε»κ Ϋ≤ζΤΖ≤ΜΕœ≤…”Ο PCIe ±ξΉΦΘ§ΩΣΖΔ»Υ‘±–η“Σ–¬“Μ¥ζ PCIe ±÷”ΫβΨωΖΫΑΗ“‘Ήν–ΓΜ·ΙΠΚΡΓΔBOM ΐΝΩΚΆΒγ¬ΖΑεΟφΜΐΓΘΈ“Ο«…ηΦΤ–¬–ΆΒΡΜυ”ΎCMEMSΒΡΟβΤ§ΆβΨßΧεSi50122PCIe ±÷”Θ§÷Φ‘ΎΈΣΩλΥΌά©’ΙΒΡPCIe –≥ΓΧαΙ©ΗΏΦ·≥…Ε»ΓΔΒΆΙΠΚΡΓΔΗΏΩ…ΩΩ–‘ΚΆ…ηΦΤΒΡΦρ“ΉΜ·Γ±ΓΘ |

Άχ”―Τά¬έ