基于PCI总线通用DSP信号处理系统的设计

发布时间:2010-6-30 16:37

发布者:我芯依旧

|

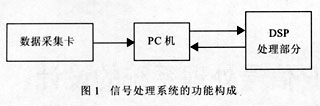

1 引言 1.1 DSP简介及基本特点 数字信号的处理离不开算法和实现手段。数字信号处理器(digital signal processor简称DSP)。是在模拟信号变换成数字信号以后进行高速实时处理的专用处理器,是实现实时数字信号处理的有力工具。DSP目前广泛应用于模式识别,数字通信,信号处理,工业控制等领域。TI公司的TMS320C54X系列DSP有着以下的特点:采用先进的修正增强型哈佛结构,片内共有8条总线(1条程序存储器总线,3条数据存储器总线和4条地址总线);高度并行和带有专用硬件逻辑的CPU设计;高度专业化的指令系统;模块化结构设计;能降低功耗和提高抗辐射能力的新的静电设计方法。因此它能高速实时以及灵活地应用于图像处理、语言处理、频谱分析、数字滤波、实时控制 等各个领域。TMS320VC5402是54X系列中应用比较广泛的一种芯片,它有着丰富的接口资源,是一种集数据处理和通信功能于一体的高速微处理器。其操作速率为40~100MIPS。 1.2 PCI局部总线的性能和特点 PCI总线是一种不依附于某个具体处理器的局部总线。从结构上看,PCI是在CPU和原来的系统总线之间插入的一级总线,具体由一个桥接电路实现对这一层的管理,并实现上下之间的接口以协调数据的传送。管理器提供了信号缓冲,使之能支持10种外设,并能在高时钟频率下保持高性能。PCI总线也支持总线主控技术,允许智能设备在需要时取得总线控制权以加速数据传送。 2信号处理系统的功能构成 通用信号处理系统一般分为数据采集、数据处理和数据管理3个部分(图1)。采集部分可以采用通用的数据采集卡,数据管理部分则必须用 PC机才能完成。在信号处理系统中,最费时间,也即影响信号处理系统的实时性的瓶颈是数据的处理部分。数据的处理通常采用微机软件的方法, 但完全由PC机处理有个缺点,就是信号处理需要的运算主要是数字运算,因相对于通用CPU(GPP)来说,它是采用冯·诺依曼存储器结构,并不适用于数字信号的运算,不仅会造成处理速度慢,而且占用CPU时间过多,直接影响了PC机对数据的管理。因此,我们提出用另一种方法把信号处理部分从微机软件中分离出来,交给DSP处理,然后把DSP处理好的数据再传给PC机管理。该系统的功能构成如图1所示。这样不仅可以做到信号处理和数据管理并行进行,而且充分利用DSP对数字信号处理高速,并行的优势,提高了信号处理系统的实时性和稳定性。在对信号作连续的流水处理时,其性能优势更能得以体现,同时这也是一个廉价的产品,有着很高的性能价格比。

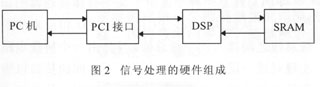

3 信号处理部分的硬件构成 信号处理部分接口电路的结构如图2所示。信号处理程序保存在主机中,在上电以后,自举加载到DSP中,并由固化在DSP的ROM中的 BOOTLOADER来完成。

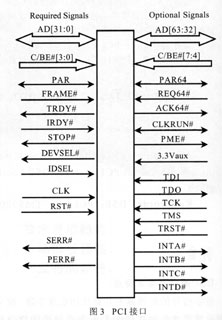

主要的处理流程是:信号采集卡把模拟的信息转化为数字的信息,进入PC机;由PC机通过PCI接口把数字的信息传输到DSP,保存在SRAM中; DSP从SRAM中读取数据,对信号进行处理;然后,把处理后的数据再从PCI接口传回PC机,交给数据管理部分处理。 3.1 PCI接口 为了管理数据和寻址、接口控制、仲裁以及系统运行,PCI接口对单个目标设备需要至少47个引脚,对主控设备最少需要49个引脚。图3给出了按功能组划分的引脚,左边的为必需引脚,右边的为可选引脚。图中的信号的方向是对主控设备/ 目标设备的组合而言。总引脚数120条(包含电源、地、保留引脚等)。PCI的总线宽度有32位和64位。在本系统中,设备是32位,没有作64位扩展。

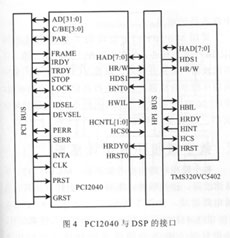

由于PCI总线时钟高达33MHz,信号线应按微波传输线对待,再加上接口逻辑本身的复杂性,设计难度很大。实现接口的办法:(1)用可编程逻辑器件EPLD或FPGA和用EPLD或FPGA实现。PCI接口的优点在于其灵活的可编程性。首先PCI接口可以依据插卡功能进行最优化,而不必实现所有的PCI功能,这样可以节约系统的逻辑资源;其次可以将PCI插卡上的其他用户逻辑与PCI接口逻辑集成在一个芯片上,实现紧凑的系统设计;再者当系统升级时,只需对可编程器件重新进行逻辑设计而无需更新PCB版图。(2)用专用PCI接口芯片实现。专用PCI接口芯片可以实现完整的PCI主控模块和目标模块接口功能,将复杂的PCI总线接口转换为相对简单的用户接口。厂商对PCI总线接口进行了严格的测试,用户只要设计转换后的总线接口即可。从某种意义上讲,PCI接口完成的是PCI总线和插卡上的从属处理器之间的消息传递。 由于以上原因,再考虑到系统开发的成本和周期,用专用接口芯片来实现PCI总线的接口较理想。接口芯片选用的是TI公司的PCI2040。PCI2040 是专门用来和54X或6X桥接的芯片,可以实现与TMS320VC5402的无缝接口 ;可以对端口进行访问读写。PCI2040提供了一个由PCI总线至插卡总线的直通通路(pass-thru)。PCI2040通过这些数据通路将复杂的PCI接口转换为相对简单的插卡总线接口。在本系统中,DSP中的资源映射到PC机的内存D9008000~D9008FFF和D9000000~ D9007FFF,中断请求为11。 PCI2040通过HPI接口与DSP通信,通信流程如下:PCI总线向PCI2040读写数据,PCI2040会根据这些命令在HPI口上发起相应的要求,这个通信过程可以通过编程首先初始化HPI控制寄存器HPIC以及主机地址寄存器HPIA,然后再从主机数据寄存器HPID中读/写数据来完成。具体的接口电路如图4所示:一块PCI2040最多可以挂接4片 DSP,以用于多DSP系统。

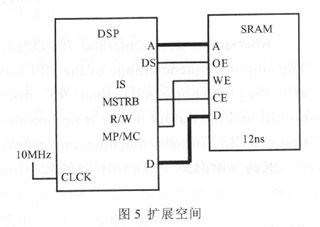

3.2 扩展空间 对信号处理系统来讲,DSP芯片所带的资源常常不能满足要求。这包括两个方面,一是程序空间,二是数据空间。对程序空间,可以选择不同的自举方式,充分利用PC机的资源。对数据空间有下面几种解决方法:(1)选择资源多的芯片,但这会引起成本的上升;(2)改进算法,边读取数据边处理;(3)用一个锁存器保存高位地址,自己扩展数据空间。这 里采用的方法是在用算法进行边读数据边处理的同时,用SRAM对数据空间进行了扩展。考虑到时序关系,以及TMS320VC5402只能与异步的存储器连接等因素。选用了TPS73HD318。它是 3.3V,1M×16大小的静态RAM,高低位字节可选,其读写速度达到12ns,能够与DSP的读写速度相匹配,无须另加接口时序。对于等待时间的产生,可以用软件的方法,对等待状态寄存器(SWWSR)进行设置。而产生的时延在调试时可以对DSP的时延寄存器进行设置, 以达到最大速度。硬件接口如图5所示。

4 DSP系统的自举 所谓自举(Bootload),就是在上电时从外部加载并执行用户的程序代码。加载的途径有:(1)从一个外部的EPROM或FLASH加载;(2)从主机通过HPI总线、并行I/O口、任何一个串行口、用户定义的地址热自举等方式加载。因为信号处理的程序一般都比较大,为了保证这个信号处理系统的通用性和可移植性,需把程序保存在主机中,用HPI总线自举。HPI是一个8位的并行口,PC机和'5402通过共享的片内存储器交换信息。选用HPI自举方式,需要把HINT和INT2引脚连在一起。复位时,Bootload使HINT置位,从而使 INT2置位。BootloaD读出中断标志寄存器(IFR)的bit2位后,即能从HPI口进行自举。与别的54X系列一个很重要的不同是:5402要检查数据存储器的OX7FH位以决定程序的入口地址,用户程序也要在复位完成后才能加载到HPI的RAM中。 5 驱动程序 因为PCI2040扩展了配置空间,所以,要通过 HPI口实现与DSP的通信,需要驱动程序。如果直接使用DDK来编写PCI设备的驱动程序,需要大量的Windows底层的知识,难度比较大。因此可以使用别的驱动程序的编写工具,如Vtools和 WinDrive。我们选用了WinDrive 。Jungo公司的WinDrive与其他驱动程序开发工具的最大不同是它可以在编程者不太了解Windows内核的情况下编写驱动程序。这样,可以把精力主要放在功能的实行上,同时用WinDrive写成的驱动程序只需作很少的修改就能很方便地适用于各种操作系统,如Win dows 9x, Window 2000,Windows NT以及Linux等。编写过程如下:(1)用WinDrive 的Drive Wiz ard 工具查找所要编写驱动程序的PCI卡,并用CREATING INF FILE 产生INF 文件,然后添加新硬件;(2)对PCI卡上的配置寄存器,I/O空间,内存范围,中断,片内寄存器进行设置;(3)生成源代码,对它进行功能添加,主要是实现对DSP 片内SRAM的访问。 |

网友评论