CPLDОӘҝШЦЖәЛРД16О»ёЯҫ«¶ИКэЧЦөзС№ұнЙијЖ

·ўІјКұјдЈә2010-6-25 16:21

·ўІјХЯЈәzealot

|

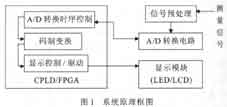

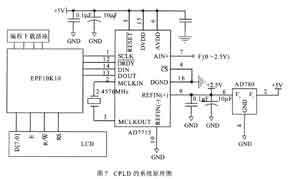

1 ТэСФ CPLD ( Complex Programmable Logic Device ) КЗРВРНөДҝЙұаіМВЯјӯЖчјюЈ¬Улҙ«НіASICПаұИЈ¬ҫЯУРЙијЖҝӘ·ўЦЬЖЪ¶МЎўЙијЖЦЖФміЙұҫөНЎўҝӘ·ў№ӨҫЯПИҪшөИУЕөгЈ¬МШұрККәПУЪІъЖ·өДСщЖ·ҝӘ·ўәНРЎЕъБҝЙъІъЎЈҙ«НіөДКэЧЦөзС№ұн¶аТФөҘЖ¬»ъОӘҝШЦЖәЛРДЈ¬РҫЖ¬јҜіЙ¶ИІ»ёЯЈ¬ПөНіБ¬ПЯёҙФУЈ¬ДСТФРЎРН»ҜЈ¬УИЖдФЪІъЖ·РиЗу·ўЙъұд»ҜКұЈ¬І»өГІ»ЦШРВІј°жЎўөчКФЈ¬ФцјУБЛН¶ЧК·зПХәНіЙұҫЎЈ¶шІЙУГCPLDҪшРРІъЖ·ҝӘ·ўЈ¬ҝЙТФБй»оөШҪшРРДЈҝйЕдЦГЈ¬ҙуҙуЛх¶МБЛҝӘ·ўЦЬЖЪЈ¬ТІУРАыУЪКэЧЦөзС№ұнПтРЎРН»ҜЎўјҜіЙ»ҜөД·ҪПт·ўХ№ЎЈ 2ПөНіФӯАнј°ЧйіЙ ПөНіЧйіЙФӯАнҝтНјИзНј1ЛщКҫЎЈПөНіөДҝШЦЖәЛРДКЗТ»Ж¬CPLDРҫЖ¬Ј¬ЛьУЙИэёц№ҰДЬДЈҝй№№іЙЈә A/DЧӘ»»КұРтҝШЦЖДЈҝйЎўВлЦЖұд»»ДЈҝйТФј°ПФКҫҝШЦЖ/Зэ¶ҜДЈҝйЎЈИэёцДЈҝйөД№ҰДЬ·ЦұрОӘ·ўіцҝШЦЖРЕәЕЖф¶ҜA/DЧӘ»»ј°¶БИЎІЙСщЦөЎў¶ФADІЙСщЦөҪшРРВлЦЖЧӘ»»Ўў·ўіцҝШЦЖРЕәЕЗэ¶ҜLED/LCDПФКҫПаУҰКэҫЭЎЈ

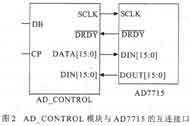

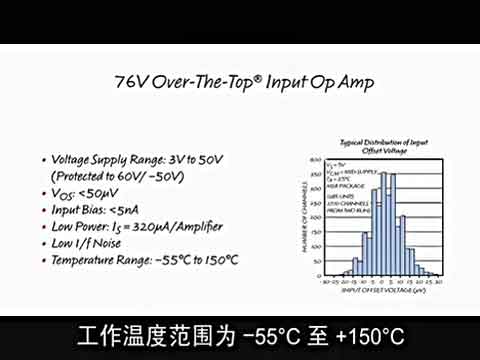

ПөНі№ӨЧчФӯАнЈәІвБҝРЕәЕҫӯ№эРЕәЕФӨҙҰАнЈ¬ұд»»ОӘ0Ў«2.5V·¶О§ДЪөДУРР§РЕәЕәуЛНИлA/DЧӘ»»өзВ·ЦРЈ¬И»әуA/DЧӘ»»КұРтҝШЦЖДЈҝй·ўіцҝШЦЖРЕәЕЈ¬Жф¶ҜA/DЧӘ»»ЖчҪшРРЧӘ»»Ј¬A/DІЙСщөГөҪөДКэЧЦРЕәЕФЪВлЦЖұд»»ДЈҝйЦРЧӘ»»ОӘПаУҰөДПФКҫҙъВлЈ¬ЧоәуҫӯПФКҫҝШЦЖ/Зэ¶ҜДЈҝй·ўіцҝШЦЖУлЗэ¶ҜРЕәЕЈ¬НЖ¶ҜНвІҝөДПФКҫДЈҝйЈЁLED/LCDЈ©ПФКҫПаУҰөДКэҫЭЎЈ 3CPLD№ҰДЬДЈҝйЙијЖ ЦЗДЬКэЧЦөзС№ұнөДҝШЦЖәЛРДCPLDөДИэёц№ҰДЬДЈҝйҪФУГVHDLУпСФұаіМКөПЦЈ¬ПВГжЦчТӘҪйЙЬCPLDөДИэёц№ҰДЬДЈҝйөДЙијЖЎЈ 3.1 A/DЧӘ»»КұРт·ВХжДЈҝйAD_CONTROL ANALOG DEVICES№«ЛҫЙъІъөДAD7715КЗТ»Ж¬16О»өДЎЖ-ҰӨ ADCјҜіЙөзВ·ЎЈЛьөДЦчТӘМШРФУРЈә3V/5V№ӨЧчөзС№Ј¬өҘЈҜЛ«ј«РФКдИлЈ»ҝЙұаіМёДұдФцТжОӘ1Ј¬2Ј¬32Ј¬128ұ¶Ј»ФЪөҘј«РФКдИлЧҙМ¬ПВДЈДвөзС№КдИл·¶О§ФКРнОӘ0Ў«20mV, 0Ў«80mV, 0Ў«1.25V, 0Ў«2.5VІ»өИЈЁУРАыУЪМбёЯҫ«¶ИЈ©Ј»ИэПЯҙ®РРҪУҝЪЈ»Ц§іЦІо·ЦКдИлЈ»өН№ҰәДЈЁ450 mF [email=Max@3V]Max@3V[/email]Ј©ЎЈФЪұҫПөНіЦРAD7715өДЧчУГКЗҪ«0~2.5VөДКдИлДЈДвРЕәЕЧӘ»»ОӘ16О»өДёЯҫ«¶ИөДКэЧЦРЕәЕ№©CPLDҙҰАнЎЈAD_CONTROLДЈҝйУГУЪҝШЦЖAD7715өДЖф¶ҜЎў¶БЎўРҙөИІЩЧчЎЈЙијЖөДAD_CONTROLДЈҝйИзНј2ЛщКҫЈ¬ЖдVHDLУпСФөДENTITY¶ЁТеІҝ·ЦИзПВЈә ENTITY AD_CONTROL IS PORT( SCLK:OUT STD_LOGIC; DRDY:IN STD_LOGIC; DOUT:OUT STD_LOGIC_VECTOR(15 DOWNTO 0); DIN:IN STD_LOGIC_VECTOR(15 DOWNTO 0); DB:OUT STD_LOGIC_VECTOR(15 DOWNTO 0); CP:IN STD_LOGIC ); END AD_CONTROL;

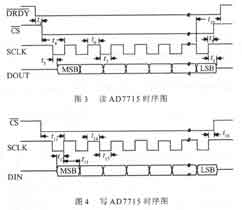

ИзНјЛщКҫЈ¬¶юХЯөДҪУҝЪРЕәЕПЯЦұҪУБ¬ҪУІўУЙAD_CONTROLДЈҝйДЈДвІъЙъAD7715РҫЖ¬өДёчёцҪУҝЪРЕәЕЈ¬НкіЙADCөДЖф¶ҜЎў¶БЎўРҙІЩЧчЎЈAD7715өД№ӨЧчДЈКҪУЙДЪІҝјДҙжЖчЈЁCommunications RegisterЈ¬Setup RegisterЈ¬Test RegisterЈ¬Data RegisterЈ©ЦРөДҝШЦЖЧЦҫц¶ЁЎЈДЪІҝјДҙжЖчөДКэҫЭРҙИләН¶Біц¶јУЙCSЈ¬DRDYЈ¬SCLKРЕәЕҝШЦЖЎЈөұ AD7715ұ»·ГОККұЈ¬SCLKҪЕУҰіцПЦТ»ҙОҙшЙПЙэСШөДёЯөзЖҪЈ¬ЖдКұЦУЖөВКУҰОӘ9.2kHzЎЈХвКЗ№ШјьРЕәЕЈ¬ЖдЛыРЕәЕҫщТФҙЛРЕәЕЧчОӘКұ»щЎЈТтҙЛЈ¬CPLDЦРөДAD_CONTROLДЈҝйөД№ҰДЬЦ®Т»ҫНКЗМṩSCLK ТФј°ЖдЛыРЕәЕөДСПёсКұРтЎЈНј3ЎўНј4·ЦұрОӘAD_CONTROLДЈҝй¶БЎўРҙAD7715КұРтНјЎЈ

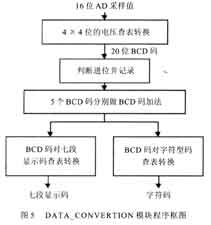

3. 2 ВлЦЖұд»»ДЈҝйDATA_CONVERSION ФЪҙЛВлЦЖұд»»ДЈҝйDATA_CONVERSIONЦРЦчТӘКөПЦөД№ҰДЬКЗҪ«ADІЙСщЛНАҙөД16О»өД¶юҪшЦЖКэЧӘ»»ОӘҝЙұ»LED/LCDК¶ұрөДЖЯ¶ОLEDПФКҫВл»тЧЦ·ыРНLCDВлЎЈФЪұҫПөНіЦРҙЛДЈҝй°ьә¬БЛХвБҪЦЦЧӘ»»№ҰДЬТФККУҰПФКҫ¶ЛІ»Н¬өДЕдЦГЎЈОӘБЛҙпөҪХвТ»ДҝөДЈ¬КЧПИТӘҪ«16О»¶юҪшЦЖВлұд»»ОӘBCDВлЈ¬И»әуФЩ·ЦұрҪшРРЧӘ»»Ј¬өГөҪЖЯ¶ОПФКҫВлј°ЧЦ·ыРНВлЎЈФЪҙЛДЈҝйЦРёчёцBLOCKІҝ·ЦөДВлЦЖұд»»өДVHDLіМРтҝЙНЁ№эWHEN-ELSEУпҫдҪшРРІйұнАҙКөПЦЎЈЧӘ»»өД№эіМИзНј5ЛщКҫЎЈ

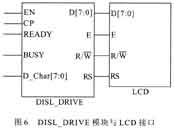

3.3 ПФКҫҝШЦЖј°Зэ¶ҜДЈҝйDISL_DRIVE өзС№ЦөөДПФКҫҝЙУЙLED»тLCDКөПЦЎЈФЪұҫПөНіЦР¶ФУЪөзС№ЦөөДПФКҫ·ЦОӘmVәНVБҪөөЈ¬ЛщТФРиТӘФЪәуГжјУЙПөҘО»АҙГчИ·Ј¬ЗТұҫПөНіОӘөН№ҰәДПөНіЈ¬ИфУГLEDФт№ҰәДПа¶Ф№эҙуЈ¬ЛщТФСЎУГБЛТ»ҝй8ЎБ2ЧЦ·ыРНТәҫ§ПФКҫДЈҝйMDSL81809-03Ј¬КөПЦБЛөН№ҰәДЈ¬¶шЗТҝЙҙшөҘО»Л«ЕЕПФКҫЈ¬ЧЦМеГА№Ыҙу·ҪЎЈ DISL_DRIVEКҫЈ¬ХыёцөзВ·К®·ЦјтҪаЎЈПөНі№ӨЧч№эіМКЧПИУЙ CPLD¶ФAD7715ј°LCDҪшРРіхКј»ҜЈ¬И»әуөұУРКдИлРЕәЕV iЈЁ0Ў«2.5VЈ©өҪAIN+¶ЛәуЈ¬УЙCPLDНЁ№эҪУҝЪПтAD7715өДјДҙжЖчЦРРҙИлҝШЦЖЧЦЈ¬К№Жд¶ФКдИлөДДЈДвРЕәЕҪшРРЧӘ»»Ј¬ұдОӘ16О»өДКэЧЦРЕәЕЛНөҪDOUT¶ЛЈ¬УЙCPLDҫӯ№эВлЦЖұд»»өИҙҰАнәуЈ¬ФЩНЁ№эУлLCDөДҪУҝЪЗэ¶ҜІў·ўЛНКэҫЭЈ¬Ҫ«өзС№Цөј°өҘДЈҝйУлLCDөДҪУҝЪИзНј6ЛщКҫЎЈНјЦРLCDөДRS¶ЛРиКдИл·ҪІЁЗэ¶ҜЈ¬ХвҝЙУЙCPLDұаіММṩЎЈөұAD7715ІЙСщНкіЙәу,УЙDATA_CONVERSIONДЈҝйҪ«ІЙСщКэЧЦРЕәЕЧӘ»»ОӘLCDҝЙК¶ұрөДЧЦ·ыРНКэҫЭәуЈ¬ЛНЦБDISL_DRIVEДЈҝйЈ¬ФЩУЙЖдЗэ¶ҜLCDЈ¬Ҫ«ЧЦ·ыРНКэҫЭЛНөҪLCDөДD0~D7¶ЛЈ¬КөПЦПФКҫЎЈ

4ПөНіЙијЖәНВЯјӯ·ВХж CPLDөДИэёц№ҰДЬДЈҝйУГVHDLУпСФГиКцЈ¬ҪшРРЧЫәП·ВХжәуБ¬ҪУЖрАҙөДПөНіөзВ·ФӯАнНјИзНј7ЛщО»ПФКҫФЪLCDЙПЎЈ

ұҫПөНіІЙУГөДCPLDРҫЖ¬ОӘALTERA№«ЛҫөДEPF10K10LC84-4РҫЖ¬Ј¬ВЯјӯГЕКэОӘ10000ГЕЈ¬УГMAX+PLUSўт10.0Инјю№ӨҫЯҝӘ·ўЎЈЙијЖКдИлНкіЙәуЈ¬ҪшРРХыМеөДұаТләНВЯјӯ·ВХжЈ¬И»әуҪшРРЧӘ»»ЎўСУКұ·ВХжЙъіЙЕдЦГОДјюЈ¬ЧоәуПВФШЦБCPLDЖчјюЈ¬НкіЙҪб№№№ҰДЬЕдЦГЈ¬КөПЦЖдУІјю№ҰДЬЎЈ 5 ЧЬҪб ұҫПөНіКЗУГCPLDКөПЦөДЦЗДЬКэЧЦөзС№ұнЎЈЛжЧЕEDAјјКхөД№г·әУҰУГЈ¬CPLDТСіЙОӘПЦҙъКэЧЦПөНіЙијЖөДЦчТӘКЦ¶ОЈ¬CPLDДҝЗ°ХэіҜЧЕёьёЯЛЩЎўёьёЯјҜіЙ¶ИЎўёьЗҝ№ҰДЬәНёьБй»оөД·ҪПт·ўХ№ЎЈ |

НшУСЖАВЫ