研究人员以碳纳米管实现真正的3D芯片

发布时间:2014-12-23 10:58

发布者:eechina

|

美国史丹佛大学(Stanford University)的研究人员们在日前举办的2014年国际电子元件会议(IEDM)上展示了真正的 3D 晶片。大部份的 3D 晶片采用矽穿孔(TSV)的方式推叠不同的制造晶片,例如美光科技(Micron Technology)的混合记忆体立方体(HMC)推叠 DRAM 晶粒。 此外,总部设于美国奥勒冈州的新创公司BeSang将其专有制程技术授权给南韩的海力士半导体(SK Hynix Inc.),用于打造出无需透过 TSV 的真正 3D 技术。 然而,史丹佛大学所展示的是任何晶圆厂都能在标准的互补式金属氧化物半导体(CMOS)上堆叠任何层数的逻辑与记忆体。在IEDM上,史丹佛大学在 CMOS 晶片上堆叠了2层的金属氧化物电阻型随机存取记忆体(PRAM),以及1层利用碳奈米管(CNT)作为电晶体通道的逻辑电路。

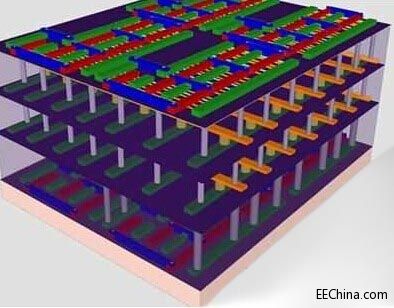

史丹佛大学展示的3D晶片以标准过孔方式连接4层电路,最底层是标准CMOS,最上层是碳奈米管逻辑电晶体,中间夹着2层RRAM。(来源:Stanford, Mitra/Wong Lab) “对于使用传统的跨层过孔而言, TSV 技术至关重要,但关键在于如果你想达到无法以 TSV 实现的极高能源密度效率之时,”史丹佛大学电子工程系教授Subhasish Mitra表示,“然而,我们能够利用传统过孔分别在各层之上顺利地打造这些电路层,显示我们的方法是可行的。” 史丹佛大学所采用的方法是在底层制造一种标准 CMOS 逻辑晶片,然后以二氧化矽绝缘体加以覆盖,并且利用氩气溅镀蚀刻的方式使其平面化。在第二层的 RRAM 是由氮化钛、氧化铪(作为主动交换层)和铂组成,然后在 CMOS 层上以200℃的温度利用传统 TSV进行制造(以免损坏 CMOS ),以实现互连。 然后,在经过 PRAM 以及另一层绝缘二氧化矽沈积后,另一层绝缘二氧化矽则沈积于 RRAM 之上并实现平面化。最上层则先以碳奈米管进行同向覆盖,利用剥离(lift-off)方式形成石英晶片。为了实现足够的密度,研究人员们进行13次的碳奈米管转换方式。然后再用传统的内层过孔(ILV)与微影技术,将碳奈米管制造于逻辑层上的电晶体通道中。 “我们可以利用这种技术制造出任意层数,”史丹佛大学教授H.S. Philip Wong说:“我们使用相当宽松的设计规则在学校的晶圆厂中制造这些电路层,但在其他的展示中则已证明我们的制程能一直微缩到现有采用过孔技术的20nm商用级。”

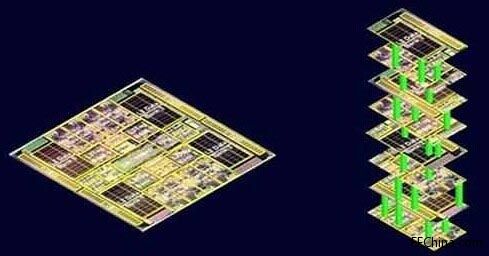

标准的平面型CMOS晶片(图左)透过TSV分别堆叠逻辑元件与记忆体于不同的结构;史丹佛大学的工程师为采用标准TSV的CMOS晶片上3层结构进行低温制程,以实现更高密度。 史丹佛大学的研究人员们还积极地展示在平面二氧化矽表面的碳奈米管性能,这是在平行碳奈米管上层利用标准图形化技术,在场效电晶体(FET)中形成每通道约 50个奈米管。研究人员们认为,这种碳奈米管电晶体由于具备较矽晶更高10倍的能效,因而可望在未来取代矽晶电晶体技术。 “我们想表达的是你可以先以标准矽晶 CMOS 作为底层,仍然能够打造出 3D 晶片,但在未来,我们希望人们转换成利用碳奈米管电晶体,因为他们的性能可进一步扩展到超越矽晶,这就是为什么我们展示真正的碳奈米管电路,而不只是堆叠上的一个测试电晶体。” 研究团队们强调,必须确保这种碳奈米层在温度够低的情况下制造,才不至于损坏 PRAM ,而在足够的低温下制造 PRAM ,才不会损坏到底层的 CMOS 晶片。数以千计的过孔实现各层的互连,才能使得这种碳奈米管场效电晶体(CNTFET)成为 PRAM 的理想选择。 |

网友评论