ЛљгкEMIFНгПкЕФDSPПижЦЯЕЭГЩшМЦ

ЗЂВМЪБМфЃК2014-12-22 14:31

ЗЂВМепЃКdesignapp

|

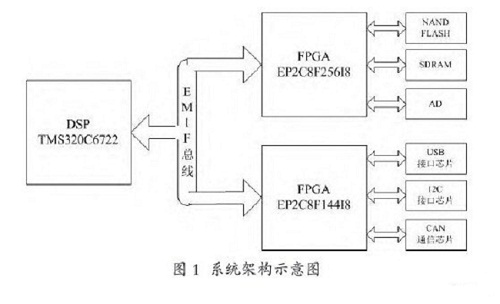

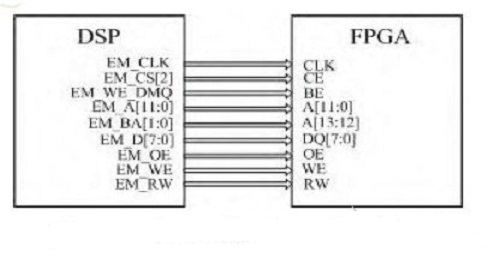

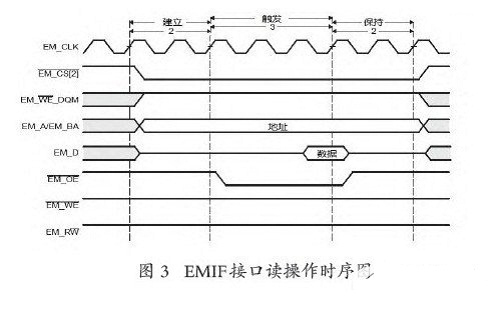

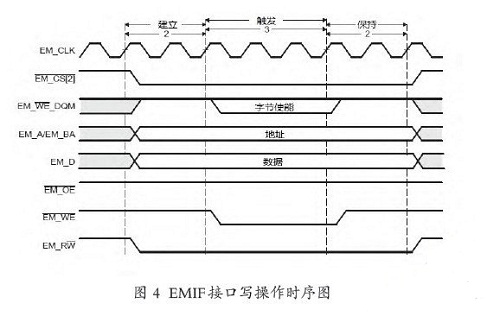

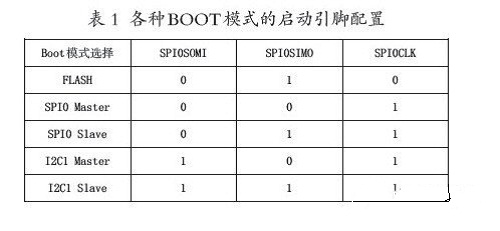

1 в§бд ЫцзХаХЯЂММЪѕЕФЗЂеЙЃЌЪ§зжаХКХДІРэММЪѕГЩЮЊЪ§зжЛЏЩчЛсзюживЊЕФММЪѕжЎвЛЁЃгЩгкЪ§зжаХКХДІРэЦїЃЈDSPЃЉЫйЖШПьЃЌЮШЖЈадИпЃЌЙІКФаЁЃЌНќаЉФъРДдкЭЈаХЁЂЭМЯёДІРэЁЂздЖЏПижЦЕШСьгђжаЕУЕНСЫЙуЗКЕФгІгУЁЃЦфжаЃЌУРЙњЕТжнвЧЦїЕФTMS320ЯЕСаDSPеМОнСЫЪРНчDSP ЪаГЁЕФжївЊЗнЖюЃЌTIвВвђДЫГЩЮЊСЫЪРНчЩЯзюДѓЕФDSPжЦдьЩЬЁЃБОЯЕЭГВЩгУСЫTMS320C6722ИЁЕуаЭDSPаОЦЌЁЃ EMIFНгПкЃЈExternal Memory InterfaceЃЉЪЧTMS320ЯЕСаDSPЩЯОпгаЕФвЛжжИпЫйНгПкЃЌЦфЩшМЦГѕждЪЧЪЕЯжDSPгыВЛЭЌРраЭЕФЭтВПРЉеЙДцДЂЦїЃЈШч SDRAMЃЌFLASHЕШЃЉжЎМфЕФИпЫйСЌНгЁЃдкЕБЧАЕФвЛаЉгІгУжаЃЌЮЊСЫИќГфЗжЕФгІгУDSPЕФдЫЫуФмСІЃЌРЉеЙЦфв§НХзЪдДЃЌЙЄГЬЪІУЧГЃгУEMIFНгПкСЌНгFPGAЃЌдйЭЈЙ§FPGAгыЖржжЭтВПЩшБИЯрСЌЁЃетбљЃЌFPGAГЩЮЊСЫвЛИіжазЊеОЃЌИїжжЪ§зжаОЦЌЕФЪ§ОнЖМПЩвдЭЈЙ§FPGAДЋЪфжСDSP.ЖдгкИќМгИДдгЕФЯЕЭГЃЌЕБвЛПщFPGAаОЦЌЕФв§НХзЪдДЖМБЛгУОЁЪБЃЌПЩвддкDSP ЕФEMIFНгПкЩЯСЌНгЖрПщFPGAаОЦЌЃЌдйНЋЙІФмИївьЕФаОЦЌСЌНгжСFPGAЁЃетбљЃЌDSPаОЦЌНіЭЈЙ§EMIFНгПкОЭФмЪЕЯжЖдИДдгЯЕЭГЕФПижЦЁЃ 2 ЛљгкEMIFНгПкЕФDSP+FPGAЯЕЭГЪЕЯж 2.1 ЯЕЭГМмЙЙ ЁЁЁЁ  ЭМ1 ЪЧБОШЫЫљЪЙгУЕФЯЕЭГЃЌDSPаОЦЌЭЈЙ§EMIFНгПкСЌНгСЫ2 ЦЌFPGAЃЌЦфжаEP2C8F256I8 жївЊИКд№DSPКЫаФДІРэЫљашЪ§ОнЕФНЛЛЛЃЌСЌНгСЫFLASH аОЦЌЃЌSDRAMаОЦЌЃЌA/D аОЦЌЁЃСэвЛПщFPGA аОЦЌEP2C8F144I8 ИКд№гыЭтВПЭЈаХЃЌСЌНгСЫUSB НгПкаОЦЌЃЌI2CЭЈаХаОЦЌКЭCANзмЯпЭЈаХаОЦЌЁЃ TMS320C6722 аЭDSPЕФEMIFНгПкЩшМЦГѕждЪЧгыЭтВПРЉеЙДцДЂЦїСЌНгЃЌEMIFНгПкгаСНжжЙЄзїЗНЪНЃКSDRAMЙЄзїФЃЪНгывьВНЙЄзїФЃЪНЁЃSDRAMЙЄзїФЃЪНЪЧзЈЮЊ SDRAMЩшМЦЕФЭЌВНЙЄзїФЃЪНЃЌEMIFНгПкФмздЖЏИјSDRAMНјааЫЂаТЃЛвьВНЙЄзїФЃЪНЪЧгыSRAMЁЂFLASHЕШвьВНЦїМўЙЄзїЪБВЩгУЕФФЃЪНЁЃ  ЁЁЁЁ ЭМ2 ЫљЪОЪЧDSPгывЛЦЌFPGAЕФНгПкСЌНгЭМЃЌDSPгыЖрЦЌFPGAСЌНгЪБЃЌНгПкПЩвдАДЭМЕФЗНЪНИДгУЃЌTMS320C6722аЭDSPЕФEMIFНгПкга14ИљЕижЗЯпЃЌгыВЛЭЌFPGAНјааЭЈаХЪБЃЌвЊЪЙгУВЛЭЌЕФЕижЗЁЃ 2.2 DSP гыFPGA ЭЈаХЪБађ 2.2.1 вьВНЖСВйзї DSPЗЂГіЖдFPGAЕФЖСЩъЧыЪБЃЌОЭЛсНјаавьВНЖСВйзїЁЃЕБЖСВйзїВЛФмдкЭтВПЦїМўЕФвЛИіЗУЮЪжмЦкФкЭъГЩЪБЃЌEMIFОЭЛсНјааЖрИіжмЦкЕФВйзїЃЌжБЕНЭъГЩећИіЩъЧыЁЃ  вЛИіEMIFЖСВйзїЗжЮЊНЈСЂЪБМфЁЂДЅЗЂЪБМфКЭБЃГжЪБМфШ§ВПЗжЁЃдкНЈСЂЪБМфПЊЪМЪБЃЌEM_CSЃл2ЃнЦЌбЁаХКХРЕЭЃЌЭЌЪБЕижЗЯпEM_AгыEM_BAИјГіЫљЖСШЁЪ§ОнЕФЕижЗЁЃДЅЗЂЪБМфПЊЪМЪБЃЌEM_OEаХКХРЕЭЃЌЭЌЪБFPGAдкEM_DаХКХЯпЩЯДЋЪфЪ§ОнЃЌDSPНЋдкДЅЗЂЪБМфЕФзюКѓвЛИіЪБжгДІЖдЪ§ОнВЩбљЁЃБЃГжЪБМфжаEM_OE аХКХНЋРИпЃЌВЂдкБЃГжЪБМфНсЪјКѓЃЌEM_CSЃл2ЃнаХКХРИпЁЃдкећИіжмЦкжаEM_WE_DQMЁЂEM_WEЁЂEM_RWаХКХЪМжеЮЊИпЕчЦНЁЃ 2.2.2 вьВНаДВйзї DSPЗЂГіЖдFPGAЕФаДЩъЧыЪБЃЌОЭЛсНјаавьВНаДВйзїЁЃЕБаДВйзїВЛФмдкЭтВПЦїМўЕФвЛИіЗУЮЪжмЦкФкЭъГЩЪБЃЌEMIFОЭЛсНјааЖрИіжмЦкЕФВйзїЃЌжБЕНЭъГЩећИіЩъЧыЁЃ  ЁЁЁЁ РрЫЦгкЖСВйзїЃЌEMIF аДВйзїЗжЮЊНЈСЂЪБМфЁЂДЅЗЂЪБМфКЭБЃГжЪБМфШ§ВПЗжЁЃдкНЈСЂЪБМфПЊЪМЪБЃЌEM_CSЃл2ЃнЦЌбЁаХКХРЕЭЃЌEM_RWаХКХРЕЭЃЌЭЌЪБЕижЗЯпEM_AгыEM_BAИјГіЫљЖСШЁЪ§ОнЕФЕижЗЃЌЪ§ОнЯпEM_D ИјГіашвЊаДШыFPGAЕФЪ§ОнЁЃДЅЗЂЪБМфПЊЪМЪБЃЌEM_WEаХКХРЕЭЃЌEM_WE_DMQаХКХИјГізжНкЪЙФмаХКХЁЃБЃГжЪБМфПЊЪМЪБEM_WE_DMQаХКХгы EM_WEаХКХРИпЃЌВЂдкБЃГжЪБМфНсЪјКѓЃЌEM_CSЃл2ЃнаХКХгыEM_RWаХКХРИпЁЃдкећИіаДВйзїжмЦкжаEM_OEаХКХЪМжеЮЊИпЕчЦНЁЃ DSP ЭЈЙ§ХфжУEMIF НгПкЕФМФДцЦїРДЪЕЯжЩЯЪіЪБађЃЌFPGAПЩВЩгУIP КЫРДЪЕЯжEMIFавщЃЌВЛЭЌЕФFPGAаОЦЌвЊВЩгУВЛЭЌЕФЕижЗЁЃ 3 ЯЕЭГBOOTЗНЗЈ TMS320C6722 аЭDSPЕФФкВПУЛгаПЩаДЕФROMЃЌDSPЕФГЬађБиаыДцЗХдкЭтВПЦїМўжаЃЌDSPаОЦЌЩЯЕчКѓБиаыЪзЯШДгЭтВПаОЦЌЯТдиГЬађЁЃБОПюDSPПЩвдЭЈЙ§SPIзмЯпЦєЖЏЁЂЭЈЙ§I2CзмЯпЦєЖЏКЭЭЈЙ§EMIFНгПкЦєЖЏЁЃетМИжжBootЗНЪНКЭЖдгІЕФв§НХХфжУШчБэ1ЫљЪОЃЌдкБОЯЕЭГжаЃЌEMIFНгПкГ§СЫЪЕЯжЭЈГЃЕФЪ§ОнНЛЛЛЃЌЛЙМцШЮДјЖЏDSPЦєЖЏЕФЙІФмЁЃ  ЁЁЁЁ ЯЕЭГЩЯЕчКѓЃЌDSPЕФRESETв§НХвЊЭЈЙ§ЯТРЕчзшРЕЭЃЌЪЙDSP ДІгкИДЮЛЬЌЁЃFPGAаОЦЌEP2C8F256I8ЩЯЕчКѓДгFPGA ХфжУаОЦЌEPCS4жаЯТдиГЬађЦєЖЏЁЃFPGAЦєЖЏГЩЙІКѓНЋDSPаОЦЌЕФSPI0SOMIв§НХгыSPI0CLKв§НХРЕЭЃЌНЋSPI0SIMOв§НХРИпЃЌШЛКѓдйНЋRESETв§НХРИпЁЃетбљХфжУЪЧЮЊСЫЪЙDSPЭЫГіИДЮЛЬЌЪБФмИљОнЩЯЪі3Иів§НХЕФЕчЦНЛёжЊDSPаОЦЌНЋЭЈЙ§EMIFНгПкЦєЖЏЁЃДЫКѓЃЌDSPаОЦЌНЋДгEMIFНгПкЖСШЁ1KBЪ§ОнЃЌВЂНЋет1KBЪ§ОнДцЗХгкDSPЕФRAMжаЃЌдйжДаает1KBЕФГЬађЁЃ ЩЯЪіЙ§ГЬГЦЮЊDSPЕФЕквЛДЮЦєЖЏЙ§ГЬЁЃет1KBЕФГЬађЪЧгЩЛуБргябдБраДВЂЭЈЙ§CCStudio ШэМўБрвыГЩЛњЦїгябдЃЌДцЗХгкFPGAжаЃЈЭЈЙ§mif ЮФМўБрвыНјFPGAЕФГЬађЃЉЁЃИУ1KBГЬађЕФЙІФмЪЧдйДЮЕїгУEMIF НгПкЃЌВйзїFPGAЃЌЪЙЕУFPGA ЭЈЙ§IP КЫДгFLASHаОЦЌжаНЋЦфгрЕФГЬађЃЈБОЯЕЭГЕФГЬађдМЮЊ32KЃЉПНШыDSPЕФRAM жаВЂжДааетаЉаТПНШыЕФГЬађЁЃетЪЧDSP ЕФЕкЖўДЮЦєЖЏЁЃЕквЛДЮЦєЖЏЪЧгВМўЦєЖЏЃЌЪЧTMS320C6722 аЭDSPвбОЩшЖЈКУЕФЦєЖЏЗНЪНЃЌЕкЖўДЮЦєЖЏЪЧШэМўЦєЖЏЃЌЫљжДааЕФЦєЖЏГЬађгЩгУЛЇБраДЁЃ злЩЯЃЌБОЮФНщЩмСЫDSPаОЦЌЭЈЙ§EMIFНгПкСЌНгFPGAЕФгВМўЕчТЗгыЪБађЃЌИљОнБОЮФНщЩмЕФЗНЗЈЃЌDSPаОЦЌЭЈЙ§FPGAФмПижЦДѓСПЭтВПаОЦЌЙЄзїЃЌНіЪЙгУDSPЕФEMIFНгПкОЭФмЪЕЯжDSPЦєЖЏКЭПижЦИДдгЯЕЭГЙЄзїЕФЙІФмЃЌДѓДѓРЉеЙСЫDSPаОЦЌЕФСщЛюадЃЌЪЙЦфЧПДѓЕФдЫЫуЙІФмЕУвдИќКУЕФЗЂЛгЁЃ |

ЭјгбЦРТл