基于FPGA的线阵CCD子图像提取模块的设计与仿真

发布时间:2014-12-17 15:42

发布者:designapp

|

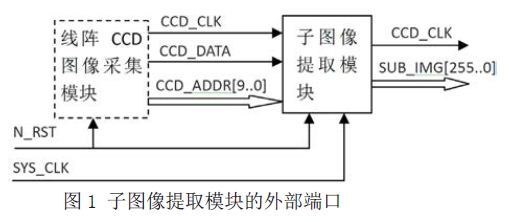

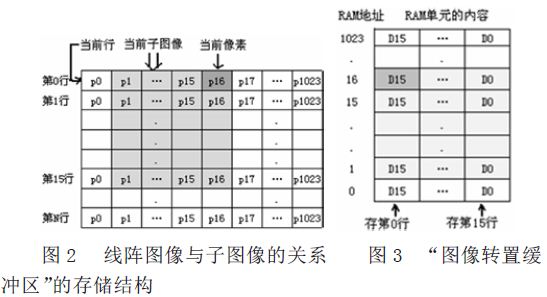

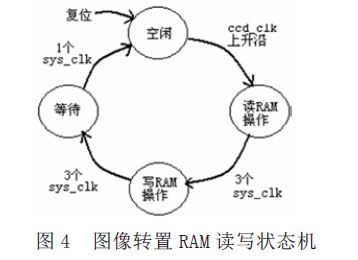

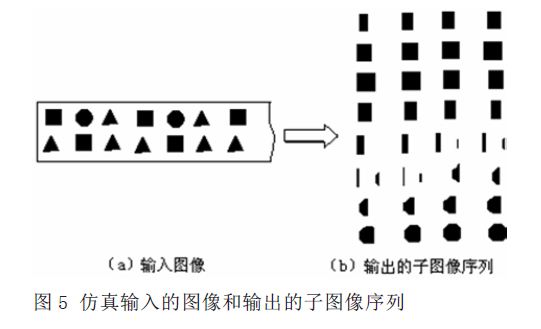

0 引言 在工业生产自动化系统中,通过计算机视觉和图像处理技术来实现产品的质量监测和控制,已逐渐成为一种有效的应用技术。线阵CCD图像传感器广泛地应用于产品尺寸测量和分类、非接触尺寸测量、条形码、形态识别等众多领域。在图像检测系统中,应具备一个高速的子图像提取和输出模块,本文采用FPGA器件EP3C25F256C8和CCD线阵图像传感器RL1024P,实现线阵CCD图像检测系统中的子图像提取和输出功能。 1 子图像提取模块的设计 子图像提取模块的功能可描述为:采用FPGA器件实现,根据串行输入的黑白图像和同步信号,提取该图像中设定尺寸大小的子图像。假设输入图像大小为i*j,某一像素点的坐标位置为(X,Y),要取出子图像的大小为m*n,则用c代码描述为:for(b=0;b 根据系统设计的要求,线阵CCD图像采集模块采用串行的方式输出1×1024像素的一行图像,子图像提取模块接收该图像数据、缓冲、再输出16×16像素的子图像。子图像提取模块的外部端口,如图1所示。主要信号有:像素同步时钟信号CCD_CLK、像素数据CCD_DATA、当前输入像素的坐标CCD_ADDR[90];另外,N_RST和SYS_CLK为系统提供的复位信号和处理时钟信号。其中,每个CCD_CLK的上升沿出现时CCD_DATA像素有效,且该像素所在的位置为CCD_ADDR[90]值。  为了实现每个CCD_CLK周期内均输出一个子图像,SYS_CLK应该为CCD_CLK的10倍左右。 本文采用“图像转置缓冲区”的方法来实现子图像提取模块。“图像转置缓冲区”是一个按行写入(更新)、按列读出的一个RAM缓冲区。在FPGA内部设置一个1024个单元的RAM缓冲区,每个单元的位宽为16bits.线阵CCD采集模块输出的线阵图像与子图像的关系,如图2所示。其中,第0行表示图像的当前行,第N行为历史行,每行有1024个像素,按照p0至p1023的像素顺序输出。假设当前CCD_CLK输入的像素为第0行的p16像素,则其对应的16X16子图像为图中的阴影部分。 “图像转置缓冲区”RAM块存储图像的结构,如图3所示。  RAM块共有1024个单元,每个单元为16位的宽度,可存放最近的16行图像数据。对比图2和图3,可以发现,RAM块的地址编号相当于线阵CCD图像的某一行像素的位置,某个RAM单元的位D15~D0对应某一列的最近16个像素,相当于对线阵图像转置后再存放到RAM块中。对RAM缓冲区进行写操作时,由于线阵CCD图像的数据是按行逐位输入的,每个CCD_CLK时钟上升沿出现时,仅需更新RAM缓冲区中当前像素对应的比特,因此在逻辑上是根据图像按行写入RAM区的。在FPGA器件中,可设计一个状态机来实现“图像转置缓冲区”的读写操作,如图4所示。  子图像提取模块输出的子图像有256个像素,在FPGA内部通过寄存器暂存上一个输出的子图像;当更新RAM区的某个像素时,把16X16的滑动窗口向右移动一列像素的位置,把滑动窗口内的数据作为输出,就可以得到新的子图像。 2 设计仿真 在本文的设计仿真中,由于用到图像文件的解析和图像显示,因此借助MATLAB和Modelsim软件,通过文件读写的方式实现的联合仿真,可使仿真处理更加便捷和直观。其中,MATLAB用来把图像文件转换为输入的像素,以及显示输出的子图像;Modelsim用来仿真和验证FPGA设计是否正确。  本文使用MATLAB和Modelsim进行联合仿真,主要有以下三个步骤。第一步,在MATLAB中编写m文件,读取bmp位图文件并把像素数据写入文件datain.txt中,作为ModelSim仿真的输入激励信号。第二步,在ModelSim中,用VHDL编写Testbench测试文件,读取datain.txt文件,产生与CCD_CLK同步的像素信号;编写DO文件进行自动化仿真,再把仿真输出的子图像数据保存在dataout.txt文件中。第三步,在MATLAB中编写m文件,解析dataout.txt文件,依次显示为16×16的黑白图片序列,确定仿真结果是否正确。本设计仿真输入的图像及输出的子图像序列,如图5所示。从仿真结果可知,设计方法是正确的,仿真结果符合设计功能的要求。 3 结束语 应用线阵CCD图像传感器进行产品检测时,连续、高速地输出子图像序列是必不可少的重要环节,采用FPGA实现子图像序列的提取和输出,有多种不同的设计方法。本文采用“图像转置缓冲区”和状态机的方式,来实现系统所要求的子图像提取和输出的功能,并用MATLAB和ModelSim工具软件对设计进行了联合仿真,该方法具有FPGA资源占用少、结构简单、高速处理,以及便捷和直观的特点,对其他类似的FPGA设计项目有很好的参考作用。 |

网友评论