PCB特性影响电源分配网络(PDN)性能

发布时间:2014-12-17 11:22

发布者:designapp

|

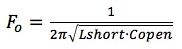

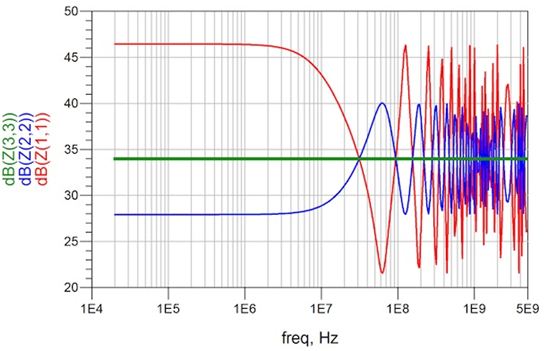

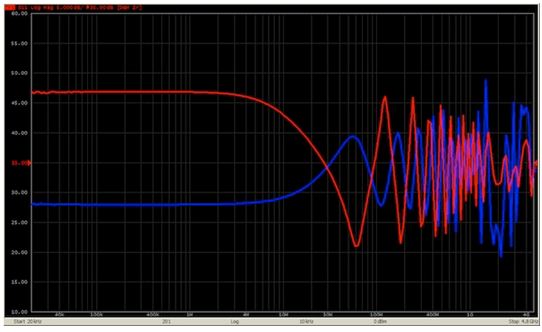

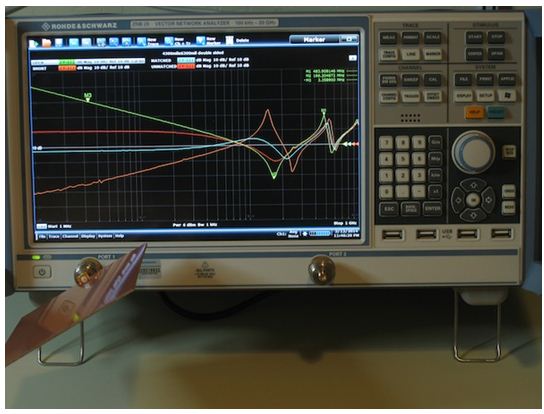

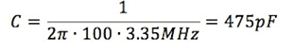

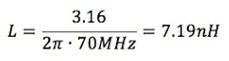

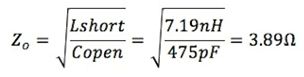

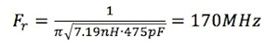

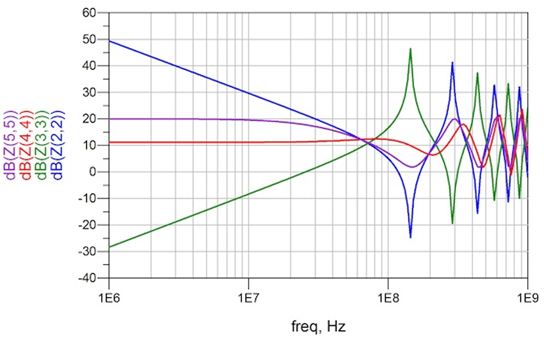

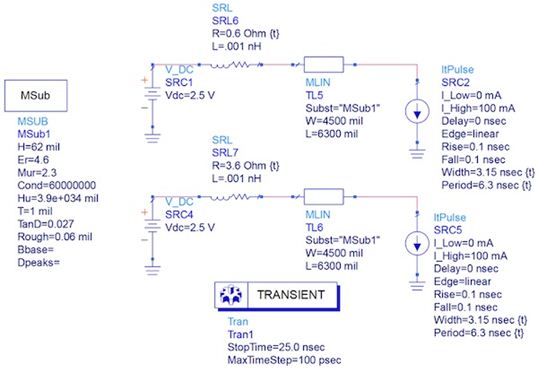

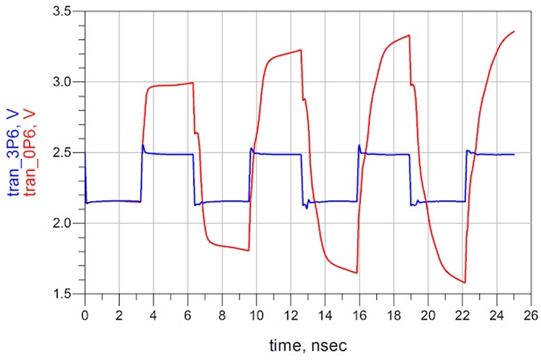

电源分配网络(PDN)的基本设计规则告诉我们,最好的性能源自一致的、与频率无关的(或平坦)的阻抗曲线。这是电源稳定性非常重要的一个理由,因为稳定性差的电源会导致阻抗峰值,进而劣化平坦的阻抗曲线,以及受电电路的性能。 由于没有阻抗路径是完全平坦的,所以我们需要做一些设计调整。本文旨在帮助你做出一些对系统性能影响最小的折衷。 源阻抗应该匹配传输线阻抗。 一般来说,这是S参数测量和所有射频设备的基本前提。源阻抗(最常见的是50Ω)连接到阻抗与源匹配的同轴电缆,负载也端接到相同的阻抗。这种做法实现了完美的平坦阻抗,不管是从源看到负载还是从负载看到源都是一致的。 稳压器的输出阻抗可以被认为是一个源,而PCB层可以看作是一根传输线。后端去耦电容就是负载。 传输线基本原理 当频率低于传输线谐振频率时,传输线特征阻抗可以用电感和电容项定义。电容可以在传输线远端没有端接时测量。电感可以在传输线远端短路时测量。传输线的特征阻抗取决于这两个测量结果,即:  (1) 电感和电容交叉点的频率就是特征阻抗,等于:  (2) 正确匹配的传输线呈现完全平坦的阻抗曲线,其幅度等于特征阻抗。不正确端接的传输线呈现为电容或电感性质,在传输线谐振频率的倍数处会产生许多谐振和抗谐振频率。如果传输线是电容性质,那么抗谐振首先发生。如果传输线是电感性质,那么谐振先发生。在两种情况下,首次谐振或抗谐振的频率为:  (3) 图1用50Ω同轴电缆仿真显示了这些关系。未端接终端阻抗是在电缆末端开路、短路和匹配端接的情况下测量的。  图1:传输线近端阻抗开路(蓝色)、短路(红色)和正确匹配(绿色),另外一种有趣的关系。 在传输线和源不匹配的情况下,有两种可能的解决方案,具体取决于端接电阻是大于还是小于特征阻抗。如果端接电阻小于传输线的特性阻抗,那么抗谐振峰值会超过端接电阻。这些阻抗峰值被定义为:  (4) 谐振最小值等于端接电阻。 如果端接电阻大于传输线的特征阻抗,那么谐振峰值等于端接电阻。抗谐振最小值被定义为:  (5) 利用前面端接电阻分别是24.9Ω和210Ω的仿真模型可以显示这些关系,图2中端接电阻是匹配的。  图2:传输线未端接终端阻抗24.9Ω(蓝色)、210Ω(红色)和正确匹配(绿色)。 这些关系在图3的对端接24.9Ω和210Ω的50Ω同轴电缆测量中得到了确认。  图3:对端接210Ω(红色)和24.9Ω(蓝色)的50Ω同轴电缆的测量结果。 这些概念被扩展到实际的一块双面印刷电路板,在这块PCB上面积为4.5” x 6.3”的裸铜箔中心焊接有一个SMA连接器,如图4所示。 图4:利用一块面积为4.5”x6.3” 、一个边有个SMA连接器的双面铜箔板测量PCB的开路(绿色)和短路(橙色)阻抗。该阻抗还用SMA连接器正对面的2.7Ω(蓝色)和10Ω(红色)端接电阻进行了测量。电阻用非常短的编带连接到PCB,以便尽量减小互连电感。  我们可以使用图4中的示波器测量结果近似计算PCB的特征阻抗。电容是用标记M3估计的。  电容用70MHz、10dBΩ的那个点估计。  利用(1)可以计算出特征阻抗为:  另外,特征阻抗可以看作是开路阻抗和短路阻抗的交叉点,发生在近似11.5dBΩ或3.76Ω点。 也可以使用(4)和带2.7Ω端接电阻的近似峰值阻抗(14.5dBΩ)计算PCB的特征阻抗。  重新变换计算Zo,  可以用(3)计算第一个谐振频率或抗谐振频率,即:  用3.6Ω的端接电阻重复进行测量,如图5所示。  图5:用3.6Ω代替2.7Ω端接电阻对同一块PCB进行测量(红色)。注意,在采用3.6Ω的端接电阻后,只有少量峰值指示其特征阻抗稍大于3.6Ω。 对PCB进行仿真并与图5进行比较,结果如图6所示。  图6:PCB仿真结果与图5所示的测量结果进行比较。 最后,使用电源端的0.6Ω和3.6Ω源阻抗并在PCB谐振频率点仿真动态瞬时响应。仿真模型见图7,仿真结果见图8.  图7:用0.6Ω和3.6Ω源阻抗代表稳压器输出阻抗,在谐振频率点进行动态负载瞬时ADS仿真。  图8:瞬时响应仿真结果表明,0.6Ω较低源电阻(红色) 的瞬时响应比匹配的3.6Ω源电阻(蓝色)具有大得多的电压偏移。 该视频演示端接电阻在PCB板上频域和时域的影响 小结 本文讨论了几种确定电路板特征阻抗的方法,并用仿真模型定义了PCB特征与PDN性能之间的重要关系。在经过实际测量后,关系得到了确认。 可以通过观察第一个缺陷是谐振点还是抗谐振点来判断PCB阻抗是否大于或小于端接阻抗,端接阻抗是否大于PCB阻抗。 这些结果清晰地表明,为了优化PDN性能,必须使PCB层阻抗与稳压器的输出阻抗相匹配。最好是使PCB层阻抗等于稳压器的输出阻抗,如果不可能实现的话,PCB阻抗应该低于稳压器输出阻抗,以便更好地包含与峰值阻抗最大值相关的峰值偏移。 |

网友评论