2.5 GbpsЪеЗЂЦїжа1ЁУ2НтИДгУЕчТЗЕФЩшМЦ

ЗЂВМЪБМфЃК2014-12-17 09:36

ЗЂВМепЃКdesignapp

|

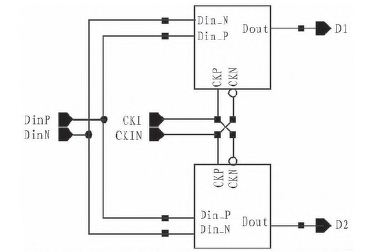

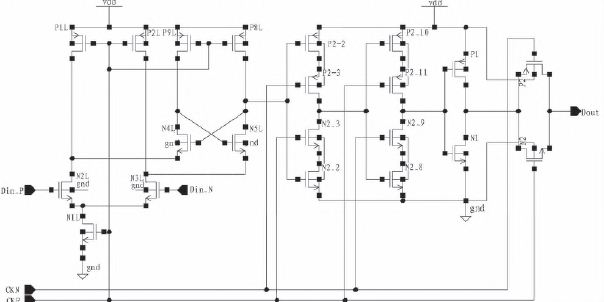

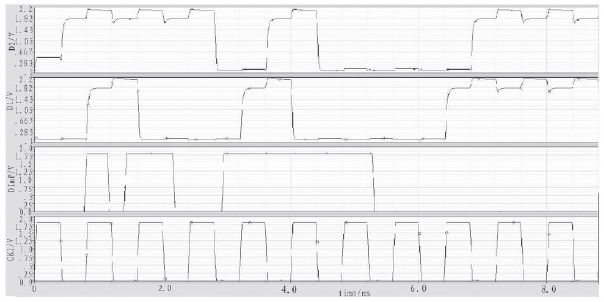

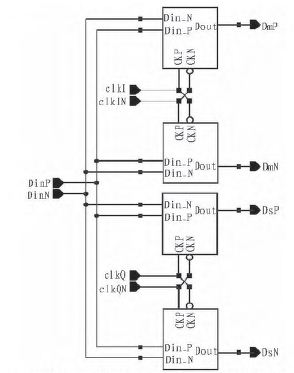

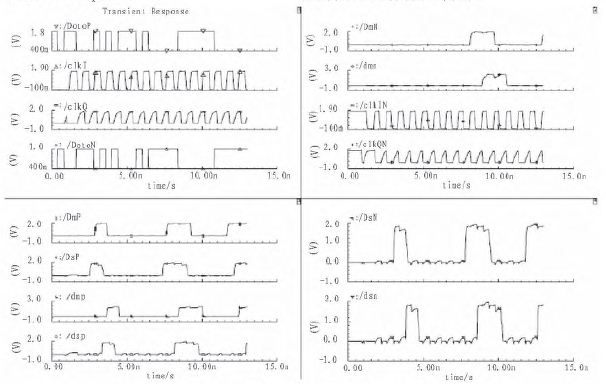

ИпЫйЭЈаХЯЕЭГвбОдкЪРНчЗЖ ЮЇФкНјШыДѓЙцФЃНЈЩшНзЖЮЃЌДѓСПЕФаХЯЂНЛЛЅДйНјСЫЭЈаХКЭМЦЫуЛњММЪѕЕФбИУЭЗЂеЙЃЌИпЫйИЩЯпЯЕЭГзїЮЊаХЯЂИпЫйЙЋТЗЕФжїИЩЃЌбаОПЩшМЦЦфЫљВЩгУЕФИпЫйаОЦЌЪЦдкБиааЁЃЪ§ОнЕФДЋЪфЗНЪНЃЌгЩгкВЂаааХКХБЫДЫжЎМфЕФёюКЯгыДЎШХЯожЦСЫЦфЙЄзїЫйЖШКЭДЋЪфОрРыЃЌЖјДЎааЗНЪННкдМДЋЪфУННщЃЌНЕЕЭСЫЯЕЭГЛЅСЌЕФИДдгадЃЌДЋЪфЫйТЪИќИпЁЂОрРыИќдЖЃЌвбдкаОЦЌжЎМфЁЂДІРэЦїгыЭтЩшжЎМфЁЂИпЫйгВХЬНгПкЁЂБГАхСЌНгЕШСьгђЙуЗКгІгУЁЃ ЮЊСЫПЫЗўЪБжгЕФзюДѓЗзЊЦЕТЪЪмЕНЙЄвеЯожЦЕФШБЕуЃЌМђЛЏЕчТЗЩшМЦЕФИДдгЖШвдМАЪБжгЗжВМЕФФбЖШЃЌЪЕЯжИќИпЕФЫйТЪЃЌЭЌЪБОЁСПНЕЕЭЯЕЭГЙІКФЃЌАыЫйТЪЕчТЗНсЙЙж№ВНШЁДњШЋЫйТЪНсЙЙЁБ_ЁЃБОЮФИљОн2.5GbpsИпЫйДЎааЪеЗЂЦїЕФЙЄзїЪЕМЪЃЌЮЊНЕЕЭКѓајЕчТЗЩшМЦФбЖШЃЌВЩгУЙЄзїЫйТЪНЯИпЕФЕчСїФЃЪНТпМ(Current Mode LogicЃЌCML)ЩшМЦСЫЫЋЛЗЪБжгЪ§ОнЛжИДЕчТЗжаЕФЧАЖЫ1ЃК2НтИДгУЕчТЗЃЌВЩгУSMIC 0.18 umФЃФтЛьКЯаХКХЙЄвеЪЕЯжВЂЛљгкSpectraVerilogНјааЪ§ФЃЛьКЯЗТецЃЌНсЙћЯдЪОЕчТЗПЩвде§ГЃЙЄзїЃЌЗћКЯдЄЦквЊЧѓЁЃ 1 НтИДгУЕчТЗЕЅдЊ НтИДгУЕчТЗАбвЛТЗИпЫйаХКХЛЙдЮЊШєИЩТЗЕЭЫйаХКХЃЌГЃгУНсЙЙАќРЈДЎааЁЂВЂааЁЂЪїаЮвдМАЩЯ Ъі3жжНсЙЙЕФзщКЯаЮЪНЁЃДЎааНтИДгУЕчТЗНсЙЙМђЕЅЃЌЪБађЙиЯЕЧхГўЃЌПЩвдЪЕЯжШЮвт1ЃКNЕФНтИДгУЙІФмЃЌЕЋЫљгаДЅЗЂЦїЙЄзїдкЪфШыЪБжгЦЕТЪЩЯЃЌЦфЙЄзїЫйЖШЛсжЦдМЕчТЗЕФЫйЖШЃЌвђДЫДЎааНсЙЙЖдДЅЗЂЦїЩшМЦКЭЙЄвеЕФвЊЧѓНЯИпЃЌЖјЬсИпДЅЗЂЦїЫйТЪЛсДјРДаОЦЌЙІКФдіМгЁЂЕчЦНАкЗљМѕаЁЃЌдыЩљШнЯоБфаЁЕШЮЪЬтЃЌвђДЫГЃгУгкЕЭЫйЯЕЭГжаЃЛВЂааНсЙЙжаДЅЗЂЦїЙЄзїдкЪфГіЪ§ОнЫйТЪЩЯЃЌЖдДЅЗЂЦїЫйТЪвЊЧѓаЁЃЌвђДЫЙІКФНЯЕЭЁЂЩшМЦМђЕЅЃЌМцЙЫСЫЫйЖШгыЙІКФЃЌЪЧ1ЃК2НтИДгУЕчТЗЕФРэЯыНсЙЙЃЌЕЋЖдгк1ЃКNНтИДгУЖјбдЃЌNИіВЂааСЌНгЕФДЅЗЂЦїЖдЧАМЖЕчТЗЙЙГЩКмДѓЕФЕчШнИКдиЃЌЪЧЫйТЪЬсЩ§БфЕУРЇФбЃЛЪїаЮНтИДгУЕчТЗГфЗжРћгУ1ЃК2ВЂааНтИДгУЕчТЗЕФгХЕуЃЌЪЙећИіЕчТЗНЯЧАСНжжНсЙЙгаИпЫйЕЭЙІКФЕФгХЕуЁЃ ЖдгкВЩгУАыЫйТЪНсЙЙЕФИпЫйДЎааЪеЗЂЦїЖјбдЃЌећИіЕчТЗадФмжївЊЪмЧАЖЫ1ЃК2НтИДгУЕчТЗЕФЯожЦЃЌЭЌЪБПМТЧЕНЮЊСЫдіЧПаХКХПЩППадЃЌД§ДІРэЕФЪфШЫЪ§ОнЮЊВюЗжЪ§ОнЃЌБОЮФЩшМЦЕФ1ЃК2НтИДгУЕчТЗВЩгУРрВЂааНсЙЙЃЌШчЭМ1ЫљЪОЃЌЩЯЯТСНИіЕчТЗЮЊВЩгУЕчСїФЃЪНТпМНсЙЙЕФНтИДгУЕчТЗЕЅдЊЃЌЪфШыЮЊВюЗжЪ§ОнКЭЛЅВЙЪБжгЁЃ  ЭМ1 ВюЗжЪфШыЛЅВЙЪБжгЕФ1ЃК2НтИДгУЕчТЗдРэЭМ ЕчСїФЃЪНТпМЕчТЗЯрБШДЋЭГЕФCMOSЕчТЗПЩвддкИќЕЭЕФаХКХАкЗљЧщПіЯТЙЄзїдкИќИпЕФЦЕТЪЁЃЛљгкCMLЕФНтИДгУЕчТЗЕЅдЊдРэЭМШчЭМ2ЫљЪОЃЌЦфЙЄзїдРэПЩвдУшЪіЮЊЃКNMOSЙмN1LПЩвдПДзіПЊЙиЪЙгУЃЌдкЪБжг CKPЮЊЕЭЕчЦНЦкМфНижЙЃЌгЩN2LЁЂN3LЁЂP1LКЭP2LЙЙГЩЕФЪфШыМЖДІгкБЃГжФЃЪНЃЌN4LКЭN5LЕФТЉМЋБЛГфЕчЕНИпЕчЦНЃЛдкЪБжгCKPЮЊИпЕчЦНЦкМфЕМЭЈЃЌЪфШыМЖДІгкЭИУїзДЬЌЃЌЕчТЗНг ЪеВюЗжЪфШыЪ§ОнDin_PКЭDin_NЁЃЕчТЗжагЩP4LКЭP6LЙЙГЩЕФе§ЗДРЁЕчТЗЖдЧАМЖЦ№ЕНЫјДцзїгУЃЌПЩвдМгЫйЪфГіЪ§ОнЕФЗзЊЃЌЬсИпзЊЛЛЫйТЪЃЛзѓЯТНЧЕФ8ИіОЇЬхЙмЙЙГЩЦНКтИКдиЕчТЗЃЌПЩвдБЃжЄN4LКЭN5LЪфГіЯпЩЯЕФИКдиЖдГЦЁЃЪфШыЪ§ОндкЪБжгаХКХПижЦЯТЫЭЕНЪфГіDoutЃЌЪфГіЪ§ОнгыЪфШыЪ§ОнЗДЯрЁЃ  ЭМ2 НтИДгУЕчТЗЕЅдЊдРэЭМ  ЭМ3 НтИДгУЕЅдЊЕчТЗЗТецНсЙћ ЖдЭМ1ЫљЪОЕФНтИДгУФЃПщНјааЗТецЃЌЪфШыЮЊгЩЛЅВЙЕФPWLЗжЖЮЯпаддДжИЖЈЕФЮЛжмЦкЮЊ400 psЕФВюЗжЪ§ОнЃЌВЩгУжмЦкT=800 psЃЌЩЯЩ§ЪБМфКЭЯТНЕЪБМфЮЊtr=tf=40 psЕФТіГхЕчбЙдДзїЮЊЪБжгаХКХЃЌЗТецНсЙћШчЭМ3ЫљЪОЁЃДгЭМжаПЩвдПДГігааЇЪ§ОнВПЗжДгЪБжгЕФЕкЖўИіИпТіГхПЊЪМЃЌДгЗТецНсЙћПЩжЊЃЌНтИДгУЕчТЗПЩвде§ГЃЪЕЯжЪ§Он1ЃК2ЕФДЎВЂзЊЛЛЁЃ 2 гУгкИпЫйЪеЗЂЦїЕФНтИДгУЕчТЗ дкИпЫйДЎааЪеЗЂЦїЕФНгЪеЖЫЃЌЮЊСЫБЃжЄЪ§ОнЕФТГАєадКЭЕчТЗЙЄзїЕФПЩППадЃЌЪ§ОнВЩгУВюЗжаЮ ЪНЁЃДгЕкЖўВПЗжПЩвдПДГіЛљгкCMLЕФ1ЃК2НтИДгУЕчТЗПЩвде§ГЃЙЄзїЃЌвђДЫПЩвдвдДЫЮЊЛљДЁДю НЈгУгкИпЫйВюЗжДЎааЪ§ОнАыЫйТЪЪеЗЂЦїЕФЧАЖЫ1ЃК2НтИДгУЕчТЗЁЃЕчТЗдРэЭМШчЭМ4ЫљЪОЁЃЦф жаclkIгыclkINЁЂclkQЁЂclkQNЮЊЛЅВЙЪБжгЃЌclkIгыclkIQЮЊе§НЛЪБжгЃЌDinPКЭDinNerЮЛВюЗж ЪфШыЕФ2.5GbpsДЎааЪ§ОнЃЌDmPгыDmNЁЂDsPгыDmNЮЊ1ЃК2НтИДгУКѓЕФСНТЗ1.25GbpsВщЗжЪ§ОнЁЃ  ЭМ4 ВюЗжЪфШыВюЗжЪфГіЕФ1ЃК2НтИДгУЕчТЗдРэЭМ  ЭМ5 ећЬхНтИДгУЕчТЗЕФЗТецВЈаЮЭМ ВЩгУSMIC 0.18umФЃФтЛьКЯаХКХЙЄвеЭъГЩЕчТЗЩшМЦЃЌЯжЖдЭМ4ЫљЪОНтИДгУЕЅдЊНјааЗТецЁЃгЩгк ЗжЖЮЯпадЕчбЙдДдкБэЪОЪ§ОнЪБЬиБ№ЗБЫіЃЌЖјЧвЕЅИіжИЖЈЪ§ОнФбвдБЃжЄЗТецЕФЫцЛњадКЭШЋУцад ЃЌЙЪЖјетРяВЩгУЪ§ФЃЛьКЯЕФЗНЗЈНјааЗТецЁЃЪфШыЪ§ОнВЩгУVerilogHDLгябдБраДЕФЮБЫцЛњађСа ЃЌВЩгУCadenceЕФSpectreVerilogНјааЗТецЁЃЗТецНсЙћШчЭМ5ЫљЪОЃЌБШНЯЪфШыЪ§ОнКЭгЩжїЪБжг ВЩбљЪфГіЕФЪ§ОнЃЌПЩвдПДГіЕчТЗЕФНтИДгУВйзїЪЧе§ШЗЕФЁЃ 3 НсТл БОЮФУшЪіСЫНтИДгУЕчТЗЕФ ДЋЭГЩшМЦЗНЗЈВЂЗжЮіСЫИїздЬиЕуЃЌИљОн2.5GbpsИпЫйДЎааЪеЗЂЦїЕФгІгУЪЕМЪЃЌВЩгУРрВЂааНсЙЙЁЂЛљгкЕчСїФЃЪНТпМЩшМЦСЫЪеЗЂЦїЕФЧАЖЫНтИДгУЕчТЗЃЌВЂЗжЮіСЫЦфЙЄзїдРэЃЌВЩгУSMIC O.18 umЛьКЯаХКХЙЄвеЭъГЩСЫЕчТЗЩшМЦЃЌВЂВЩгУSpectreVerilogНјааСЫЪ§ФЃЛьКЯЗТецЃЌНсЙћБэУїИУЕчТЗдк2.5GbpsЪеЗЂЦїЕчТЗжаПЩвдЮШЖЈПЩППЕиЙЄзїЁЃ |

ЭјгбЦРТл