IC测试基本原理与ATE测试向量生成

发布时间:2014-12-16 11:46

发布者:designapp

|

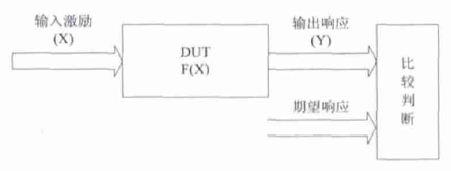

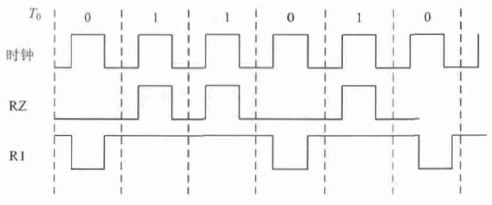

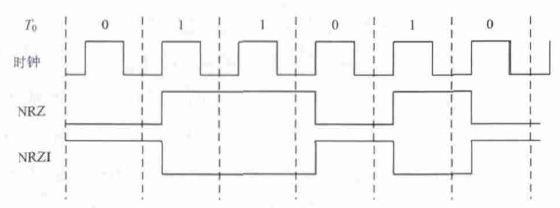

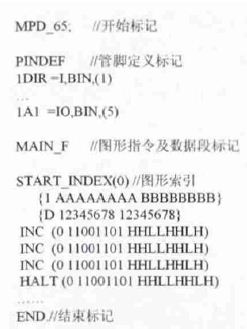

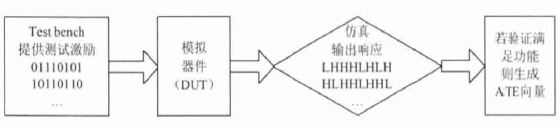

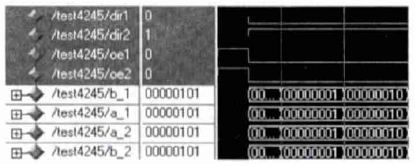

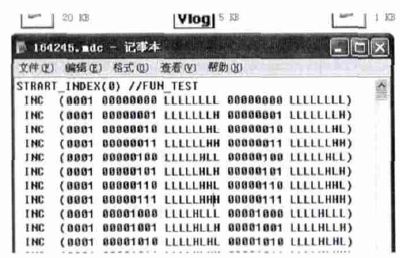

集成电路测试(IC测试)主要的目的是将合格的芯片与不合格的芯片区分开,保证产品的质量与可靠性。随着集成电路的飞速发展,其规模越来越大,对电路的质量与可靠性要求进一步提高,集成电路的测试方法也变得越来越困难。因此,研究和发展IC测试,有着重要的意义。而测试向量作为IC测试中的重要部分,研究其生成方法也日渐重要。 1 IC 测试 1.1 IC测试原理 IC 测试是指依据被测器件(DUT)特点和功能,给DUT提供测试激励(X),通过测量DUT输出响应(Y)与期望输出做比较,从而判断DUT是否符合格。图1所示为IC测试的基本原理模型。 根据器件类型,IC测试可以分为数字电路测试、模拟电路测试和混合电路测试。数字电路测试是IC测试的基础,除少数纯模拟IC如运算放大器、电压比较器、模拟开关等之外,现代电子系统中使用的 大部分IC都包含有数字信号。  图1 IC测试基本原理模型 数字IC 测试一般有直流测试、交流测试和功能测试。 1.2 功能测试 功能测试用于验证IC是否能完成设计所预期的工作或功能。功能测试是数字电路测试的根本,它模拟IC的实际工作状态,输入一系列有序或随机组合的测试图形,以电路规定的速率作用于被测器件,再在电路输出端检测输出信号是否与预期图形数据相符,以此判别电路功能是否正常。其关注的重点是图形产生的速率、边沿定时控制、输入/输出控制及屏蔽选择等。 功能测试分静态功能测试和动态功能测试。静态功能测试一般是按真值表的方法,发现固定型(Stuckat)故障。动态功能测试则以接近电路 工作频率的速度进行测试,其目的是在接近或高于器件实际工作频率的情况下,验证器件的功能和性能。 功能测试一般在ATE(Automatic Test Equipment)上进行,ATE测试可以根据器件在设计阶段的模拟仿真波形,提供具有复杂时序的测试激励,并对器件的输出进行实时的采样、比较和判断。 1.3 交流参数测试 交流(AC)参数测试是以时间为单位验证与时间相关的参数,实际上是对电路工作时的时间关系进行测量,测量诸如工作频率、输入信号输出信号随时间的变化关系等。常见的测量参数有上升和下降时间、传输延迟、建立和保持时间以及存储时间等。交流参数最关注的是最大测试速率和重复性能,然后为准确度。 1.4 直流参数测试 直流测试是基于欧姆定律的,用来确定器件参数的稳态测试方法。它是以电压或电流的形式验证电气参数。直流参数测试包括:接触测试、漏电流测试、转换电平测试、输出电平测试、电源消耗测试等。 直流测试常用的测试方法有加压测流(FVMI)和加流测压(FIMV),测试时主要考虑测试准确度和测试效率。通过直流测试可以判明电路的质量。如通过接触测试判别IC引脚的开路/短路情况、通过漏电测试可以从某方面反映电路的工艺质量、通过转换电平测试验证电路的驱动能力和抗噪声能力。 直流测试是IC测试的基础,是检测电路性能和可靠性的基本判别手段。 1.5 ATE测试平台 ATE(Automatic Test Equipment)是自动测试设备,它是一个集成电路测试系统,用来进行IC测试。一般包括计算机和软件系统、系统总线控制系统、图形存储器、图形控制器、定时发生器、精密测量单元(PMU)、可编程电源和测试台等。 系统控制总线提供测试系统与计算机接口卡的连接。图形控制器用来控制测试图形的顺序流向,是数字测试系统的CPU。它可以提供DUT所需电源、图形、周期和时序、驱动电平等信息。 2 测试向量及其生成 测试向量(Test Vector)的一个基本定义是:测试向量是每个时钟周期应用于器件管脚的用于测试或者操作的逻辑1和逻辑0数据。这一定义听起来似乎很简单,但在真实应用中则复杂得多。因为逻辑1和逻辑0是由带定时特性和电平特性的波形代表的,与波形形状、脉冲宽度、脉冲边缘或斜率以及上升沿 和下降沿的位置都有关系。 2.1 ATE测试向量 在ATE语言中,其测试向量包含了输入激励和预期存储响应,通过把两者结合形成ATE 的测试图形。这些图形在ATE中是通过系统时钟上升和下降沿、器件管脚对建立时间和保持时间的要求和一定的格式化方式来表示的。格式化方式一般有RZ(归零)、RO(归1)、NRZ(非归零)和NRZI(非归零反)等。 图2为RZ和R1格式化波形,图3为NRZ和NRZI格式化波形。  图2 RZ和R1数据格式波形  图3 NRZ和NRZI数据格式波形 RZ数据格式,在系统时钟的起始时间T0,RZ测试波形保持为“0”,如果在该时钟周期图形存储器输出图形数据为“1”,则在该周期的时钟周期期间,RZ测试波形由“0”变换到“1”,时钟结束时,RZ 测试波形回到“0”。若该时钟周期图形存储器输出图形数据为“0”,则RZ测试波形一直保持为“0”,在时钟信号周期内不再发生变化。归“1”格式(R1)与RZ相反。 非归“0”(NRZ)数据格式,在系统时钟起始时间T0,NRZ测试波形保持T0前的波形,根据本时钟周期图形文件存储的图形数据在时钟的信号沿变化。即若图形文件存储数据为“1”,那么在相应时钟边沿,波形则变化为“1”。NRZI波形是NRZ波形的反相。 在ATE中,通过测试程序对时钟周期、时钟前沿、时钟后沿和采样时间的定义,结合图形文件中存储的数据,形成实际测试时所需的测试向量。 ATE测试向量与EDA设计仿真向量不同,而且不同的ATE,其向量格式也不尽相同。以JC-3165型ATE为例,其向量格式如图4所示。 ATE向量信息以一定格式的文件保存,JC-3165向量文件为*.MDC文件。在ATE测试中,需将*.MDC文件通过图形文件编译器,编译成测试程序可识别的*.MPD文件。在测试程序中,通过装载图形命令装载到程序中。  图4 ATE测试向量格式 2.2 ATE测试向量的生成 对简单的集成电路,如门电路,其ATE测试向量一般可以按照ATE向量格式手工完成。而对于一些集成度高,功能复杂的IC,其向量数据庞大,一般不可能依据其逻辑关系直接写出所需测试向量,因此,有必要探寻一种方便可行的方法,完成ATE向量的生成。 在IC设计制造产业中,设计、验证和仿真是不可分离的。其ATE 测试向量生成的一种方法是,从基于EDA工具的仿真向量(包含输入信号和期望的输出),经过优化和转换,形成ATE格式的测试向量。 依此,可以建立一种向量生成方法。利用EDA工具建立器件模型,通过建立一个Test bench仿真验证平台,对其提供测试激励,进行仿真,验证仿真结果,将输入激励和输出响应存储,按照ATE向量格式,生成ATE向量文件。其原理如图5所示。  图5 ATE向量生成示意图 2.3 测试平台的建立 (1)DUT模型的建立 ① 164245模型:在Modelsim工具下用Verilog HDL语言[5],建立164245模型。164245是一个双8位双向电平转换器,有4个输入控制端:1DIR,1OE,2DIR,2OE;4组8位双向端口:1A,1B,2A,2B。端口列表如下: input DIR_1,DIR_2,OE_1,OE_2; inout [0:7] a_1,a_2,b_1,b_2; reg [0:7] bfa1,bfb1,bfa2,bfb2;//缓冲区 ② 缓冲器模型:建立一个8位缓冲器模型,用来做Test bench 与164245 之间的数据缓冲,通过 在Testbench总调用缓冲器模块,解决Test bench与164245模型之间的数据输入问题。 (2)Test bench的建立 依据器件功能,建立Test bench平台,用来输入仿真向量。 Test bench中变量定义: reg dir1,dir2,oe1,oe2; //输入控制端 reg[0:7] a1,a2,b1,b2; //数据端 reg[0:7] A1_out[0:7]; //存储器,用来存储数据 reg[0:7] A2_out[0:7]; reg[0:7] B1_out[0:7]; reg[0:7] B2_out[0:7]; 通过Test bench 提供测试激励,经过缓冲区接口送入DUT,观察DUT输出响应,如果满足器件功能要求,则存储数据,经过处理按照ATE 图形文件格式产生*.MDC 文件;若输出响应有误,则返回Test bench 和DUT模型进行修正。其原理框图可表示如图6所示。  图6 Test bench验证平台框图 (3)仿真和验证 通过Test bench 给予相应的测试激励进行仿真,得到预期的结果,实现了器件功能仿真,并获得了测试图形。图7和图8为部分仿真结果。  图7 仿真数据结果 在JC-3165的*.MDC图形文件中,对输入引脚,用“1”和“0”表示高低电平;对输出引脚,用“H”和“L”表示高低电平;“X”则表示不关心状态。由于在仿真时,输出也是“0”和“1”,因此在验证结果正确后,对输出结果进行了处理,分别将“0”和“1”转换为“L”和“H”,然后放到存储其中,最后生成*.MDC图形文件。  图8 生成的*.MDC文件 3 结论 本文在Modelsim环境下,通过Verilog HDL语言建立一个器件模型,搭建一个验证仿真平台,对164245进行了仿真,验证了164245的功能,同时得到了ATE所需的图形文件,实现了预期所要完成的任务。 随着集成电路的发展,芯片设计水平的不断提高,功能越来越复杂,测试图形文件也将相当复杂且巨大,编写出全面、有效,且基本覆盖芯片大多数功能的测试图形文件逐渐成为一种挑战,在ATE上实现测试图形自动生成已不可能。因此,有必要寻找一种 能在EDA工具和ATE测试平台之间的一种灵活通讯的方法。 目前常用的一种方法是,通过提取EDA工具产生的VCD仿真文件中的信息,转换为ATE测试平台所需的测试图形文件,这需要对VCD文件有一定的了解,也是进一步的工作。 |

网友评论