ЛљгкаОЦЌВтЪдЕФЛЗТЗТЫВЈЦїЩшМЦ

ЗЂВМЪБМфЃК2014-12-16 11:46

ЗЂВМепЃКdesignapp

|

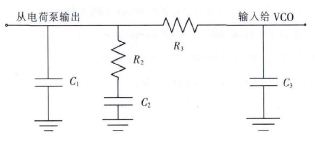

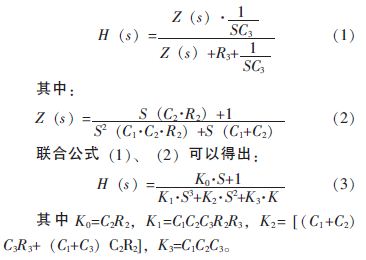

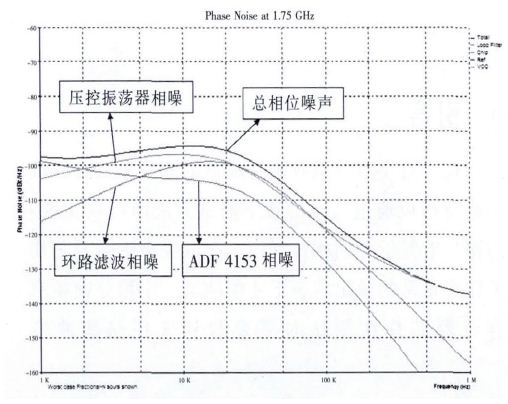

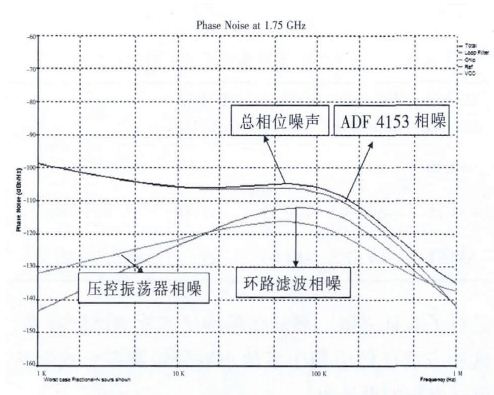

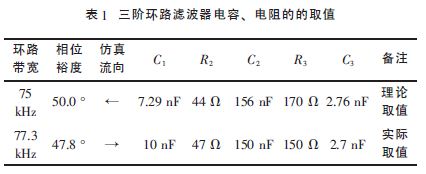

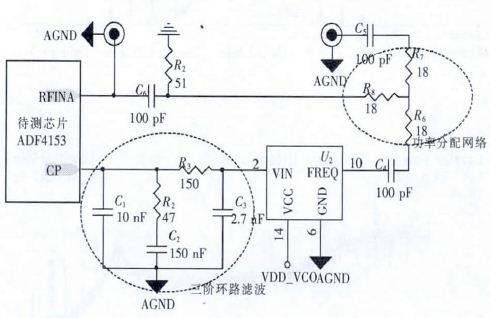

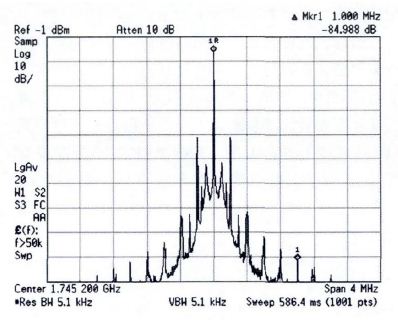

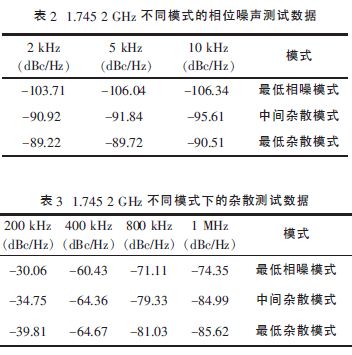

аЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїдкВтЪдЪББиаыЭтНгвЛИіЛЗТЗТЫВЈЦїЕчТЗгыбЙПиеёЕДЦїВХФмЙЙГЩвЛИіЭъећЕФЫјЯрЛЗЕчТЗЁЃЦфЭтЮЇЕчТЗжаЛЗТЗТЫВЈЦїЕФЩшМЦКУЛЕНЋжБНггАЯьЕНаОЦЌЕФадФмВтЪдЁЃвдADF4153аЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїЮЊР§ЃЌбаОПСЫЦфЭтЮЇЛЗТЗТЫВЈЦїЕФЩшМЦЗНЗЈЃЌИјГіСЫЛљгкаОЦЌВтЪдЕФЛЗТЗТЫВЈЦїЩшМЦСїГЬЃЌВЂНјааСЫбщжЄВтЪдЁЃВтЪдНсЙћБэУїЃЌИУТЫВЈЦїПЩТњзуаЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїаОЦЌВтЪдЕФашвЊЁЃ дкНјаааЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїЕФаОЦЌВтЪдЪБЃЌЪ§зжВПЗжПЩвдЭЈЙ§ГЃЙцЕФЪ§зжВтЪдЗНЗЈМДПЩвдЪЕЯжЃЛЖјЪфГіЩфЦЕаХКХЕФЯрЮЛдыЩљЁЂдгЩЂдыЩљдђашвЊаОЦЌЙЄзїдке§ГЃЕФЪфГізДЬЌЯТВХФмВтЪдЁЃаЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїаОЦЌдкВтЪдЪБашвЊгыЭтНгЛЗТЗТЫВЈЦїЃЈLFЃЉЁЂбЙПиеёЕДЦїЃЈVCOЃЉВХФмЙЙГЩЭъећЕФЫјЯрЛЗЛиТЗЃЌдкОпБИе§ГЃЕФаОЦЌЙІФмЕФЧАЬсЯТВХФмЪЕЯжЖдЦфЯрЮЛдыЩљЁЂдгЩЂдыЩљЯТЕФВтЪдЁЃ вЛАуЖјбдЃЌбЙПиеёЕДЦїОљЪЙгУЯжГЩЕФЦїМўЃЌдкЬєбЁЦїМўЪБзЂвтадФмжИБъЕФЦЅХфОЭПЩвдЃЌжЛгаЛЗТЗТЫВЈЦїВХЪЧашвЊМЦЫуКЭЩшМЦЕФЁЃЛЗТЗТЫВЈЦїдкећИіЕчТЗжажївЊзїЮЊвЛИіЕЭЭЈТЫВЈЦїЃЌЫќНЋаОЦЌМјЯрЦїЪфГіЕФТіГхаХКХНјааЕЭЭЈТЫВЈЃЌНЋИпЦЕЗжСПТЫГ§ЃЌзюжеЕУЕНвЛИіЯрЖдЦНЛЌЕФжБСїЕчбЙаХКХШЅПижЦVCOЙЄзїЃЌДгЖјЛёЕУвЛИіЮШЖЈЕФЦЕТЪЪфГіЁЃЛЗТЗТЫВЈЦїЕФадФмНЋжБНггАЯьЕНаЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїаОЦЌадФмЕФВтЪдЁЃ БОЮФвдADF 4153аЭаЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїЮЊР§ЃЌИјГіСЫШнвзЪЕЯжЕФШ§НзЛЗТЗТЫВЈЦїЕФЩшМЦЗНЗЈЃЌФмЙЛТњзуаОЦЌЪЕМЪВтЪдЕФашвЊЁЃ 1 ЭтНгЛЗТЗТЫВЈЦїЕФЩшМЦ ЛЗТЗТЫВЈЦїЪЧЕчКЩБУЫјЯрЛЗЕчТЗЕФживЊЛЗНкЃЌЫќСЌНгдкЕчКЩБУКЭбЙПиеёЕДЦїжЎМфЁЃЫјЯрЛЗЕФЛљБОЦЕТЪЬиадЪЧгЩЛЗТЗТЫВЈЦїОіЖЈЕФЁЃЪЕМЪЩЯЃЌе§ЪЧгЩгкЛЗТЗТЫВЈЦїЕФДцдкЃЌЫјЯрЛЗВХПЩвдбЁдёЙЄзїдкШЮвтЕФжааФЦЕТЪКЭДјПэФкЁЃЛЗТЗТЫВЈЦїЕФРраЭЖржжЖрбљЃЌДѓжТЗжЮЊгадДТЫВЈЦїКЭЮодДТЫВЈЦїСНДѓРрЃЌЮодДТЫВЈЦїгыгадДТЫВЈЦїЯрБШЃЌЦфгХЕудкгкЃКНсЙЙМђЕЅЁЂЕЭдыЩљЁЂИпЮШЖЈЖШКЭвзвдЪЕЯжЁЃ зюГЃМћЕФЮодДТЫВЈЦїЪЧШчЭМ1ЫљЪОЕФШ§НзТЫВЈЦїЁЃвЛАуЖјбдЃЌЛЗТЗТЫВЈЦїЕФДјПэгІЮЊPFDЦЕТЪЃЈЭЈЕРМфИєЃЉЕФ1/10ЁЃЬсИпЛЗТЗДјПэЛсЫѕЖЬЫјЖЈЪБМфЁЃЕЋЛЗТЗДјПэЙ§ДѓЛсДѓЗљЖШЕидіМгВЛЮШЖЈадЃЌДгЖјЕМжТЫјЯрЛЗЮоЗЈЫјЖЈЕФзДЬЌЁЃ  ЭМ1Ш§НзЛЗТЗТЫВЈЦї Ш§НзЮодДТЫВЈЦїЕФДЋЕнКЏЪ§ЮЊЃК  ЮЊСЫЧѓШЁC1ЁЂC12ЁЂC3КЭR1ЁЂR2ЕФШЁжЕЃЌЪзЯШашвЊШЗЖЈЩшМЦашвЊЕФДјПэМАЯрЮЛдЃЖШЃЌжюЖрЮФЯзИјГіСЫЯъЯИЕФЧѓШЁВНжшЃЌдкДЫВЛдйЗѓЪіЁЃШЛЖјЃЌдкЪЕМЪЕФгІгУЪБЃЌетжжМЦЫуЗНЗЈНЯЮЊЗБЫіЃЌВЛРћгкЙЄГЬЩшМЦЪЙгУЁЃ ADIЙЋЫОЗЂВМЕФADIsimPLLЦЕТЪКЯГЩЦїЩшМЦШэМўПЩвдКмЗНБуЕиИљОнгУЛЇЕФЪЙгУвЊЧѓНјааЛЗТЗТЫВЈЦїЕФЩшМЦЁЃЫќНЋгІгУЙЄГЬЪІДгЗБдгЕФЪ§бЇМЦЫужаНтЭбГіРДЁЃгІгУепжЛвЊЪфШыЩшжУЛЗТЗТЫВЈЦїЕФМИИіЙиМќВЮЪ§ЃЌADISimPLLОЭПЩвдздЖЏЕиМЦЫуГіЫљашвЊЕФТЫВЈЦїдЊЦїМўЕФЪ§жЕЁЃетаЉВЮЪ§АќРЈЃКМјЯрЦЕТЪPFDЃЌЕчКЩБУЕчСїICPЃЌЛЗТЗДјПэBWЃЌЯрЮЛдЃЖШЃЌVCOПижЦСщУєЖШKvЃЌТЫВЈЦїЕФаЮЪНЃЈгадДЛђЮодДЃЌНзЪ§ЃЉЁЃШЛЖјЃЌдкаОЦЌВтЪдЪБЃЌШчКЮОЁПЩФмЕиНЋЭтНчЕчТЗЃЈШчЛЗТЗТЫВЈЦїЃЉв§ШыЕФдыЩљНЕЕЭЃЌвдВтЪдГіаОЦЌЕФецЪЕадФмЃЌетЪЧаОЦЌЭтЮЇЕчТЗЩшМЦЪБашвЊНтОіЕФЮЪЬтЁЃ 2 ЛЗТЗТЫВЈЦїЩшМЦВЮЪ§ЕФбЁдё ЮЊСЫбаОПЛЗТЗТЫВЈЦїЖдЫјЯрЛЗЪфГіЦЕТЪЯрЮЛдыЩљЕФгАЯьЃЌЩшМЦГіЗћКЯаОЦЌВтЪдашвЊЕФЭтЮЇЛЗТЗТЫВЈЦїЁЃЮвУЧдкADIsimPLLШэМўжаНјааСЫШчЯТЗТецХфжУЁЃЦїМўаЭКХЃКADF 4153ЃЌfPFD=25MHzЃЈРэЯыаХКХдДЃЉЃЌINT=69ЃЌFRAC=101ЃЌMOD=125ЃЌVCOВЩгУZCommЙЋЫОЕФV674ME34-LFЃЌдкИУХфжУЯТЃЌдЄЦкЪфГіЕФRFOUT=1.7452GHzЁЃ aЃЉЩшЖЈЛЗТЗТЫВЈЦїДјПэЮЊ20kHzЃЌЯрЮЛдЃЖШ50ЁуЃЌЦфЯрЮЛдыЩљЕФЗТецЧщПіШчЭМ2ЫљЪОЁЃ  ЭМ2ЛЗТЗДјПэ20kHzЪБЕФЯрЮЛдыЩљЗТецЭМ ДгЭМ2жаПЩвдЕУжЊЃЌЕБЛЗТЗТЫВЈДјПэЮЊ20kHzЪБЃЌVCOЫљв§Ц№ЕФЯрЮЛдыЩљеМОнСЫжїЕМЕиЮЛЁЃаОЦЌЫљв§Ц№ЕФЯрЮЛдыЩљдђБЛбЭУЛдкзмЪфГідыЩљжЎЯТЁЃЛЛОфЛАЫЕЃЌЕБЛЗТЗДјПэНЯеЃЈШч20kHЃЉЕФЧщПіЯТЃЌеыЖдЫјЯрЛЗЪфГіаХКХНјааЯрЮЛдыЩљВтЪдЃЌЦфНсЙћВЂВЛФмеце§ЕиЗДгГаОЦЌЪфГіЕФЯрЮЛдыЩљЁЃ bЃЉЩшЖЈЛЗТЗТЫВЈЦїДјПэЮЊ100kHzЃЌЯрЮЛдЃЖШ50ЁуЃЌЦфЯрЮЛдыЩљЕФЗТецЧщПіШчЭМ3ЫљЪОЁЃ  ЭМ3ЛЗТЗДјПэЮЊ100kHzЪБЕФЯрЮЛдыЩљЗТецЭМ ДгЭМ3жаПЩвдЕУжЊЃЌЕБЛЗТЗТЫВЈДјПэЮЊ100kHzЪБЃЌVCOЖдгкзмЯрЮЛдыЩљЕФЙБЯзЯджјЕиНЕЕЭЃЌаОЦЌЫљв§Ц№ЕФЯрЮЛдыЩљеМОнСЫжїЕМЕиЮЛЃЌдк10kHzвдФкЃЌзмЯрЮЛдыЩљЪфГіЕФЧњЯпЛљБОгыаОЦЌЫљв§Ц№ЕФЯрЮЛдыЩљжиКЯЁЃгЩДЫПЩвдЕУжЊЃЌЕБЛЗТЗДјПэНЯПэЃЈШч100kHzЃЉЕФЧщПіЯТЃЌеыЖдЫјЯрЛЗЪфГіаХКХНјааЯрЮЛдыЩљВтЪдЃЌЦфНсЙћЛљБОФмеце§ЗДгГаОЦЌЪфГіЕФЯрЮЛдыЩљЁЃ БОЮФбаОПЕФADF 4154ЕФжївЊВтЪдЦЕЕуЮЊ1.7452GHzЃЈfPFD=25MHzЃЌRSET=5.1kЃЉЃЌИљОнВтЪдвЊЧѓНјаазлКЯЕФПМТЧЃЌЩшЖЈСЫЛЗТЗДјПэ75kHzЃЌЯрЮЛдЃЖШ50ЁуЕФдМЪјЬѕМўЁЃдкНјааADF 4153ЕФЭтЮЇЕчТЗЩшМЦЪБЃЌЪзЯШашвЊШЗШЯЫљЪЙгУЕФVCOаЭКХМАЦфБъГЦадФмЁЃШЛКѓдйИљОнADIЙЋЫОЬсЙЉЕФADIsim-PLLШэМўНјааШ§НзЛЗТЗТЫВЈЦїЕФЩшМЦЁЃДгШэМўЕУГіC1~C3ЁЂR2ЁЂR3ЕФОпЬхШЁжЕЃЌдйИљОнЯжгаЕФБъГЦЕчШнЕчзшжЕНјааЕїећЃЌЗДЫуГіЪЕМЪЩшМЦЕФЛЗТЗДјПэМАЯрЮЛдЃЖШЁЃЪЕМЪЪ§ОнШчБэ1ЫљЪОЁЃ  гЩДЫЃЌЮвУЧШЗЖЈСЫЛЗТЗТЫВЈЦїжаИїИіЕчШнЁЂЕчзшЕФШЁжЕЃЌВЂЩшМЦСЫПЩгУгкADF 4153аОЦЌВтЪдЕФЕчТЗдРэЭМЃЌШчЭМ4ЫљЪОЁЃVCOЕФЪфГіВЛНіашвЊСЌНгЭтВПЦЕЦзвЧНјааВтЪдЃЌЛЙашвЊЭЈЙ§ЕчШнЗДРЁЕНADF 4153ЕФREFINAЖЫЃЌЭЌЪБREFINAЖЫЛЙашвЊдЄСєSMAЭЗгУгкЩфЦЕЪфШыЦЕТЪЗЖЮЇМАСщУєЖШВтЪдЁЃвЛИіМђЕЅЕФЕчзшЭјТчгУгкЭъГЩVCOЪфГіаХКХЙІТЪЕФдйЗжХфЁЃ  ЭМ4ЛЗТЗТЫВЈЦїМАЩфЦЕЕчТЗЩшМЦ 3 ЛЗТЗТЫВЈЦїЕФВтЪдбщжЄ дкЗТецЕФЛљДЁЩЯЃЌЮвУЧЩшМЦВЂМгЙЄСЫADF4153ЕФВтЪдАхЃЌВЂАДееМЦЫуЕФЕчШнЁЂЕчзшжЕзщГЩСЫЛЗТЗТЫВЈЭјТчЁЃВЩгУAgilent8257DЩфЦЕаХКХдДЬсЙЉ250MHzзїЮЊfREFINЃЌЭЈЙ§SPIЖЫПкЩшЖЈfPFD=25MHzЃЌN=69ЃЌ4/5ЗжЦЕФЃЪНЃЌICP=5mAЃЌFRAC=101ЃЌMOD=125ЁЃЪЙгУЦЕЦзвЧВтСПЪфГіаХКХЃЌФмЙЛе§ГЃЫјЖЈдк1.7452GHzЃЌШчЭМ5ЫљЪОЁЃЭМ6ЮЊИУЦЕЕуЕФЯрЮЛдыЩљВтЪдЭМЃЌЪЕВтЯрЮЛдыЩљЮЊ-106.34dBc/HzЁЃЛЗТЗДјПэдМЮЊ85kHzЃЌгыРэТлжЕ77.3kHzДцдквЛЖЈЕФВюОрЁЃетЪЧгЩгкдкЗТецЪБВЂУЛгаПМТЧВтЪдАхзпЯпМАВтЪдВхзљЕШДцдкЕФМФЩњЕчШнЫљЕМжТЕФЦЋВюЃЌЕЋШддкКЯРэЗЖЮЇвдФкЁЃ  ЭМ5ЪфГіаХКХЦЕЦз  ЭМ6ЯрЮЛдыЩљВтЪдЭМ еыЖдаОЦЌНјааВЛЭЌЙЄзїФЃЪНЯТЕФЯрЮЛдыЩљМАдгЩЂНјааВтЪдЃЌВтЪдНсЙћШчБэ2ЁЂ3ЫљЪОЁЃ Ъ§ОнЪжВсЙцЖЈзюЕЭЕФЯрЮЛдыЩљФЃЪНЯТ5kHzЦЕЦЋЕФЯрЮЛдыЩљPNЁм-95dBc/HzЃЌЪЕВтИУЕуЮЊ-106.04dBc/HzЃЌВтЪдНсЙћТњзувЊЧѓЁЃ Ъ§ОнЪжВсЙцЖЈжаМфдгЩЂФЃЪНЯТ1MHzЦЕЦЋЕФдгЩЂSNЁм-65dBc/HzЃЌЪЕВтИУЕуЮЊ-84.99dBc/HzЃЌВтЪдНсЙћТњзувЊЧѓЁЃ злЩЯЫљЪіЃЌИУТЫВЈЦїЕФЩшМЦФмДяЕНдЄЦкЕФЩшМЦФПБъЃЌТњзуВЛЭЌФЃЪНЯТЕФдгЩЂМАЯрдыВтЪдЕФвЊЧѓЃЌПЩгУгкADF 4153аОЦЌЕФадФмВтЪдЁЃ 4 НсЪјгя БОЮФжївЊЛљгкаОЦЌВтЪдФПЕФЃЌеыЖдЭтЮЇЕчТЗжаЕФЛЗТЗТЫВЈЦїЩшМЦРДНјааЬжТлЃЌЮФжаИјГіСЫвЛжжМђЕЅЁЂвзааЕФЙЄГЬЛЏМЦЫуЗНЗЈКЭСїГЬЃЌВЂЖдЦфНјааСЫбщжЄВтЪдЃЌВтЪдНсЙћТњзуаОЦЌВтЪдЕФашвЊЁЃетжжЗНЗЈвбОгІгУгкЖрПюаЁЪ§ЗжЦЕЦЕТЪКЯГЩЦїЕФВтЪдЕчТЗЕФЩшМЦжаЁЃ  |

ЭјгбЦРТл