关于DDR3的对比研究

发布时间:2014-12-16 11:30

发布者:designapp

|

为实现集成式用户体验,如今的设备支持的功能越来越多,使各类接口承担了大量数据流量压力。为了更高效地处理这些数据,提供高带宽的快速内存可解当前的燃眉之急。尽管内存的种类多种多样,但在通过高带宽数据传输接口提供大量动态随机存取存储时,双倍数据速率(DDR)内存仍占据着主导地位。这些类型的内存之所以被称为双倍数据速率是因为相比单数据速率内存,它们可以在一个内存时钟周期内进行两次数据传输,进而提供双倍的性能。 一般来说,DDR内存有多个存储体,内含交错的存储阵列以及预取缓冲区。对于所有数据传输而言,内存地址可划分为存储体地址、行地址和列地址。DDR内存的性能优势主要体现在其预取架构和突发式操作上。当内存访问存储体的一个特定行时,预取缓冲区就会获得一组相邻的数据字,并随后在内存时钟各个沿的I/O管脚上突发,无需单独的列地址。因此,预取缓冲区越大,带宽就越高。此外,通过创建含有多个DDR内存芯片的模块也可以实现高带宽。 〈对于所有数据传输而言,内存地址可划分为存储体地址、行地址和列地址。DDR内存的性能优势主要体现在其预取架构和突发式操作上。〉 在正常操作前,DDR内存必须要以预先定义的方式进行上电和初始化。在进行读/写操作前,需要激活/打开存储体的一个特定行(基本上是激活并增强该行的信号),待操作完成后,若不再需要访问该行,则可对其进行预充电操作或将其关闭。DDR内存需要定期刷新,这样其内容才不会丢失。 DDR内存的预取缓冲区大小为2n(即每个内存访问周期2个数据字),DDR2内存的预取缓冲区大小为4n(即每个内存访问周期4个数据字),DDR3内存的预取缓冲区大小为8n(即每个内存访问周期8个数据字)。其中,n指I/O接口的大小,通常为4、8或16。这些预取计划的有效性主要得益于空间区域性原则。 了解了这些基本知识后,接下来我们将进一步探讨DDR3内存的具体特性和功能。 DDR3内存 与DDR2内存相比,DDR3内存的性能大大提高,主要体现在功耗进一步降低,能够在更高的时钟频率下运行,且采用了8n预取结构,为数据传输提供了更高带宽。通常,DDR3内存的工作电压为1.5V,内存时钟频率为400MHz~800MHz,从而使每管脚的数据传输速率达到800Mbps~1600Mbps。DDR3内存可在4位、8位、16位I/O接口上运行,支持的突发长度为每内存访问周期4或8个数据字。DDR3内存与DDR2内存的重要特性对比见表1。  表1:DDR3与DDR2内存的特性对比。 除了上述的特性改进之外,DDR3内存中还新增了DDR2内存所不具备的特性: ● 引入了FLY_BY拓扑结构,将命令和地址信号发送到内存模块,从而以更高的速度提供更好的信号完整性。 ● 支持写入均衡(Write leveling)和读取均衡(Read leveling)机制,以补偿由FLY_BY拓扑结构造成的倾斜。 ● 采用专用ZQ管脚和ZQ校准序列并配合片上校准引擎来校验片内终结器(ODT)电路和输出驱动器。 ● 引入了专门的复位管脚。 ● 支持低功耗强化特性。 ● 支持动态ODT特性,以提高写入操作的信号完整性。 以下章节中将详细描述DDR3的上述新特性。 【分页导航】

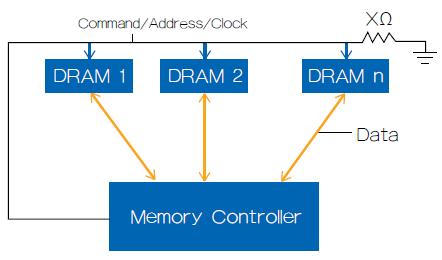

FLY_BY拓扑结构 DDR3内存具有较高的信号传输速率,因此需要有一个新的拓扑结构将命令和控制信号发送到不同的内存模块中。DDR2使用的是如图1所示的T型拓扑结构,但是这种拓扑结构由于容性负载限制,无法支持较高的信号传输速率以及数量较多的内存模块。在T型拓扑结构中,信号在被发送到各个内存模块前会先到达一个中心节点,从而限制了走线长度变动的可能性,使走线长度局限到较短的路径。该拓扑结构无法可靠地支持较高的信号传输速率,是因为在增加内存容量时,会出现多个stub且信号可检测到的容性负载也会增加。  图1:将内存控制器与DDR2内存模块连接在一起的T型拓扑结构图,其中的命令/地址/时钟信号以分支结构发送到各个内存模块中。 为解决上述问题,DDR3内存采用了FLY_BY拓扑结构,将命令和地址信号串联到各个内存模块上,并在末端配备合适的电阻。在该拓扑结构中,信号可在不同的间隔时间内到达不同的内存模块,可延迟遭遇内存模块输入容性负载的时间。这样一来,通过容性负载的减少,DDR3可以在不影响数据速率的同时提供更高的信号传输速率并提升内存系统的扩展性。图2给出了DDR3内存系统采用的FLY_BY拓扑结构。  图2:将内存控制器和DDR3内存模块连接在一起的FLY_BY拓扑结构图,其中各个内存模块共享以串联模式连接在一起的通用命令/地址/时钟信号线。 【分页导航】

写入均衡 由于DDR3内存采用了FLY_BY拓扑结构,命令、地址和时钟信号与数据和选通信号会在不同时间到达不同的内存模块。为了解决这个问题,DDR3内存引入了整平技术,使各个内存模块接口的数据选通与时钟信号对齐。系统中各个内存模块的每一个数据字节都要进行整平操作。 写入均衡弥补了数据写入操作中内存模块界限处数据选通信号和时钟信号间的偏斜。在启动写入均衡机制前,需要向DDR3内存写入适当的模式寄存器值使其进入写入均衡模式。进入写入均衡模式后,内存模块便有了时钟信号和数据选通信号。内存模块在其边界采样时钟信号,与观测到的数据选通信号进行对比,然后通过数据线将采样值(0/1)反馈给驱动实体,以便为下一个循环中的数据选通信号做延迟调整。这一流程反复进行,直到观测的反馈值从0跳变为1,这表明内存模块边界的时钟信号与数据选通信号对齐。 读取均衡 读取均衡主要解决数据读取操作中数据与选通信号之间的偏斜。为了支持此特性,DDR3内存中增加了一个多用途寄存器(MPR)。该寄存器中包含一个预先定义的数据模式,选中后就会在数据线上输出该模式的数据而非内存阵列中的普通数据。在启动读取均衡序列前,需要向DDR3内存中编入适当的模式寄存器值,使MPR数据成为输出数据。之后,读取均衡机制启动,开始向内存模块发送READ命令,并试图通过优化调整数据选通信号的内部延迟来捕获预定义数据。反复重复此流程直到通过调整数据选通信号内部延迟而创建的窗口能够以最佳方式捕获到预先定义模式的数据。读写均衡特性仅涉及DDR3内存,DDR2内存不支持此类特性。 【分页导航】

ZQ校准 为了提高信号完整性,并增强输出信号强度,DDR内存中引入了终端电阻和输出驱动器。而为了在温度和电压发生变化的情况下仍能保持信号完整性,就需要对这些终端电阻和输出驱动器进行定期校准。未经校准的终端电阻会直接影响信号质量,而调整不当的输出驱动器则会使有效信号跃迁偏离参考电平,从而导致数据和选通信号之间出现偏差。如图3所示,这种偏差会缩短有效数据窗口,并降低数据传输的可靠性。  图3:因不等的数据选取脉冲(DQS)驱动使交叉点偏离中间水平而导致有效数据窗口缩短。 DDR2内存的输出驱动器一般置于芯片外,只在初始化过程中随机校准一次,因此这种被称为“片外驱动校准(OCD)”的校准序列仅用于校准片外输出驱动器。DDR2内存无法支持ODT校准模式。 为了保持更高的信号完整性,DDR3内存中引入ODT和片上输出驱动器。DDR3内存中新增了ZQ专用脚,在ZQ管脚与地面之间接有一个240Ω±1%容差的外部参考电阻,便于进行校准。当内存模块收到ZQ校准命令时,片上校准引擎便启动校准序列。在DDR3内存的初始化阶段会进行初始ZQ校准,之后会定期进行短时ZQ校准,以补偿运行温度和电压漂移造成的信号波动。 动态ODT 为了提高数据总线上的信号完整性,DDR3内存中新增了一个特性,可以在不设置模式寄存器值的情况下修改ODT电阻。使能该特性后,一个不同的终端电阻值就会被写入到内存中。图4展示了在DDR3内存中使能该特性后,如何在写入操作中动态转换终端电阻,在这种情况下也无需再发送模式寄存器编程命令。  图4:使能DDR3内存模块的动态ODT阻配置特性后,在数据写入操作中该配置将终端电阻改为“RTT_Dyn”,待操作完成后,又将终端电阻恢复到“RTT_Nom”。 【分页导航】

专用复位管脚 DDR3内存有一个专用的复位管脚,若出现错误情况会异步复位内存的内部状态。 低功耗模式 为了在不使用状态下节省电力,DDR3内存也与DDR2内存一样支持节电模式和自刷新模式。在自刷新模式下,DDR3内存可以在系统其他部分处于关闭状态时仍保证数据不丢失。在长时间不进行读取或写入动作时,把CKE信号置于低状态(LOW),可使内存进入节电模式,在这种情况下,内存不会保留任何数据。内存进入节电模式后且所有的存储体都被预充电的状态被称为预充电节电模式;若在节电模式期间,任一存储体处于激活状态,则该状态被称为激活节电模式。把CKE信号置于高状态(HIGH)即可使内存退出节电模式。低功耗模式的转换由内存控制器管理,这样就可以按需使内存进入和退出低功耗模式,从而赋予设备更多的灵活性。通常,DDR3内存会在收到相应命令后的一个内存时钟周期内进入所需的低功耗模式,并在满足必要条件的情况下退出该低功耗模式。根据JEDEC规范,DDR3-800型内存进入和退出节电模式的总时间最少应为7.5ns(欲了解更多详细信息,可参照DDR3JEDEC规范)。 【分页导航】

高效DDR3内存控制器指南 为了更好地管理各类DDR3内存的特性,并提供一种简便的、带宽效率高的自动化方式来初始化和使用内存,我们需要一款高效DDR3内存控制器。内存控制器不仅能在上电后根据编程控制器参数自动初始化内存,还应该提供具有排队、优先级、仲裁和重新排序功能的高带宽接口以便在多个同步内存访问的情况下仍可实现对内存的高效松耦合访问。 一个典型的DDR3内存控制器子系统由以下几部分组成: 1.可满足各种内存访问请求的高带宽接口; 2.在内存初始化阶段用于控制器参数配置的寄存器访问端口; 3.由队列和内存命令处理引擎构成的核心控制器模块; 4.用于驱动输入内存操作到物理内存的物理接口; 5.依照DDR3协议将内存访问请求发送到内存的物理层; 6.用来维持内存接口适当电压等级的专用集成电路(ASIC)管脚校准逻辑。 以下各节将详细讲述上图中控制器的各个组件。 内存访问接口 为了响应外部系统访问内存的需求,DDR3内存控制器设有若干内存访问接口和控制器。为了有效地利用DDR3内存,内存访问接口应可支持高带宽和高频率操作,且多个内存访问接口的设置也可确保内存能够同时响应多个同步访问请求。除了进行读/写数据操作及使能该操作的内存位置地址,接口协议中还应包含访问请求实体和收到每个数据操作的回复机制等信息。此外,为了充分利用DDR3内存的突发式特性,接口协议也要求为突发式。在多个访问接口共存的情况下,接口协议中应设置优先级字段来显示每个数据操作的优先级。 寄存器访问接口 有了寄存器访问接口,程序员就可以在上电期间为特定的DDR3内存初始化配置控制器参数。由于该接口并不一定要在高频率下运行,因此可依照具体要求使用。此外,寄存器访问接口可选支持误码指示,能够在程序员尝试编程一个无效控制器寄存器时发出误码指示。 【分页导航】

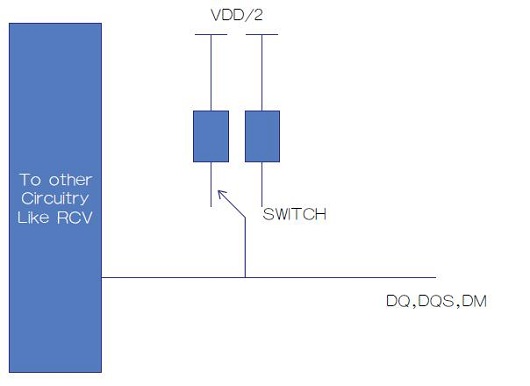

内存物理接口 尽管在控制器和内存物理层之间可以使用自定义的物理接口,但我们仍建议使用DFI兼容接口。DFI兼容接口可为控制器和物理层间提供标准化接口,从而降低成本且便于再利用;DFI兼容接口还可减少针对某厂商的整合工作量,并可实现从FPGA原型到ASIC的无缝迁移。DFI兼容接口的另一显著特性可参见DFI规范。 内存物理层 该模块通过ASIC管脚连接到内存系统,并根据DDR3电气规范与协议规范将数据操作拖放到该模块。除了包含控制DDR3接口信号所必需的逻辑外,该模块还支持其他特性,诸如自动读写均衡,用于时序控制的DLL,以及控制内存进入或退出各种低功耗模式等。由于本文篇幅有限,有关内存物理层的更多详细信息可参考厂商的数据表。 管脚校准 DDR3内存控制器也可配置ASIC管脚校准逻辑,使内存接口上的电压等级维持在适当水平。该逻辑的使用方式类似于DDR2内存的OCD校准特性,通过维持电阻网络中上拉和下拉电阻的平衡,使内存接口的电压等级在不同运行条件下都保持在适当的水平。 调试内存控制器 为完成调试过程,可使用下述组件或特性: 1.可以在控制器上运行多个状态寄存器,更好地了解当前控制器的状态和命令执行情况,还可引入中断信号来指示外部系统发生的关键事件。 2.可以在内存物理层增加用来指示DLL状态的观测寄存器,有助于确认与时序相关的问题。 3.可以在内存物理层执行环回操作,这将能够在不影响其他内存组件的情况下,不必对整个DDR控制器进行编程即可测试连接正确性和数据眼图生成情况。 4.可以在控制器中执行ECC,以检测并纠正内存中的数据损坏。 结论 简而言之,我们可以清楚地看到,尽管对当前DDR2内存的连接拓扑和控制器特性集做了一些强制性改变,但与DDR2内存相比,DDR3内存有着更显著的性能优势。如今,DDR3标准为DDR4标准所取代,通过降低工作电压和增加内存时钟频率,DDR4标准可确保更加高效的运行。此外,DDR4内存的典型工作电压为1.2V,支持的内存时钟频率范围为667MHz~1.6GHz,存储密度更高达16GB(DDR3内存仅为8GB),因而能够在改进能源经济性的基础上带来更高的性能。虽然DDR4是DDR内存标准最新最好的产物,但由于DDR4的普及率比较低,DDR3内存仍是目前最广泛应用的内存。 参考文献 1. JEDEC DDR3 SDRAM standard (JESD79-3F) 2. JEDEC DDR2 SDRAM standard (JESD79-2F) 3. http://www.rambus.com/us/technology/innovations/detail/flyby.html 4. http://www.design-reuse.com/articles/15699/ddr3-ddr2-interfacesmigration.html 5. http://en.wikipedia.org/wiki/DDR3_SDRAM 6. http://pdf.directindustry.com/pdf/elpida-memory/ddr3-sdrambrochure/34572-71260.html 7. www.elpida.com/pdfs/E0594E20.pdf 8. http://www.micron.com/products/dram/ddr3-to-ddr4 【分页导航】

|

网友评论