ЙигкJESD204BзЊЛЛЦїгыFPGAЦЅХфЕФЩшМЦЙиМќЕу

ЗЂВМЪБМфЃК2014-12-15 15:14

ЗЂВМепЃКdesignapp

|

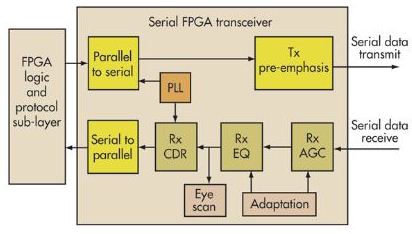

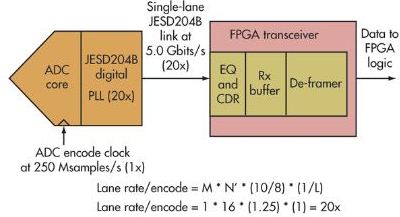

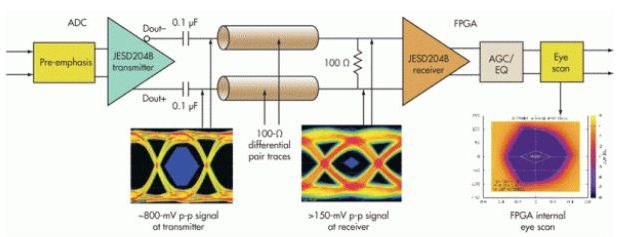

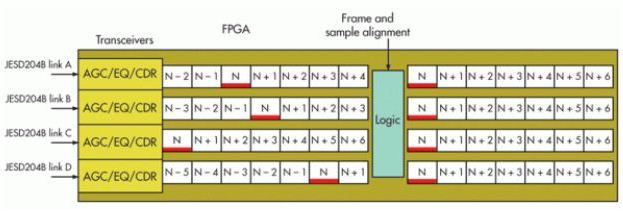

ЫцзХИќЖрЕФФЃЪ§зЊЛЛЦї(ADC)КЭЪ§ФЃзЊЛЛЦї(DAC)жЇГжзюаТЕФJESD204BДЎааНгПкБъзМЃЌГіЯжСЫFPGAгыетаЉФЃФтВњЦЗЕФзюМбНгПкЗНЪНЮЪЬтЁЃFPGAЙЉгІЩЬЖрФъРДвЛжБжЇГжЧЇезДЎаа/НтДЎ(SERDES)ЪеЗЂЦїЁЃШЛЖјдкЙ§ШЅЃЌДѓЖрЪ§ADCКЭDACВЛФмЭЈЙ§етаЉИпЫйДЎааНгПкНјааХфжУЃЌОЭЪЧЫЕFPGAгызЊЛЛЦїЮоЗЈгыШЮКЮГЃгУБъзМНгПкЃЌРћгУИпДЎаа-НтДЎ(SERDES)ДјПэЁЃ JESD204BНгПкеыЖджЇГжИќИпЫйзЊЛЛЦїВЛЖЯдіГЄЕФДјПэашЧѓЖјПЊЗЂЃЌвдЬюВЙИУПеАзЁЃзїЮЊЕкШ§ДњДЎааЪ§ОнСДТЗБъзМЃЌJESD204BЬсЙЉИќИпЕФзюДѓЭЈЕРЫйТЪ(УПЭЈЕРИпДя12.5 Gbps)ЃЌжЇГжШЗЖЈбгГйКЭаГВЈжЁЪБжгЁЃИУНгПкНшжњМцШнПЊЗХЪаГЁFPGAНтОіЗНАИЧвПЩРЉеЙЕФИпадФмзЊЛЛЦїЃЌПЩЧсЫЩДЋЪфДѓСПД§ДІРэЕФЪ§ОнЁЃ ДѓЖрЪ§аХКХДІРэЯЕЭГЪзЯШЪЧЭЈЙ§ЦфФЃФтЛђRFЦЕТЪЁЂЖЏЬЌЗЖЮЇКЭВЩбљЫйТЪНјааЖЈвхЃЌвдНЈСЂзЊЛЛЦїбЁдёБъзМЁЃШЛЖјЃЌЕБгыFPGAЦЅХфНјааЪ§ОнДІРэЪБЃЌЮоТлШчКЮЖМВЛФмКіЪгЖдзЊЛЛЦїЪ§зжНгПкЕФПМСПЁЃжЛвЊСЫНтаТаЭJESD204BНгПкВЂРЮМЧвЛаЉИпМЖПМСПвђЫиЃЌФЧУДЮЊФњЕФFPGAбЁдёКЯЪЪЕФJESD204BзЊЛЛЦїЦфЪЕВЂВЛФбЁЃвдЯТЪЧвЛаЉЙигкJES204BзЊЛЛЦїгыFPGAЦЅХфЕФГЃМћЮЪЬтМАНтД№ЁЃжиЕуЫЕУїВЩгУетПюаТаЭДЎааНгПкНјаазЊЛЛЦїЩшМЦЪБЕФЙиМќЕуЁЃ FPGAЖдгкJESD204BашвЊЖрЩйЫйЖШЃП ЭЈГЃЃЌЩшМЦШЫдБЪЕМЪЩЯЪЧЮЪJESD204BгызЊЛЛЦїНгПкгІгУжаFPGAашвЊжЇГжЕФЪеЗЂЦїЯпТЗЫйТЪЁЃЪеЗЂЦїЪЧFGPAжаЕФИпЫйДЎааНгПкЃЌЦфПЩвдЗЂЫЭЛђНгЪеЪ§ОнМАЛжИДФкЧЖЪБжгЁЃЪеЗЂЦїжївЊзїЮЊИпЫйЪ§ОнЖЫПкЃЌгыЙІФмЮоЙиЁЃЕЋШчЙћдкЦфжмЮЇХфжУКЯЪЪЕФЙЬМўЃЌЫќУЧПЩвдЮЊаэЖрВЛЭЌЕФНгПкавщЬсЙЉ Ъ§зжжЇГжЁЃР§ШчЃЌFPGAЪеЗЂЦїПЩвдГфЕБВЂаажСДЎааЗЂЩфЦїЛђДЎаажСВЂааНгЪеЦї(ЭМ1)ЁЃ  ЭМ1.Р§ШчЃЌFPGAЪеЗЂЦїПЩвдГфЕБВЂаажСДЎааЗЂЩфЦїЛђДЎаажСВЂааНгЪеЦїЁЃ ЖдгкJESD204BетбљЕФИпЫйДЎааНгПкЃЌFPGAЪеЗЂЦїПЩвддкЯЕЭГжавдСНжжЗНЪНЗЂЛгзїгУЁЃЕБFPGAжЇГжADCЭтВПЪ§ОнЯТгЮВЩМЏЪБЃЌЫќЪЧзїЮЊДЎааЪ§ОнНгЪеЦїЁЃЕБЪеЗЂЦїНгЪеЪ§ОнЪБЃЌЫќНЋИпЫйДЎааСїзЊЛЛЮЊВЂаажЁЪ§ОнЃЌдкFPGAжаНјвЛВНЭъГЩЯТгЮДІРэЁЃНЋЪ§ОнДгДЎааИёЪНзЊЛЛЕНВЂааИёЪНЧАЃЌашвЊгУЕНздЪЪгІдівцПижЦ(AGC)ЁЂОљКт(EQ)КЭЪБжг/Ъ§ОнЛжИД(CDR)ЙІФмЁЃ ЕБFPGAЯђDACЪфЫЭЪ§ОнЪБЃЌЫќЛсжДааЗЂЩфЦїЙІФмЁЃзїЮЊЗЂЩфЦїЃЌЫќНЋаЮГЩжЁЪ§ОнЃЌВЂЭЈЙ§ИпЫйНгПкДЎааЗЂЫЭГіШЅЁЃдЄМгжиЙІФм(КѓајЛсЬИЕН)ЗХДѓИУаХКХЃЌвдЪЙДЋЪфЪ§ОнОЁПЩФмИќЭъећЁЃ ЭЈГЃЧщПіЯТЃЌЯЕЭГЕФФЃФтВЩбљЫйТЪЛђИќаТЫйТЪНЋМфНгОіЖЈJESD204BНгПкЩЯЕФFPGAЪеЗЂЦїЯпТЗЫйТЪЁЃзЊЛЛЦїЕФЪБжгЛђБрТыЫйТЪЭЈЙ§ЫјЯрЛЗ(PLL)БЖЦЕРДЪЕЯжJESD204BЮЛЫйТЪЁЃзЊЛЛЦїжЇГжЕФзюДѓЯпТЗЫйТЪПЩФмВЛЪЧЯЕЭГЫљашЃЌЖјгІЕБЭЈЙ§вбжЊЕФБЖЦЕЦїНјааЕїНкЁЃ ЭМ2ЯдЪОСЫвЛИіВЩгУ250 MSPSБрТыЪБжгЕФЕЅвЛ(M = 1)16ЮЛ(NЁЏ = 16)ADCЃЌЫќдк20БЖБрТыЪБжгЫйТЪ(5 Gbps)ЯТЭЈЙ§ЕЅвЛJESD204BЭЈЕР(L = 1)ЗЂЫЭЪ§ОнЁЃИУдЫЫуАќРЈ8ЮЛ/10ЮЛБрТыПЊЯњЁЃзЊЛЛЦїВЩгУгы250 MSPSВЛЭЌЕФБрТыЪБжгЃЌЪфГіЭЈЕРЫйТЪЛсЯргІЕиЯђЩЯЛђЯђЯТЕїНкжС20БЖЕФЕБЧАБрТыЪБжгЫйТЪЁЃ  ЭМ2.ВЩгУ250 MSPSБрТыЪБжгЕФЕЅвЛ16ЮЛADCПЩвдЭЈЙ§ЕЅвЛJESD204BЭЈЕРдк5.0 GbpsЫйТЪЯТЪфГіВЩбљЪ§ОнЁЃБОР§жаЃЌJESD204BЭЈЕРЫйТЪЪЧБрТыЪБжгЦЕТЪЕФ20БЖЁЃ ФФаЉзЊЛЛЦїЬиадПЩгУгкбгГЄЯЕЭГжаЕФJESD204BСДТЗЃЌВЂШдФмБЃГжгХвьЕФЪ§ОнЭъећадЃП JESD204BЙцЗЖСаГіСЫЗћКЯ20cmДЋЪфЯпТЗвЊЧѓЕФБъзМЁЃгЁЫЂЕчТЗАх(PCB)зпЯпВФСЯЕФЮяРэЬиадЖдгкаХКХдкДЋЪфЦкМфЛсгіЕНКЮжжЫЅМѕЦ№жїЕМзїгУЁЃШЛЖјЃЌЖрЪ§зЊЛЛЦїКЭFPGAЩЯЕФгадДЭЈЕРВЙГЅММЪѕгажњгкЬсИпСДТЗадФмЁЃ зЊЛЛЦїЛђFPGAЗЂЩфЦїЪфГіПЩвдЬсИпДЎааЪ§ОнЕФИпДјПэВПЗжЃЌЭЌЪББЃГжЕЭДјПэВПЗжВЛБфЁЃИУММЪѕБЛГЦЮЊдЄМгжиЁЃгЩгкЕЭЭЈаХКХЫЅМѕЪзЯШгАЯьаХКХЕФИпДјПэВПЗж(ЩЯЩ§КЭЯТНЕЪБМф)ЃЌдЄМгжигажњгкЬсИпДЎаааХКХДЋЪфОрРыЁЃ ЖдгкНгЪеЦївВвЛбљЃЌDACЛђFPGAПЩвдЯђЪфШыаХКХЬсЙЉздЖЏдівцПижЦКЭEQЃЌвдЬсИпДЋЪфЯпТЗФЉЖЫПЩМћаХКХЕФИпЦЕВПЗжЁЃИУММЪѕЭЈГЃОпгаВЛЭЌЕФдівцКЭОљКтЦїЩшжУЃЌвдАяжњИљОнЯЕЭГашЧѓгХЛЏЪ§ОнЛжИДЁЃГ§СЫОљКтНзЖЮЃЌXilinxЛЙЬсЙЉФкВПЬНВтЙЄОпЃЌДгЖјНЋдкFPGAжаМћЕНЕФЪ§ОнблаЮЯѓЛЏ(ЭМ3)ЁЃ  ЭМ3.дкADCжСFPGAЕФJESD204BДЋЪфЯпТЗжазЊЛЛЦї/ЗЂЩфЦїЕФдЄМгжиЃЌЗХДѓСЫаХКХЕФИпДјПэВПЗжЃЌЭЌЪБНгЪеЦї/FPGAЕФОљКтПЩЛжИДЫЅМѕаХКХЁЃXilinxЕФФкВПблЩЈУшЙЄОпПЩЖдFPGAжаЕФблНјааФкВПЬНВтЁЃ еыЖдзЊЛЛЦїЛЙФмзіаЉЪВУДДІРэЃЌвдМѕЩйЗЂЫЭИјЛђРДздгкFPGAЕФЪ§ОнСПЃП ЮЊСЫМѕаЁFPGAЕФМЦЫуИКЕЃЃЌвЛаЉзЊЛЛЦїЙЉгІЩЬдкећИізЊЛЛЦїНтОіЗНАИжаЬэМгСЫЪ§зжДІРэВПЗжЁЃвЛаЉаХКХДІРэЯЕЭГжЛашЪЙгУОТЫВЈЕФаХКХДјПэВПЗжЁЃЗЂЩфКЭДІРэЫЭжСЛђРДздFPGAЕФШЋДјПэЪ§ОнЪЧвЛжжПЊЯњИКЕЃЃЌЭъШЋУЛгаБивЊЁЃ Р§ШчЃЌADCПЩЪЕЯжЪ§зжЯТБфЦЕ(DDC)ЙІФмЃЌПЩвдгааЇЕиНЋНЋУПЫФИіФЃФтВЩбљжаЕФЕквЛИіЗЂЫЭИјFPGAЁЃЪ§зжТЫВЈЪ§ОнПЩдкJESD204BНгПкЩЯЪЙгУИќЕЭЕФЪ§ОнЫйТЪЃЌВЂЧвЮоашдкFPGAЩЯХфжУDDCЪБжгЁЃ ЯрЗДЃЌDACВхжЕЙІФмПЩвддЪаэНіЪЙгУ1/4Ъ§ОнЫйТЪЃЌНЋЪ§ОнДгFPGAЗЂЫЭжСDACЃЌВЂЧвЪЙгУИДдгЫуЗЈЖдЫФИіВЩбљжаЕФЦфгрШ§ИіНјааЪ§зжВхжЕЁЃDACВхжЕЗНЪННіПЩвдДЋЪфЪ§ОнЕФвЛИізгМЏЃЌШЛКѓдкВЩгУФЃФтИёЪНЪфГіЧАдкзЊЛЛЦїжаЭъШЋзщзАЁЃ ЮвЕФFPGAашвЊжЇГжЖрЩйSERDESЭЈЕР/зЊЛЛЦїЃП ЮоТлФњЕФСДТЗЪЧВЩгУЕЅвЛзЊЛЛЦїЛЙЪЧЖрИізЊЛЛЦїЃЌзЊЛЛЦїНггыFPGAНгПкЕФJESD204BЭЈЕРЪ§гыЯпТЗЫйТЪЁЂзЊЛЛЦїВЩбљЫйТЪЁЂЪ§ОнАќаЇТЪжБНгЯрЙиЁЃЫфШЛзЊЛЛЦїПЩвдЬсЙЉЫФЬѕJESD204BЭЈЕРЃЌЕЋвд1/2зюДѓзЊЛЛЦїВЩбљЫйТЪдЫааЕФЯЕЭГПЩФмНіашЪЙгУСНЬѕЭЈЕРЁЃУПИізЊЛЛЦїПЩвРВЛЭЌЕФЩшМЦРДЪЕЯжВЛЭЌЕФJESD204BЭЈЕРЪ§ЁЂЫйЖШКЭЪ§ОнАќЁЃПЩВщПДзЊЛЛЦїЪ§ОнЪжВсЃЌПДПДЪВУДбЁЯюзюЪЪКЯФњЕФгІгУЁЃ ЮвФмЙЛНЋЖрИізЊЛЛЦїгыЕЅвЛFPGAЪЕЯжЭЌВНТ№ЃП ЪЧЕФЃЌетПЩвдзіЕНЃЌжЛвЊFPGAжЇГжЕФЭЈЕРЪ§зувдТњзугІгУЫљашЁЃЖрADCЯЕЭГЕФжївЊФбЕужЎвЛЪЧЖдЦыВЩбљаХКХЃЌетаЉаХКХдкДгФЃФтжСЪ§зжВЩбљЙ§ГЬжаОпгаВЛЭЌЕФбгГйЪБМфЁЃJESD204BНгПкЖдЯЕЭГВЮПМаХКХ(SYSREF)гаЯргІЙцЖЈЁЃетгажњгкЮЊЯЕЭГжаЕФИїзЊЛЛЦїДДСЂШЗЖЈЕФбгГйЪБМфЃЌДгЖјЮЊЖр зЊЛЛЦїЭЌВНЬсЙЉНтОіЗНАИЁЃгЩгкJESD204BЩЯВЩгУЪ§ОнжЁЃЌРДздгкЖрИіADCЕФЪ§ОнжЁОЭПЩвддкFPGAЕФКѓДІРэВНжшжаЖдЦыЁЃетбљОЭПЩвдаЃе§зЊЛЛЦїКЭFPGAЪеЗЂЦїжЎМфЕФбгГйВЛЦЅХфЁЃ ЭЌбљЃЌFPGAдкНЋЪ§ОнЗЂЫЭжСЖрИіDACЧАЃЌПЩвдЯШНЋЪ§ОнНјаажЁЖдЦыЁЃетЪЧПМТЧЕНФЧаЉашвЊЭЈЙ§ЕЅвЛЛђМИИіFPGAРДЭЌВНЖрИізЊЛЛЦїЕФЯЕЭГЁЃвЛаЉзЊЛЛЦїЙЉгІЩЬЛЙдке§ЪНММЪѕЙцИёЭтЬсЙЉЖюЭтЕФЭЌВНЙІФмЃЌгУгкБъзЂЬиЖЈВЩбљЁЃШчЙћФњЕФЯЕЭГашвЊЖрзЊЛЛЦїЭЌВНЃЌашОЁСПМѕЩйзЊЛЛЦїСЌНгЕФJESD204BЭЈЕРЪ§ЃЌВЂбЁдёзюЧПадФмЕФFPGAЁЃ JESD204BавщжаЙцЖЈЃЌашЖдЦыРДздгкЖрИіADCЁЂОпгаВЛЭЌбгГйЕФВЩбљЪ§ОнДгЖјдкFPGAжаЪЕЯжЭЌВНЁЃЭМ4ЯдЪОСЫРДздЖрИіСДТЗЕФжЁЪ§ОнЛђБъМЧЕФбљБОШчКЮеыЖдЭЌВНДІРэНјаажиЖдЦыЁЃ ЮвЕФгІгУашвЊдѕбљЕФFPGAВМЫйРДДІРэЪ§ОнЃП JESD204BНгПкВЩгУЧЖШыЪНЪБжгРДНјааИпЫйДЎааЪ§ОнДЋЪфЁЃШЛЖјЃЌFPGAашвЊИќТ§ЕФВЮПМЪБжгзїЮЊжїЪБжгРДДІРэЪ§ОнЁЃFPGAЯЕСаКЭВњЦЗЕФВМЫйОіЖЈетвЛЙІФмЁЃПМТЧFPGAашбЁдёФФжжЗНЪНДІРэзЊЛЛЦїЪ§ОнЯрЕБживЊЁЃР§ШчЃЌИКд№ВЩМЏжмЦкадРыЩЂЪ§ОнМЏжСДцДЂЦїЕФгІгУЃЌКЭШЋЫйСЌајДІРэВЂЗЂЫЭЪ§ОнЕФгІгУЃЌетСНепПЩФмашвЊВЛЭЌЕФFPGAВМЫйЁЃ ШчКЮШУJESD204BдкFPGAЩЯЙЄзїЃП ИУЮЪЬтЕФСэвЛжжБэДяПЩФмЪЧЁАЮвгІЕБДгFPGAжЦдьЩЬФЧРяЛёЕУJESD204BЙЬМўЕФжЊЪЖВњШЈ(IP)ЛЙЪЧздМКПЊЗЂЃПЁБ XilinxЕШFPGAЙЉгІЩЬОљЬсЙЉгУгкJESD204ЁЂJESD204AКЭJESD204BНгПкЕФзджїIPНтОіЗНАИЁЃетаЉНтОіЗНАИПЩФмТдгаВювьЃЌетШЁОігкJESD204ЕФВњЦЗЛЛДњвдМАFPGAВњЦЗЕФЪеЗЂЦїЫйЖШЁЃ ШЗБЃОЁдчЭъГЩзЊЛЛЦїбЁаЭЃЌУїШЗФњЕФЯЕЭГжаашвЊВЩгУЕФFPGAаЮЪНКЭЯрЙиIPЁЃбЁаЭЪБгІЕБПМТЧЪЙгУФФМвFPGAЙЉгІЩЬЕФВњЦЗЁЂЪЙгУФФвЛДњJESD204ЁЂFPGAЕФЯЕСаКЭаЭКХЃЌвдМАФњФкВПЪЕЯжIPЫљашЕФММЪѕДњТыБраДФмСІЁЃ вЛаЉJESD204BзЊЛЛЦїПЩФмашвЊЬиЪтЕФЖюЭтгІгУВуЃЌЛђЪЧЮЇШЦIPЕФДњТыЁААќзАЦїЁБЃЌетЛљБОЩЯЪЧвЛЬзЖРгаЕФЙЬМўжИСюЁЃШчЙћЪЧетжжЧщПіЃЌзЊЛЛЦїЙЉгІЩЬгІЕБШЗШЯВЂЬсЙЉгІгУДњТывдСЌНгFPGA IPЁЃгІЕБдкЪ§ОнЪжВсжаСаУїашвЊФФаЉФкШнРДжЇГжJESD204BзЊЛЛЦїСДТЗЁЃвЛаЉзЊЛЛЦїжЦдьЩЬЛЙПЊЗЂСЫвЛжждкЫћУЧЕФЦїМўКЭFPGAЙЬМўМфНјааГЙЕзбщжЄВтЪдЕФЕчГиЃЌвджЄУїВњЦЗЕФЮШЖЈадЁЃ зЊЛЛЦїЪЙгУОпгаЪеЗЂЦїЁАЦЕТЪЖДЁБЕФFPGAЪБЛсГіЯжЮЪЬтТ№ЃП вЛаЉFPGAВњЦЗжЇГждЫааЙ§ГЬжаДцдкМфЯЖ(ЮоЗЈЪЙгУвбжЊЕФЦЕТЪЗЖЮЇ)ЕФЪеЗЂЦїЁЃетЛсЪЙJESD204BЭЈЕРЦЕТЪЙцЛЎИќИДдгвЛЕуЃЌЕЋШддкПЩПиЗЖЮЇФкЁЃеыЖдзЊЛЛЦїВЩбљЫйТЪКЭJESD204BЭЈЕРЫйТЪНјааЦЕТЪЙцЛЎЪЧЪЙЦЕТЪдЖРыЪеЗЂЦїМфЯЖЕФЙиМќЁЃ ДѓЖрЪ§зЊЛЛЦїЯЕЭГЭЈГЃЖМгаЙЬЖЈЕФВЩгУЦЕТЪЁЃашвЊЖдХМШЛЕФЖРЬигІгУНјаажЇГжЕФЧщПіжЛЪЧЩйЪ§ЁЃИљОнЯЕЭГзЊЛЛЦїЕФЙЬЖЈВЩбљЫйТЪКЭжЎЧАЬжТлЕФJESD204BЫйТЪБЖЦЕЦїЃЌЯЕЭГЩшМЦШЫдБПЩвдШЗЖЈЪеЗЂЦїЦЕТЪМфЯЖЪЧЗёЛсЖдЯЕЭГдьГЩЮЪЬтЁЃ МДЪЙЗЂЯжЦкЭћЕФЭЈЕРЦЕТЪИеКУдкМфЯЖЗЖЮЇФкЃЌШдашВщПДзЊЛЛЦїЪ§ОнЪжВсЃЌПДПДЪЧЗёгаСэвЛаЉбЁЯюПЩгУРДЕїећЭЈЕРЫйТЪЁЃР§ШчЃЌПЩвдИФБфЗНГЬжаЕФвЛаЉЦфЫћБфСПЃЌШчЭЈЕРЪ§СПЛђJESD204BВЩгУЗжБцТЪаХЯЂЃЌРДЬсИпЛђНЕЕЭЦЕТЪЧњЯпЃЌвдБмПЊЪеЗЂЦїЦЕТЪМфЯЖЁЃ  ЭМ4.JESD204BавщжаЙцЖЈЃЌЖдЦыРДздгкЖрИіADCЁЂОпгаВЛЭЌбгГйЕФВЩбљЪ§ОнДгЖјдкFPGAжаЪЕЯжЭЌВНЁЃРДздЖрИіСДТЗЕФжЁЪ§ОнЛђБъМЧЕФбљБОПЩеыЖдЭЌВНДІРэНјаажиЖдЦыЁЃ аЁНс аТаЭзЊЛЛЦїгыJESD204BжЎРрЕФFPGAНгПкНЯЮЊИДдгЃЌЪЙЦфЯдЕУФбгкДІРэЃЌДЫЪБЗжНтЙиМќЯЕЭГашЧѓжСЙиживЊЁЃБиаыСЫНтВЩбљЫйТЪКЭJESD204BЭЈЕРЫйТЪБЖЦЕЦїЁЃИљОнIPжЇГжЁЂЪеЗЂЦїЪ§ЁЂЪеЗЂЦїЫйЖШКЭЦЕТЪМфЯЖЕШвђЫиРДНјааЙцЛЎКЭбЁдёКЯЪЪЕФFGPAВњЦЗЃЌгажњгке§ШЗбЁдёзЊЛЛЦїЁЃЭЈЙ§жиЕуЙизЂвЛаЉгыFPGAЯрЦЅХфЕФИпМЖБъзМЃЌПЩМђЛЏбЁдёКЯЪЪЕФJESD204BзЊЛЛЦїЕФЙ§ГЬЁЃ |

ЭјгбЦРТл