ADSL收发器片上系统芯片的设计与实现

发布时间:2010-6-23 10:31

发布者:zealot

|

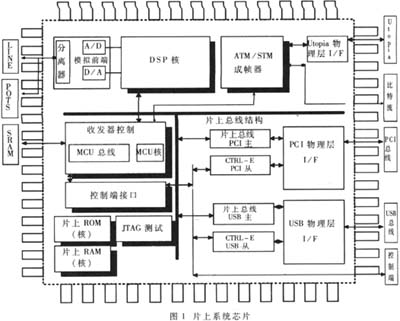

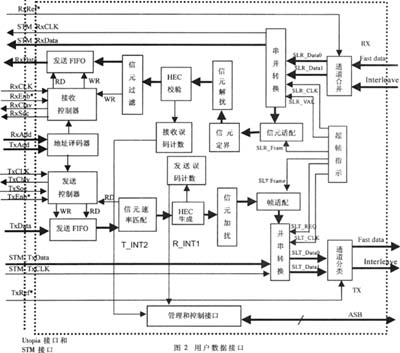

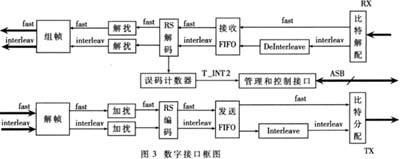

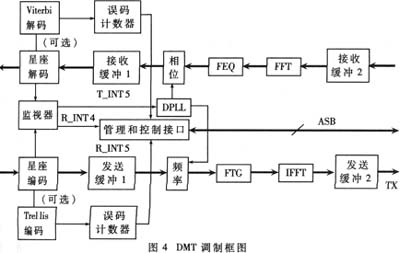

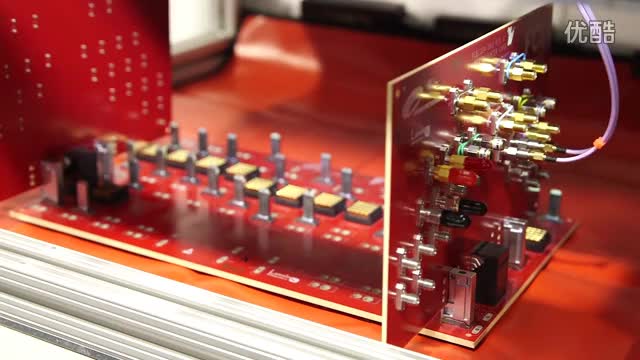

数字信号处理非对称数字用户环路ADSL是目前宽带接入网技术中最具前景及竞争力的一种1。虽然欧美一些先进国家在ADSL示范网上取得了成功?但在当前Internet的应用环境中?要广泛应用ADSL还有阻力。主要原因是ADSL系统技术较为复杂,采用集成电路(IC)设计方法,通过印刷电路板PCB来将多芯片集成为系统,系统实际性能并不理想,同时使得ADSL设备制作成本较高因此难以推广使用。采用片上系统设计方法2?3?4把各个子系统有机地集成到一个芯片上去,可以很好地克服多芯片集成系统所引起的系统性能问题,使ADSL真正成为一种高速、低成本的Internet高速接入技术。本文介绍ADSL收发器片上系统芯片设计,给出了硬件实现的具体描述。 1 ADSL收发器片上系统芯片总体设计 设计的片上系统System on a Chip芯片如图1所示.  其中存储器核采用NMI Electronics存储器核PCI采用Eureka Technology的PCI核 DSP核选用某公司的DSP核?DSP算法自主设计开发。MCU核完成与DSP核、ATM成帧器核及各种接口的通信、控制、管理功能,包括PCI总线接口、USB接口、10BASE-T接口及内部总线的协调控制工作,通过专用逻辑模块来完成;DSP核致力于完成收发器设备中各种核心算法,包括ADSL子信道划分算法、DMT(离散多音频调制)子信道比特分配算法、功率调整、非线性回波抵消算法、自适应均衡算法等;模拟前端AFE核完成A/D、D/A转换、线路驱动及分离器功能;ATM成帧器核完成ATM帧头定位及成帧功能,其中的逻辑电路完成CRC编解码、扰码与解码、RS编解码、交织与解交织和TCM编解码;通过模式选择本设计可以工作于ATM和STM两种模式下;本芯片还提供了控制通道(RS232接口),实现对系统的管理、监视和调试功能。设计特点 (1)模拟前端核与其他核集成在一起?避免了线性驱动器件中常见的四个电源至少需要三个的情况实现了高效率、低功耗的设计。(2)可在局端DSL接入复用器中直接当作线卡来用,以提供高速因特网接入服务。(3)支持所有最新的ADSL标准,包括ANSI T1.413 Issue 2、ITU G.992.1和ITU G.992.2。它还提供了G.Lite运作所需要的低开销、快速启动和再训练功能。(4)通过控制口提供配置和控制ADSL线的所有功能,减轻主机控制器的管理负担。 2 芯片中的典型电路设计与实现 2.1 ATM成帧器设计 ATM成帧器完成用户数据接口功能。用户数据接口将接收的Utopia接口或者STM接口数据分为快速通道和交织通道,或者将快速和交织通道的数据送入Utopia接口或者STM接口。用户数据接口分为接收方向和发送方向两个部分,发送方向是由芯片外向芯片内,所处理数据包括ATM数据(utopia接口)、STM数据,将其组成为ADSL超帧,并分为交织通道和快速通道;接收方向是将交织通道和快速通道的数据通过解帧等变换发送出去,也分为utopia接口数据、STM数据。其大致的结构如图2所示。  STM接口在发送方向包括STM_Data和STM_CLK两种信号,在接收方向包括STM_Data和STM_CLK两种信号。在发送方向,STM信号经过并串转换后,以串行方式进行传送,SLT_Data0传送偶数比特,SLT_Datal传送奇数比特,然后在通道分类中根据外部微处理器的配置(通过控制接口)将数据送入fast通道或者interleave通道。在接收方向,从fast通道和interleave通道中来的数据在通道合并中合并为串行数据,SLR_Data0传送偶数比特,SLR_Data1传送奇数比特,再经过串并转换送到STM接口中。其中,超帧指示模块主要产生指示超帧的信号(包括接收和发送方向),VAL和REQ是字节数据有效信号,Frame信号是数据超帧开始信号,CLK信号是超帧时钟。根据Utopia协议可以知道,Utopia 接口每个字节数据都是由一个时钟周期来传送的,所以传送一个信元可以用53个时钟周期。在发送方向和接收方向的同步时钟信号都是由ATM层发出的,可以把他们看成是异步时钟。从Utopia接口进入芯片的数据首先通过地址译码,选择发送的端口地址,然后由发送控制器控制从Utopia接口来的数据,将它们存入发送缓冲,然后到信元速率接口控制器。 信元速率控制器模块的功能为:当ATM层发送的信元速率小于ADSL的下行传送数据速率时,信元速率控制器就插入一些空信元来使两者的数据速率匹配。HEC生成模块的功能:处理信元的HEC,提高出现滑码时的信元定界能力。在处理信元的HEC过程中,如果发生错误,可以将错误发生次数在接收误码计数器中记录下来,用于以后的性能监测中。信元加扰模块的功能:防止在信元负荷中出现与HEC相同的情况。帧适配模块的功能:将信元数据流整理成适于ADSL超帧数据结构。一方面实现同步,可以通过插入或者删除AEX、LEX来实现帧的同步。在ADSL中可以通过填充字节LEX、AEX来实现。如果发送时钟稍快一点,将把固定的字节数用完,这时可以用LEX、AEX来传送数据。如果发送时钟稍慢一点,固定的字节数将不会被用完,这时候可以不用LEX、AEX字节。这种过程可以通过eoc中的同步指示信号(ib)来表示,由外部微处理器来处理。帧适配模块的另一方面功能是可以提取aoc、eoc、ib等子节。并串转换模块的功能:将数据流进行并串转换后送入通道分类模块。通道分类模块的功能:将奇数和偶数的串行数据流合并成一列数据流,根据Utopia接口的TxAdd信号或者外部微处理器的配置(控制接口中的寄存器)送入fast通道或者interleave 通道。需要指出的是接收方向与发送方向数据流向相反,不再解释。 2.2 数字接口设计 根据ADSL协议要求?数字接口主要将信道中的快速和交织的数据经过扰码、FEC编码后形成可以传送的数据。大致框图如图3所示。  在发送方向,从用户数据接口来的fast(快车)通道和interleave(交织)通道的数据先分别进行CRC校验,然后进入解帧模块,在这个模块中,将超帧分解为一个一个的数据帧,存入缓冲中。然后对fast和interleave数据分别进行加扰,这种加扰是对每个数据帧进行加扰,加扰后的数据进入RS编码模块,之后进入发送FIFO。对于Interleave数据,从发送FIFO出来以后就进行交织处理,然后将两种数据进行比特分配,对每个子信道分配一定的比特数,这可以参考比特分配表格(在初始化时计算出来,存放在缓存之中)。 在接收方向,从DMT调制模块来的数据进入比特解配,对Interleave数据再经过de_interleave模块之后进入接收FIFO,然后进入RS解码模块,当发现错误时,将误码计数器加1,计数结果将用于性能。从RS解码出来的数据经过解扰后,送入组帧模块,在这个模块中,将各个数据帧组合成超帧,然后将数据进行CRC校验,最后送到用户数据接口。 2.3 DMT调制电路设计 DMT调制是ADSL收发器片上系统芯片中的重要模块之一,主要完成数据在每个子信道上的调制,它的好坏直接关系到ADSL收发器芯片性能的好坏。DMT中大部分的计算都通过DSP来完成,如FFT/IFFT、FEQ、TEQ、星座编码和解码、Trellis编码和Viterbi解码等功能。与DSP的联系主要通过数据和程序地址总线来完成。DMT调制模块大致框图如图4所示。  在发送方向,从数字接口来的数据流已经是每个子信道的比特分配流,这种数据流在星座编码模块中进行星座编码,将频域的比特流信号转换成时域的星座平面上的复数(X+iY)信号,然后进行2D QAM调制。这时候可以选择Trellis编码(四维格状调制),用以产生冗余比特来增强发送的可靠性。然后将经过星座编码后的数据存入发送缓冲。由于信道失真或者其他的原因,从缓冲出来的数据在频率和相位上都与主时钟频率和相位不匹配。所以为了调整这种不匹配,从缓冲出来的数据先经过频率调整和增益微调(FTG)。频率调整是调节发送频率,保证发送频率和理想频率的一致,FTG是调节每个子载波上的增益稀疏。然后再进入快速傅立叶逆变换(IFFT),将频域的DMT符号转换成时域的信号,送入发送缓冲之中,最后送入模拟前端接口。 在接收方向,从模拟前端接口来的数据是经过时域均衡(TEQ)以后的,这些数据首先进入接收缓冲,之后进入快速傅立叶变换(FFT),将时域的DMT信号转换成频域的信号(512点),然后在频域均衡(FEQ)和相位调整模块中消除相应的干扰,送入接收缓冲,之后进行星座解码,从而将星座平面的复数点转换为比特流。如果接收的数据使用了Trellis编码,那么在星座解码后的数据将再通过Viterbi解码模块之后,送入数字接口。 在第64个子信道中传送的时导频信号,在发送和接收方向都是通过DPLL数字锁相环来保证发送和接收时钟与导频信号一致。当星座编码和解码时,发现导频信号的星座点的位置与理想的点位置不一致时,就要通过DPLL和相位调整/频率调整模块来纠正。同时,监视器可以发送中断R_INT4信号到管理和控制接口,通过ASB与内部ARM核通信。DPLL的功能有:(1)DPLL中恢复导频信号的功能。为了保证收发时钟有固定的相位关系,在ADSL中采用了插入导频的方法来传送和恢复时钟信号。发送器在发送数据的同时用64号子信道传送独立的导频信号,抽样时钟频率为2208kHz,而导频信号的频率为276kHz,恢复了导频信号后,利用锁相环锁住抽样时钟频率,从而实现时钟的恢复。(2)在PLL中通过一个时钟源产生内部的所需时钟。其中内部所需时钟包括:CPU时钟、DSP时钟、各种算法的时钟等。PLL锁相环的外界参考晶体的频率可以为:35.328MHz。 在Trellis编码和Viterbi解码时,分别有一个误码计数器与之相连,当发生错误时,误码计数器加1,加到一定数值,就通过发送中断信号T_INT5、R_INT5通知内部ARM核。 3 非对称数字用户环路收发器的片上系统芯片设计难点 3.1 DSP算法设计及实现 DSP算法是ADSL收发器SOC芯片的核心?其工作的好坏直接影响整个芯片的性能?而ADSL收发器中涉及的DSP技术又非常复杂给设计增加了难度。DSP算法的设计首先要建立算法模型,以模型为基础进行算法设计,继而设计优化模型并以此为根据对算法进行优化,使算法准确、稳定,能很好地满足性能要求。下一步就是硬件软件实现及二者的协同设计和验证,验证是为了优化VLSI硬件和功能结构,有效快速地执行算法,最后进行DSP系统集成。 3.2数模混合设计 为了降低功耗,提高电子器件的效率,把模拟前端AFE与微控制器MCU核等集成到一起。在一个数字芯片上集成混合信号内核时,缺乏线性电阻是一个主要问题?因为连续时间序滤波器要求片上电阻具有良好的可控性和线性。电流开关DAC也要用线性电阻把电流转变成电压。把数字噪音与模拟噪音隔离开是另外一个问题,必须采用具有较高共模抑制比CMRR 和电源抑制比的完全差动设计。 3.3系统验证问题 随着系统级芯片SOC复杂性的增加,传统使用HDL软件模拟器来进行验证的方法已经不够用了,它无法提供所需的性能,以检查系统功能的正确性。而且SOC芯片的验证需要对整个系统建立模型,要将很多实际的情况加入到模型之中,来证明整个系统以及芯片都工作正常。因此,需要有一个灵活的建模环境,以便处理大量的系统级方案。处理界面入口TIP 可以在抽象层软件和详细的硬件实现之间提供一个高速链接,执行任务软件、验证系统级操作以及快速发现设计中的问题。 3.4 系统测试问题 SOC芯片的测试技术难度较大。SOC芯片测试设备则必须能够精确地检测模拟和数字两种电路,并支持扫描检测和嵌套式存储器检测。对输入引脚加测试向量,再从输出引脚观察结果的传统检测方法已不适用。因为,传统方法测试向量集会过分庞大,执行时间也会长得惊人。 4 设计实现 采用软硬件协同仿真设计,在大型EDA仿真软件Cadence的数字模拟混合设计工具Spectra上,用硬件描述语言Verilog完成设计输入,进而完成设计综合、功能仿真、布局布线、后仿真和产生构造位流文件。 以上介绍了ADSL收发器片上系统芯片设计,给出了相应硬件设计的具体描述?对设计特点、难点进行了阐述。 |

网友评论