»γΚΈ‘ΎΙη–ΨΤ§÷ΤΉςΆξ≥…«ΑΫχ––»μΦΰΩΣΖΔ

ΖΔ≤Φ ±ΦδΘΚ2014-12-3 13:54

ΖΔ≤Φ’ΏΘΚάνΩμ

|

Ής’ΏΘΚRussell KleinΘ§”≤ΦΰΦ”ΥΌΤςΖ¬’φ≤ΩΟ≈ΦΦ θΉήΦύΘ§Mentor GraphicsΙΪΥΨ Τ§…œœΒΆ≥(SoC)ΩΣΖΔ≤Μ‘ΌΫωΫω «ΦρΒΞΒΡΙη–ΨΤ§ΩΣΖΔΙΐ≥ΧΓΘœ÷¥ζ…η±Η¥σΝΩ Ι”ΟΝΥΗς÷÷»μΦΰΘ§Αϋά®»μΦΰ’ΜΓΔ÷–ΦδΦΰΓΔΤτΕ·¥ζ¬κΚΆ«ΐΕ·≥Χ–ρΓΘΡψ¥σΩ…”Τ»ΜΉ‘»τΒΊΒ»ΒΫΙη–ΨΤ§ΩΣΖΔΆξ≥…ΚσΘ§‘ΌΫΪΤδΖ≈‘ΎΒγ¬ΖΑε…œΩΣ ΦΫχ––»μΦΰΒΡΩΣΖΔΓΘ»ΜΕχ‘ΎΦΛΝ“ΒΡ –≥ΓΨΚ’υ÷–Θ§ ±ΦδΨΆ «…ζΟϋΓΘΩΣΖΔΫχΕ»»’“φΫτΤ»Θ§»τΡή‘ΎΙη–ΨΤ§÷ΤΉςΆξ≥…«Α±ψΉ≈ ÷Ϋχ––»μΦΰΩΣΖΔΘ§ΫΪ≥…ΈΣ“ΜΗωΨό¥σΒΡΨΚ’υ”≈ ΤΓΘ“ΣΉωΒΫ’β“ΜΒψΘ§–η“Σ¬ζΉψ“‘œ¬»ΐΗω“Σ«σΘΚ Ήœ»Θ§–η“Σ“ΜΧΉΩ…Ι©ΦΡ¥φΤς¥Ϊ δΦΕ(RTL)…ηΦΤΗΏΥΌ‘Υ––ΓΔ«“‘ΎΙη–ΨΤ§ΜρΩΣΖΔΑεΉΦ±ΗΨΆ–ς«ΑΨΆΡή‘Ύ…œΟφ’ΐ≥Θ‘Υ––»μΦΰΒΡΖ¬’φœΒΆ≥ΘΜ¥ΥΆβΘ§ΜΙ–η“Σ“ΜΗωΗΏΥΌΓΔΜυ”Ύ ¬ΈώΒΡ–≠Ά§Ϋ®ΡΘΆ®ΒάΫΪΖ¬’φΤς”κΜυ”ΎΙΛΉς’ΨΒΡ»μΦΰΒς ‘ΙΛΨΏΫχ––Ν§Ϋ”ΘΜΉνΚσΘ§ΜΙ–η“ΣΧαΙ©ΖϊΚœ»μΦΰΩΣΖΔ’Ώ–η«σΒΡ»μΦΰΒς ‘ΜΖΨ≥ΓΘ ΈΣ“Μ÷÷”≤ΦΰΜΙΟΜ”–≥…–ΆΒΡ≤ζΤΖΩΣΖΔ»μΦΰ ±Θ§ Ήœ»–η“Σ“ΜΗωΡή‘Υ––¥ζ¬κΒΡΜΖΨ≥ΓΘΆ®≥Θ”–ΝΫ÷÷―Γ‘ώΘΚΈοάμΜΖΨ≥Μρ–ιΡβΜΖΨ≥ΓΘ¥σΕύ ΐœνΡΩΕΦ «Μυ”ΎΡ≥Ηωœ÷”–…ηΦΤΘ§Φ¥‘Ύ‘≠”–Αφ±Ψ÷–ΧμΦ”Ρ≥–©ΙΠΡήΘ§ Ι‘≠”–Αφ±ΨΙΠΡήΗϋ«ΩΓΔΥΌΕ»ΗϋΩλΓΔ–‘ΡήΗϋΚΟΓΘ’β÷÷«ιΩωœ¬Θ§”–Ω…Ρή¥”Ϋ” ÷œνΡΩΒΡ‘≠”–…ηΦΤΑφ±Ψ÷–÷±Ϋ”Μώ»Γœ÷≥…ΒΡΒγ¬ΖΑεΘ§Μρ’ΏΡή»ΓΒΟΗΟΒγ¬ΖΑεΒΡ»μΦΰΜΖΨ≥“‘Ϋχ––»μΦΰΩΣΖΔΘ§”ΟΉ‘ΦΚΒΡΒς ‘ΜΖΨ≥ά¥Ε‘ΤδΫχ––―ι÷ΛΓΘΒΫΡΩ«ΑΈΣ÷ΙΘ§ΉνΦρΒΞΒΡΉωΖ®ΨΆ «‘Ύœ÷≥…ΒΡΒγ¬ΖΑε…œ‘Υ––ΓΘ»γΙϊ «ΩΣΖΔ“ΜΗω»Ϊ–¬ΒΡ»μΦΰΘ§ΡψΩ…“‘ Ι”Ο“ΜΩιΩΣΖΔΑεΘ§‘ΥΤχΚΟΒΡΜΑΘ§Μρ–μΜΙΡή’“ΒΫάύΥΤΒΡΩΣΖΔΑεΓΘΜΙ”–“Μ÷÷Ω…––ΒΡΖΫΖ®Θ§Φ¥‘Ύ“ΜΗω–ιΡβΒγ¬ΖΑε…œ‘Υ––Θ§»γ–ιΡβΜζ(QEMU)ΓΘQEMU «“ΜΗωΩΣ‘¥œΒΆ≥Ζ¬’φΤςΘ§Ω…Υφ“βΡΘΡβΗς÷÷ARMΑεΓΘARMΙΪΥΨ“≤ΧαΙ©“ΜΗω–ιΡβΤΫΧ®Θ§≥ΤΉςΓΑΜυ¥ΓΡΘ–ΆΓ±(Ω…‘ΎΤδΆχ’Ψ…œΟβΖ―ΜώΒΟ)Θ§άύΥΤ”ΎQEMUΘ§Ω…‘Υ––ARM¥ζ¬κΓΘΕΰ’ΏΕΦ”–“ΐ»κΒς ‘ΤςΒΡΙΛΨΏΓΘ

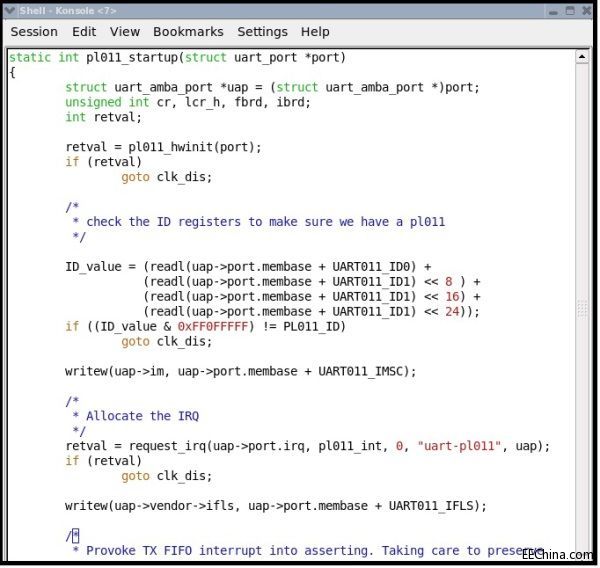

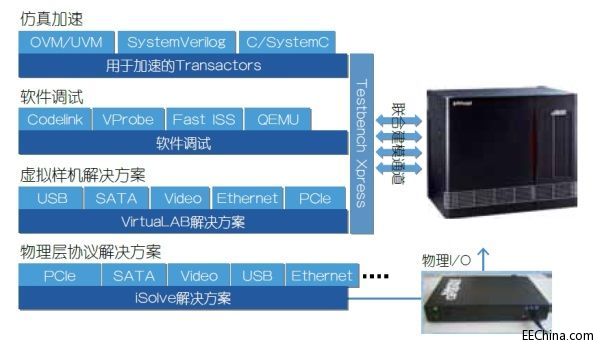

ΆΦ1ΘΚMentorΙΪΥΨ―ι÷ΛΤΫΧ®ΫΪœ»ΫχΒΡΖ¬’φΤςΫβΨωΖΫΑΗΓΔ”≤ΦΰΦ”ΥΌΤςΤΫΧ®“‘ΦΑ«Ω¥σΒΡΒς ‘ΜΖΨ≥’ϊΚœ‘Ύ“ΜΗω»Ϊ«ρΙ≤œμΒΡΗΏ–‘Ρή ΐΨί¥Πάμ÷––ΡΉ ‘¥άοΓΘ ”–ΝΥΩ…‘Υ––ΚΆΒς ‘¥ζ¬κΒΡΜΖΨ≥Θ§ΨΆΩ…“‘ΩΣ Φ±ύ≥ΧΝΥΓΘΡ≥–©«ιΩωœ¬Θ§ΡψΫΪ–η“ΣΖΟΈ “Μ–©ΜΙΈ¥≥…–ΆΒΡ»Ϊ–¬ΆβΈß…η±ΗΘ§”ΠΕ‘¥ΥΈ ΧβΒΡ“ΜΗωΫβΨωΖΫΑΗ «¥¥Ϋ®“ΜΗωΡΘ–ΆΓΘΈ“Ο«œ»¥”“ΜΗωΖ«≥ΘΦρΒΞΒΡάΐΉ”»κ ÷ΘΚΕΝ»Γ’βΗω–¬ΆβΈß…η±ΗΒΡIDΦΡ¥φΤςΓΘ–μΕύΆβΈß…η±ΗΕΦ”–IDΦΡ¥φΤςΘ§’β «“ΜΗω÷ΜΕΝΦΡ¥φΤςΘ§ΕΝ»Γ ±ΖΒΜΊΙΧΕ®ΒΡ“―÷Σ ΐ÷ΒΓΘ’βΨΆΚΟœώ»Ο«ΐΕ·≥Χ–ρΕύΝΥ–©–μΉ‘–≈Θ§»ΟΤδ“β ΕΒΫ…η±Η‘Ύ”κ’ΐ»ΖΒΡΆβΈß…η±ΗΆ®–≈ΓΘΚή‘γ“‘«ΑΘ§‘Ύ«ΐΕ·≥Χ–ρ≥θ ΦΜ· ±Θ§ΕΝ»ΓΦΡ¥φΤς≤ΔΫΪΤδ”κ‘ΛΤΎΫχ––±»ΫœΨΆ «“ΜΦΰΫœΈΣΟτΗ–ΒΡ ¬«ιΓΘ“‘œ¬ «“ΜΗωARM pl011¥°ΩΎ«ΐΕ·≥Χ–ρΒΡάΐΉ”ΘΚ

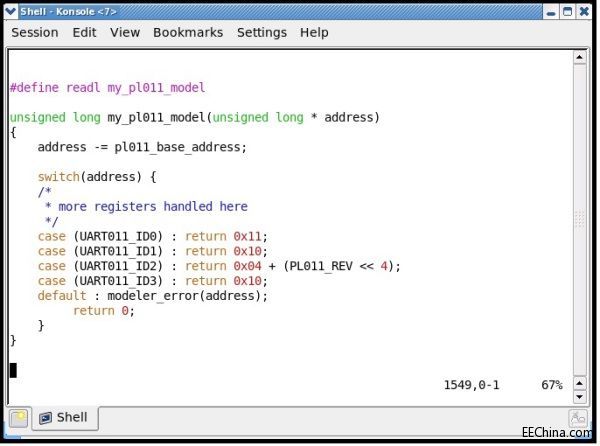

ΆΦ2ΘΚ–Θ―ι“ΜΗω–¬ΆβΈß…η±ΗΒΡIDΦΡ¥φΤς «ΐΕ·≥Χ–ρ¥ζ¬κ Ι”ΟΚξreadlΚΆwritelΕ‘ΦΡ¥φΤςΫχ––ΕΝ–¥ΓΘ’β–©‘ΎlinuxΡΎΚΥ÷–Ε®“εΒΡ«ΐΕ·≥Χ–ρ±ΜΉςΈΣ“Μ÷÷ΖΟΈ ”≤ΦΰΒΡΖΫ ΫΓΘΒΪΦΌ»γΤτΕ·ΝΥ“ΜΗω–¬ΒΡ«ΐΕ·≥Χ–ρΘ§ΡψΨΆΩ…“‘‘Ύ±ΨΒΊΫχ––÷Ί–¬Ε®“εΘ§“‘ΒΟΒΫΥυ–ηΒΡœλ”ΠΓΘάΐ»γ: ΡψΈό–ηΖΟΈ ΒΦ ”≤ΦΰΘ§±ψΡήΩΣ ΦΫχ––»μΦΰΩΣΖΔΓΘΒ±»ΜΘ§Ρψ“≤Ω…“‘≤…»ΓΦΪΕΥΒΡΉωΖ®Θ§ Ι”Ο’β÷÷ΖΫΖ®ά¥Ϋ®ΡΘ“ΜΗωΆξ’ϊΒΡΆβΈß…η±ΗΘ§ΒΪΈό¬έ»γΚΈ«κ≤Μ“Σ≥Δ ‘ΉνΦρΒΞΒΡΆβΈß…η±ΗΘ§“ρΈΣΡ«―υΚή»ί“Ή≤ζ…ζΙ ’œΓΘ“ΜΒ©≥ωœ÷Έ’ ÷ ßΑήΕχ≤…―υ»‘»Μ‘ΎΫχ––Θ§œΒΆ≥Ω…ΡήΜαΕΣ ßΡ≥–©ΖΒΜΊ÷ΒΓΘ ΦΌ»γ¥Π”Ύ–ιΡβΜΖΨ≥Θ§»γQEMUΜρARMΩλΥΌΡΘ–Ά(AFM)ΓΣΓΣΜυ¥ΓΡΘ–ΆΒΡΗΕΖ―Αφ±ΨΘ§ΡψΩ…“‘“ΐΫχΗϋΦ”Η¥‘”ΒΡΡΘ–ΆΓΘAFMΝ§Ϋ”ΝΥSystem-CΘ§œύ±»”Ύ¥φΗυ¥ζ¬κ(stub-code)Θ§’β «“Μ÷÷Ηϋ “Υ”ΎΫ®ΡΘ”≤Φΰ––ΈΣΒΡΜΖΨ≥ΓΘQEMU“≤Ω…“‘ά©’ΙΡΘ–ΆΘ§ΒΪΨ≠―ι≤Μ «ΤΨΩ’Εχά¥ΒΡΘ§–η“ΣΨ≠ΙΐΕύ¥Έ ΒΦυΓΘ”κ–μΕύΩΣ‘¥œνΡΩ“Μ―υΘ§¥ζ¬κΦ¥ «ΈΡΒΒΓΘ»τ Ι”ΟΝΥQEMUΘ§ΒΪ”÷≤Μœκ‘Ύ“ΜΆ≈‘ψΒΡC¥ζ¬κ÷–ΩύΩύ’θ‘ζ≤Δ≥Δ ‘άμ≥ωΆΖ–ςΘ§Ρ«Ο¥“ΜΒ©Ρψ–η“Σ≥§‘Ϋ¥φΗυ¥ζ¬κΘ§ΡψΩ…Ρήœκ“ΣΧχΙΐ’βΗωΫΉΕΈΓΘ ΚήΕύ«ιΩωœ¬Θ§ΈόΖ® Ι”Ο¥φΗυ¥ζ¬κΫχ––―ι÷ΛΘ§…θ÷ΝΝ§ΡψΈΣ»μΦΰ‘Υ––Υυ¥¥Ϋ®ΒΡΗϋΗ¥‘”ΒΡSystem-CΡΘ–Ά“≤ΈόΡήΈΣΝΠΓΘάΐ»γΘ§ΡψΈό¥”ΒΟ÷Σ”≤ΦΰΆ≈Ε”ΚΆ»μΦΰΆ≈Ε”‘Ύ…η±Η÷– Ι”ΟΒΡ «ΖώΈΣΆ§“ΜΗωΦΡ¥φΤς”≥…δΓΘΆ®Ιΐ“ΜΗω≤ΜΜαΉω≥ω»ΈΚΈ“βΝœ÷°ΆβΒΡΖ¥”ΠΒΡΦΡ¥φΤςΘ§ΡψΗυ±ΨΈό¥”―ι÷ΛΤδ…η÷Ο «Ζώ’ΐ»ΖΓΘ»γΙϊΡψΆ§ ±±ύ–¥«ΐΕ·≥Χ–ρΚΆœύ”ΠΒΡΆβΈß…η±ΗΡΘ–ΆΘ§Ρ«Ο¥“≤÷ΜΡή÷ΛΟςΡψΕ‘Εΰ’ΏΒΡάμΫβ «œύΈ«ΚœΒΡΓΘ –ιΡβ―υΜζœΒΆ≥Θ§»γMentor GraphicsΒΡVistaΘ§Ω…”Ο”Ύ¥¥Ϋ®ΡψΥυ–ηΒΡΗϋΗ¥‘”Μ·ΒΡΡΘ–ΆΓΘ“ΜΑψ«ιΩωœ¬Θ§’β–©ΡΘ–ΆΒΡ¥ΠάμΥΌΕ»Ζ«≥ΘΩλΘ§»μΦΰ‘Υ––“≤ΚήΥ≥≥©ΓΘ»γΙϊ”≤ΦΰΆ≈Ε”¥¥Ϋ®ΝΥ–ιΡβ―υΜζΡΘ–ΆΘ§Ρ«Ο¥‘ΎΗΟΡΘ–Ά…œ‘Υ––»μΦΰ ±Θ§±ψΡή―ι÷Λ»μ”≤ΦΰΆ≈Ε”ΒΡ…ηΦΤΙέΒψ «ΖώœύΖϊΓΘΆ®≥Θ«ιΩωœ¬Θ§Εΰ’ΏΒΡ…ηΦΤΙέΒψ «¥φ‘Ύ≤ν“λΒΡΓΘ»τΡήΨΓ‘γΖΔœ÷’β–©≤ν“λΘ§‘ρ‘Ύ…ηΦΤ÷ήΤΎΒΡΚσΤΎΩ…±ήΟβ≤Μ…Ό¬ιΖ≥Θ§»ΟΡψ≤Μ÷Ν”ΎΉΞΩώΓΘ‘Ύ“ΜΗω»μ”≤ΦΰΕΦΚή»ί“ΉΒς ‘ΒΡΙΛΨΏ÷–Θ§“Σ Βœ÷’β“ΜΒψΤδ Β≤Δ≤ΜΡ―ΓΘ –ιΡβ―υΜζ”–“ΜΗωΡψΥυΩΣΖΔΒΡ»μΦΰΆβΈß…η±ΗΒΡΆξ’ϊΙΠΡήΡΘ–ΆΓΘΡψΫΪΡή“‘¥¥Ϋ®÷’ΦΪΡΩ±ξœΒΆ≥Ά§―υΒΡΖΫ Ϋά¥¥¥Ϋ®Ή‘ΦΚΒΡ»μΦΰΘ§ΜΙΡήΖΟΈ Άβ…ηΒΡΦΡ¥φΤςΘ§ΨΆœώ‘Ύ’φ ΒΒΡ”≤Φΰ…œ‘Υ––“Μ―υΓΘ¥ΥΆβΘ§Ά®Ιΐ–ιΡβ―υΜζΩ…“‘÷±Ϋ”≤ιΩ¥’β–©Άβ…ηΦΡ¥φΤςΘ§‘ΎΈό»ΈΚΈΗ…»≈ΒΡ«ιΩωœ¬Θ§Βς ‘Ιΐ≥Χ±δΒΟΗϋ»ί“ΉΓΘΡψΫΪΡή≥δΖ÷ΒΊ±ύ–¥«ΐΕ·≥Χ–ρ≤Δ―ι÷ΛΤδ‘Υ–– «Ζώ’ΐ≥ΘΓΘΡψ…θ÷ΝΜΙΩ…“‘¥÷¬‘ΦΤΥψ≥ωΉήΙ≤Υυ–η“ΣΒΡ ±ΦδΓΘ»ΜΕχΘ§ΨΪ»ΖΒΡ―ι÷Λ ±ΦδΒΡΦΤΥψΘ§ΜΙ–ηΒ»ΒΫ”κ”≤ΦΰΗϋΤΞ≈δΒΡ»μΦΰΈ άΓΘ –η“ΣΦ«ΉΓΒΡ «Θ§–ιΡβ―υΜζ≤Δ≤Μ «’φ’ΐΒΡ”≤ΦΰΘ§Εχ÷Μ «“ΜΗωΡΘ–ΆΓΘΡΘ–Ά(“‘≥Χ–ρΒΡ–Έ Ϋ)–η“Σ”……ηΦΤ Πά¥±ύ–¥Θ§ΒΪ…ηΦΤ ΠΥυ±ύ–¥ΒΡ≥Χ–ρ≈ΦΕϊΜα≥ωœ÷¥μΈσΓΘΜΙ–η“ΣΉΔ“βΒΡ «Θ§”≤Φΰ‘Ύ“ΜΗωΚή≥ιœσΒΡ≤ψΟφ…œΫ®ΡΘΘ§’βΩ…“‘“ΐΖΔ ΒΦ ”≤ΦΰΒΡΈΔΟνΓΔ»¥”÷÷ΝΙΊ÷Ί“ΣΒΡ≤ν“λΓΘ“ρ¥ΥΘ§Φ¥ Ι«ΐΕ·≥Χ–ρΆξ»Ϊ―ι÷ΛΝΥ–ιΡβ―υΜζΘ§ΡψΒΡΙΛΉς»‘»ΜΟΜ”–Ϋα χΘ§ΜΙ–η“Σ‘ΎΗϋœξœΗΒΡ”≤ΦΰΜΖΨ≥÷–Ϋχ––―ι÷ΛΓΘ ”≤ΦΰΆ≈Ε”“―Ψ≠¥¥Ϋ®ΝΥΩ…÷¥––ΒΡ”≤ΦΰΡΘ–ΆΘ§ΉςΈΣ’ΐ≥ΘΩΣΖΔ÷ήΤΎΒΡ“Μ≤ΩΖ÷ΓΘΥϊΟ«‘ΎΦΡ¥φΤς¥Ϊ δΦΕ(RTL) Ι”Ο“Μ÷÷”≤ΦΰΟη ω”ο―‘(HDL)ά¥Οη ωΉ‘ΦΚΒΡ…ηΦΤΓΘΉν÷’Θ§Ά®Ιΐ“ΜœΒΝ–‘Υ––±ύ“κΤςΚΆΖ÷ΈωΤςά¥‘Υ––ΗΟ…ηΦΤΒΡHDLΟη ωΘ§¥¥Ϋ®―ΎΡΘΉι“‘”Ο”Ύ÷Τ‘λΙη–ΨΤ§ΓΘHDLΩ…‘ΎΖ¬’φ»μΦΰ…œ‘Υ––Θ§≤ΔΧαΙ©¥ΐ…ζ≤ζ”≤ΦΰΒΡ ±÷”÷ήΤΎΒΡΉΦ»Ζ‘Υ––Ή¥Χ§ΓΘΈ®“ΜΒΡΈ Χβ «Θ§¥σ≤ΩΖ÷“‘HDLΟη ωΒΡ ΒΧε…ηΦΤΡΘΡβΤς÷ΜΡή“‘ΦΗ °ΜρΦΗΑΌΚ’Ή»ΒΡΤΒ¬ ‘Υ––Θ§ΈόΖ®¥οΒΫ’ΉΚ’Θ§…θ÷ΝΝ§«ßΚ’ΕΦΚήάßΡ―Θ§Ε‘”Ύ»μΦΰ≥Χ–ρ‘±ά¥ΥΒΘ§’β÷÷ΤΒ¬ ΒΆΒΟΦΗΚθΚΝΈό”Ο¥ΠΓΘΆ§―υΒΡHDLΩ…”Ο”Ύ±ύ–¥Ω…±ύ≥Χ¬ΏΦ≠Τς(FPGA)Μρ”≤ΦΰΦ”ΥΌΤςΘ§»γMentor GraphicsΒΡVeloceΓΘFPGAΚΆ”≤ΦΰΦ”ΥΌΤςΩ… Βœ÷HDLΥυΟη ωΒΡ––ΈΣΘ§ΒΪΥϋΟ«ΒΡ‘Υ––ΥΌΕ» «’ΉΚ’ΦΕΒΡΓΘΕ‘”Ύ»μΦΰΙΛ≥Χ Πά¥ΥΒΘ§’β“ΜΥΌΕ»»‘»Μ≤ΜΙΜΘ§ΒΪ «÷Ν…Ό «Ω…”ΟΒΡΓΘ “ΜΒ©Ρψ“―Ψ≠ Ι”ΟΝΥ¥φΗυ¥ζ¬κΚΆ–ιΡβ―υΜζΒΡ»Ϊ≤ΩΙΠΡήΘ§ΦΌ»γ”–“ΜΗω «Ω…”ΟΒΡΘ§Ρ«Ο¥œ¬“Μ≤ΫΨΆ «‘Ύ“ΜΗωΗϋΦ”ΨΪ»ΖΒΡ”≤ΦΰΡΘ–Ά…œ―ι÷ΛΡψ±ύ–¥ΒΡ¥ζ¬κΘ§ΨΏΧεά¥ΥΒΘ§ΨΆ «RTLΓΘΩΣ Φ’β“Μ≤Ϋ÷ηΒΡΉνΦ―ΖΫΖ® «ΫΪ–ιΡβΜζ(QEMUΜρAFM)”κ”≤ΦΰΒΡRTLΡΘ–ΆΫαΚœΤπά¥Θ§‘Ύ»μΫΒΖ¬’φΤςΜρ”≤ΦΰΦ”ΥΌΤς÷–‘Υ––ΓΘMentor GraphicsΒΡ≤ζΤΖWarpcore Ι’β÷÷ΖΫΖ®≥…ΈΣΩ…ΡήΓΘΥϋΫΪ–ιΡβΜζ”κRTL÷¥––ΜΖΨ≥Ϋχ––ΝΥΫαΚœΘ§Ϋω‘ΎRTL±ΜΖΟΈ ±≤≈‘Υ––RTLΖ¬’φΤςΓΘΫΪ–ιΡβΜζ”κΖ¬’φΜΖΨ≥œύΫαΚœΘ§“‘ΦΗΑΌΚ’Ή»ΒΡΤΒ¬ ‘Υ––Θ§Ω¥ΥΤΖηΩώΘ§ΒΪ «‘Ύ≤ΜΙΐΕ»‘Υ––”≤ΦΰΒΡ«ιΩωœ¬Θ§’β÷÷ΉωΖ® «Ω…––ΒΡΓΘ»γΙϊ”≤Φΰ÷Μ‘Υ––“ΜΑΌΆρΗω ±÷”Ήσ”“Θ§÷¥–––ßΙϊΜαΚήΚΟΓΘΆ®≥Θ«ιΩωœ¬Θ§Ζ¬’φΤςΗϋ“Ή”ΎΫ®ΝΔΓΔΖΟΈ ΚΆΒς ‘ΓΘ“ΜΒ©Ρψ–η“Σ Ι”≤Φΰ‘Υ––≥§Ιΐ“ΜΑΌΆρΗω ±÷”÷ήΤΎΘ§‘ρ–η“Σ Ι”Ο”≤ΦΰΦ”ΥΌΤς“‘ Βœ÷Ηϋ”≈ΝΦΒΡ–‘ΡήΓΘ ‘Υ–––ιΡβΜζΚΆ”≤ΦΰΦ”ΥΌΤςΒΡΉιΚœΘ§Μρ“Μ–©Ι©”Π…ΧΥυΈΫΒΡΓΑΜλΚœΖ¬’φ(hybrid-emulation)Γ±Θ§Ω…‘ΎΨΪ»Ζ”≤ΦΰΡΘ–ΆΒΡ“ΜΗω ±÷”÷ήΤΎ÷–ΩλΫίΓΔΦρ±ψΒΊ‘Υ––»μΦΰΓΘ“ΜΑψ’β÷÷≈δ÷ΟΒΡ–‘ΡήΈΣ100 MHzΘ§’β≤Δ≤Μ « Β ±ΒΡΘ§ΒΪ «ΤδΥΌΕ»Ήψ“‘‘Υ––ΚΆΒς ‘Άξ’ϊΒΡ»μΦΰΕ―’ΜΓΘ Ω…Ε‘ΆβΈß…η±ΗΫχ––“Μ–©ΦρΒΞΒΡ≤β ‘Θ§ΒΪ“ΣΕ‘«ΐΕ·≥Χ–ρΫχ––≥ΙΒΉΒΡ―ι÷ΛΘ§ΆβΈß…η±Η÷ΜΫχ––ΓΑΜΖΜΊ(loop-back)Γ±Θ§ΜΙ‘Ε‘Ε≤ΜΙΜΓΘ’β“βΈΕΉ≈ΫΪΤδ”κΆβ≤Ω άΫγœύΝ§Ϋ”Θ§Έό¬έ «Ά®Ιΐ”≤ΦΰΦ”ΥΌΤς…œΒΡI/OΒγά¬Θ§ΜΙ «–ιΡβΡΘ–ΆΜρ”≤ΦΰΦ”ΥΌΤςœύΝ§ΒΡ÷ςΜζΒΡΫ”ΩΎΓΘMentorΒΡ”≤ΦΰΦ”ΥΌΤςœΒΆ≥÷–Θ§ΫΪΤδ≥ΤΈΣco-model÷ςΜζΓΘco-model÷ςΜζΚΆ”≤ΦΰΦ”ΥΌΤς÷°ΦδΩλΥΌ”––ßΒΡΝ§Ϋ”Ε‘”ΎΈ§≥÷ΗΏΥ°ΤΫΒΡ–‘Ρή «÷ΝΙΊ÷Ί“ΣΒΡΓΘ

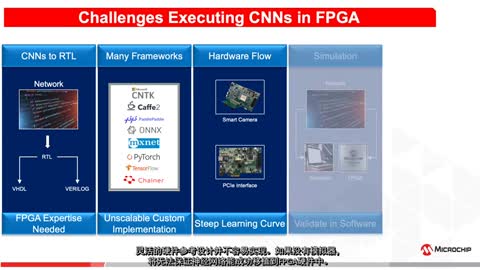

ΆΦ3ΘΚ÷Ί–¬ΈΣ–¬«ΐΕ·≥Χ–ρΕ®“εΕΝ/–¥Κξ÷ΗΝν –η“ΣΉΔ“βΒΡ «Θ§‘Ύ’βΗω≈δ÷Ο÷–Άξ’ϊΒΡ…ηΦΤ≤Μ «‘ΎRTL÷–ΓΘ’β“βΈΕΉ≈œΒΆ≥ΫΪ’ΐ≥ΘΙΛΉςΘ§ΒΪ≤ΜΜα±μœ÷≥ω”κΉν÷’≤ζΤΖœύΆ§ΒΡ–‘ΡήΧΊ’ςΓΘ¥”’βΗω≈δ÷Ο÷–ΡψΡήΩ¥≥ωΡ≥–©ΖΫΟφΒΡ–‘ΡήΘ§»γΡ≥–©ΉιΦΰ÷°ΦδΉΣΜΜΒΡΝςΝΩΓΘΒΪ «œξœΗΒΡ–‘ΡήΖ÷Έω‘ρ–η“ΣΕ‘œΒΆ≥Ϋχ––ΗϋΉΦ»ΖΒΡ±μ¥οΓΘ Β±RTL¥ζ±μ’ϊΗω…ηΦΤ ±Θ§ΡψΫΪΒΟΒΫ’ϊΗωœΒΆ≥“ΜΗω ±÷”÷ήΤΎΒΡΉΦ»ΖΡΘ–ΆΓΘ’βΩ…“‘”Οά¥Ϋχ––œξœΗΒΡ ±ΦδΖ÷Έω≤ΔΒΟ≥ωΆΧΆ¬ΝΩΓΔ―”≥Ό“‘ΦΑœλ”Π ±ΦδΒΡΨΏΧε ΐΨίΓΘ“Σ ΙœΒΆ≥”––ß‘Υ––Θ§Ρψ–η“ΣΫΪΤδΖ≈‘Ύ“ΜΗω”≤ΦΰΦ”ΥΌΤςΜρFPGA‘≠–Ά÷–ΓΘ“ΜΗωΑϋά® ΒΦ »μΦΰΒΡΆξ’ϊœΒΆ≥Θ§ ΒΦ …œ «≤ΜΩ…ΡήΜυ”Ύ»μΦΰΖ¬’φΫχ––Ϋ®ΡΘΒΡΓΘ…θ÷Ν‘Ύ”≤ΦΰΦ”ΥΌΤςΤΫΧ®…œ“≤÷ΜΡή‘Υ––”Ύ“Μ’ΉΚ’Ή»ΓΘ’β‘Ε‘Ε≥§ΙΐΝΥΜυ”Ύ»μΦΰΒΡΖ¬’φΥΌΕ»Θ§ΒΪ”κ ΒΦ ±Φδœύ±»Θ§ΜΙ «“Σ¬ΐΒΟΕύΓΘ ‘Ύ”≤ΦΰΦ”ΥΌΤς…œ‘Υ––…ηΦΤ ±Θ§–η“Σ‘Ύ«Ε»κ Ϋ¥ΠάμΤς÷–Βς ‘»μΦΰΓΘ“ΜΑψ’β÷÷Βς ‘Μα Ι”ΟœΒΆ≥Ω…”ΟΒΡ”≤ΦΰΫ”ΩΎ(άΐ»γJTAGΫ”ΩΎ)Ν§Ϋ””≤ΦΰΒς ‘ΧΫ’κά¥Άξ≥…ΓΘΒΪ «”–“ΜΗωΈ ΧβΘΚΨΓΙήJTAGΚή ΚœΒς ‘ΙΠΡήΈ ΧβΘ§ΒΪΚήΡ―”ΟΥϋά¥Βς ‘–‘ΡήΚΆ ±–ρΈ ΧβΓΘ“ρΈΣΓΑΜλΚœΓ±–ιΡβΜζΚΆΖ¬’φΒΡ–‘ΡήΗϋΗΏ“Μ≥οΘ§ΡψΜαœκ‘Ύ’β…œΟφΒς ‘Υυ”–ΒΡΙΠΡήΈ ΧβΓΘ“ρ¥ΥΘ§Ϋω¥φΒΡΈ ΧβΨΆ « ±–ρΚΆ–‘ΡήœύΙΊΒΡΈ ΧβΝΥΓΘ JTAGΚΆάύΥΤΒΡΒς ‘ΦΦ θ Ι¥ΠάμΤςΫχ»κΒς ‘ΡΘ ΫΘ§»ΜΚσ Ι”ΟΗς÷÷ΦΦ θά¥¥”¥ΠάμΤςΚΆΆβΈßΦΡ¥φΤς÷–ΦλΥς ΐΨίΓΘΦ¥ Ι‘ΎΉν”≈«ιΩωœ¬Θ§’β–©≤ΌΉς“≤÷Ν…Ό–η“ΣΚΡΖ―≥…«ß…œΆρΗω ±÷”ΓΣΆ®≥Θ « ΐ“‘ΑΌΆρΦΤΒΡ ±÷”ΓΘΕχ«“’β–©Βς ‘ ±÷”Ά®≥Θ÷Μ «¥ΠάμΤς ±÷”ΒΡ“Μ–Γ≤ΩΖ÷ΓΘ”…”Ύ‘ΎΒς ‘ ±ΦδΒψ«ΑΚσΒς ‘ΙΛΨΏ“ΐ»κΝΥ ΐ“‘ΑΌΆρΦΤΒΡ≤ΌΉς ±÷”ΒΡ―”≥ΌΘ§“ρ¥ΥΘ§Βς ‘–‘ΡήΚΆ ±–ρΈ Χβ±δΒΟΦΪΈΣάßΡ―ΓΘΩΣΖΔ»Υ‘±“ΜΑψΆ®Ιΐ¥ΠάμΤςΗζΉΌά¥ΜΊΥίΒς ‘Θ§“‘±ήΟβ―”≥ΌΓΘΒΪΦ¥ Ι ’Φ·¥ΠάμΤςΗζΉΌ ΐΨί“≤Μα”ΑœλΒΫΡψ’ΐ‘ΎΙέ≤λΒΡœΒΆ≥ΒΡ‘Υ––ΓΘ Mentor Graphics”–“ΜΩν≤ζΤΖΫ–ΓΑCodelinkΓ±Θ§Ά®ΙΐΥϋΡή ’Φ·‘ΎΖ¬’φ÷–‘Υ––…ηΦΤ ±ΒΡΜΊΥί ΐΨίΘ§άϊ”Ο’β–© ΐΨίΨΆΡή«ΐΕ·¥ΪΆ≥ΒΡ»μΦΰΒς ‘ΓΘ±Ψ÷ …œΥΒΘ§ΡψΩ…“‘ΜώΒΟ¥ΪΆ≥»μΦΰΒς ‘÷–ΒΡΥυ”–ΙΠΡήΓΣ¥ζ¬κΒΞ≤Ϋ÷¥––ΓΔ…ηΝΔΕœΒψΘ§≤ιΩ¥ΡΎ¥φΚΆ±δΝΩΓΘ’β―υΉω±ΘΝτΝΥΖ¬’φœΒΆ≥ΒΡ ±÷”÷ήΤΎΒΡΨΪ»Ζ–‘Θ§ΟΜ”–»ΈΚΈΗ±Ής”ΟΓΘΡψΜΙΨΏ”–Άξ»ΪΒΡ≤Δ––ΕύΚΥΩ…Φϊ–‘ΚΆ‘Υ––”κΜΊΆΥΒΡΡήΝΠΓΘΒΪ–μΕύ–‘ΡήΈ ΧβΚήΡ―‘Ύ‘¥¥ζ¬κ≤ψΟφΒς ‘Θ§Ά®≥ΘΜΙ–η“Σ“ΜΖυΕ‘±»”≤ΦΰΕ·ΉςΒΡΓΔ‘Ύ…ηΦΤ÷–‘Υ––ΒΡ¥ΠάμΤςΒΡΕ·Ής ±Φδ÷α ”ΆΦΓΘCodelink ’Φ·’β–©ΗζΉΌ ΐΨίΘ§≤ΔΒΦ»κMentorΒΡœΒΆ≥Ζ÷ΈωΙΛΨΏΘ§±ψΡήΕ‘’’œ‘ Ψ–‘Ρή ΐΨίΚΆ”≤Φΰ ΐΨίΓΘ“Σ‘Ύ’β“ΜΩΣΖΔΫΉΕΈΕ‘’ϊΗω…ηΦΤΫχ––’οΕœΘ§Ρ«Ο¥’βΩ…Ρή «Ω… ”Μ·–‘ΡήΈ ΧβΚΆ ±–ρΈ ΧβΒΡΉνΦ―ΫβΨωΑλΖ®ΓΘ FPGA‘≠–ΆΆ®≥ΘΜα±»”≤ΦΰΦ”ΥΌΤς‘Υ––ΒΟΗϋΩλΘ§“ρΕχΗϋ≥ΛΒΡ»μΦΰ‘Υ–– ±Φδ «Ω…“‘ Βœ÷ΒΡΘ§ΜΙΩ…ΡήΜαΖΔœ÷ΗϋΕύ…ηΦΤ…œΒΡΈ ΧβΓΘ»μΦΰΒς ‘Ά®≥Θ≤…”ΟJTAGΜρ’ΏάύΥΤΒΡΦΦ θά¥ Βœ÷Θ§ΒΪΕΦ¥φ‘Ύ…œ ωΒΡΗς÷÷Έ ΧβΓΘ‘Ύ”≤ΦΰΒς ‘÷–Θ§FPGAάζά¥ΕΦ¥φ‘ΎΩ… ”–‘”–œόΒΡ»±ΒψΓΘFPGAΙ©”Π…ΧΧαΙ©ΒΡ«Ε»κ Ϋ¬ΏΦ≠Ζ÷Έω“«÷ΜΡήΧαΙ©”–œόΒΡΗζΉΌΖυΕ»ΚΆΫœ«≥ΒΡΗζΉΌ…νΕ»“‘ΦΑΤΒΖ±ΒΡ÷Ί–¬≤βΝΩΘ§Ήν÷’ΒΦ÷¬¬ΰ≥ΛΓΔ«“Ψ≠≥Θ «ΆΜ»ΜΒΡ(ΓΑΜΊΒΫ‘≠ΒψΓ±)÷Ί–¬±ύ“κ(ΉέΚœΒΡΚΆP&R)ΓΘ’β ΙΒΟ‘ΎFPGA÷–Βς ‘±δΒΟΆ¥ΩύΆρΖ÷Θ§Ωί‘ο≤Μ“―ΓΘ–“‘ΥΒΡ «Θ§ –¬ΒΡΦΦ θΟφ –ΝΥΘ§≤ΜΫωΡήΧαΙ©≥…«ß…œΆρ÷÷–≈Κ≈ΒΡΩ…Φϊ ”ΆΦΘ§≤ΔΨΏ±Η…ν»κΗζΉΌ–ΨΤ§ΦΑœΒΆ≥ΦΕΕ·ΉςΒΡΡήΝΠΘ§ΜΙΡήΧαΙ©«ΑΥυΈ¥”–ΒΡ“Ή”Ο–‘ΚΆ«Ω¥σΒΡ‘Υ–– ±Ω…≈δ÷Ο–‘Θ§Ά®Ιΐœϊ≥ΐ¥σΕύ ΐ÷Ί–¬≤βΝΩΚΆΜΊΆΖΒϋ¥ζΒΡ–η«σΘ§ΡήΦΪ¥σΒΊΧαΗΏΒς ‘–߬ ΓΘΨ≠ΙΐΗΡΫχΒΡΒς ‘ΫΪΕ‘ Ι”ΟFPGA‘≠–ΆΒΡΧε―ιΚΆ–߬ ≤ζ…ζΜΐΦΪΒΡ”ΑœλΓΘ

ΆΦ4ΘΚ”≤ΦΰΦ”ΥΌΤς’ΐ±δΒΟ≤ΜΫωΫω÷Μ «Φ”ΥΌΖ¬’φΓΘ ¥”ΦρΒΞΒΡ¥φΗυ¥ζ¬κΩΣ ΦΘ§Ά®Ιΐ“ΜœΒΝ–“ά¥ΈΗϋœξœΗΚΆΆξ’ϊΒΡ”≤ΦΰΡΘ–Άά¥ΆΤΫχΘ§Ω…“‘‘ΎΒΟΒΫ ΒΦ ”≤Φΰ–ΨΤ§÷°«ΑΕ‘»μΦΰΫχ––―ι÷ΛΓΘΡψΩ…“‘≥Λ ±Φδ±Θ≥÷ΉνΗΏ–‘ΡήΡήΚΆΉν“Ή”ΟΒΡΒς ‘ΜΖΨ≥Θ§±Ί“Σ ± Ι”ΟœξœΗΒΡΡΘ–Ά―ι÷ΛœΒΆ≥ΒΡΗςΗωΖΫΟφΓΘΡψΫΪ–η“Σ“ΜΗωΆ®”ΟΒΡΜΖΨ≥ά¥…ζ≥…ΓΔ‘Υ––ΚΆΒς ‘Θ§“‘±ψΚΆΤδΥϊΜΖΨ≥Ϋχ––ΈόΖλΉΣΜΜΓΘΕχ«“’β“≤ΫΪά©’ΙΒΫΉν÷’ΒΡ–ΨΤ§÷–Θ§“ρΈΣΡψΜα–η“ΣΕ‘ ΒΦ ≤ζΤΖΉω“ΜΗωΉν÷’ΒΡ≤β ‘ΓΘ’β“βΈΕΉ≈“ΜΒ©ΡψΡΟΒΫΝΥ ΒΧε‘≠–ΆΘ§–η“ΣΉωΒΡΨΆΫωΫω «»Ζ»œΥυ”–ΙΠΡήΕΦ’ΐ≥Θ‘Υ––ΝΥΓΘ’κΕ‘”≤ΦΰΒΡ≥ιœσΡΘ–ΆΚΆΚσΤΎΨΏ”–ΨΪ»Ζ ±÷”÷ήΤΎΒΡRTL”≤ΦΰΡΘ–ΆΘ§ΉνΡ―ΒΡ»μ”≤ΦΰΫΜΜΞΈ ΧβΫΪ‘Ύ…ηΦΤΫΉΕΈΨΆΡήΒΟ“‘ΫβΨωΓΘ“ΜΒ© ΒΧε―υΜζΨΆ–ςΘ§ΨΆΡή¥σ¥σΦθ…Ό»μΦΰΩΣΖΔΒΡ ±ΦδΓΘ |

Άχ”―Τά¬έ