Cortus与ARM竞争32位安全处理器市场

发布时间:2014-10-10 16:54

发布者:老电工

|

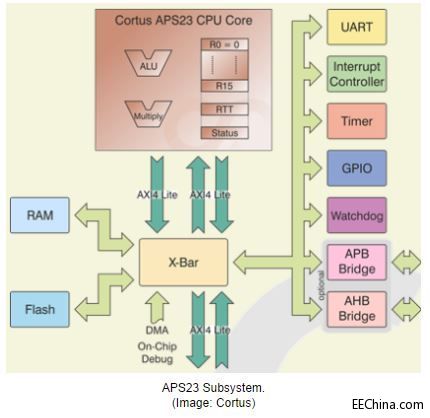

在ARM众多的IP产品占领的微控制器和微处理器IP核市场,如果还有一家公司要与其在32位处理器IP上竞争,这谈何容易?! Cortus,一家总部位于法国蒙彼利埃的32位处理器IP供应商,已经在深度嵌入式市场成功与ARM的Cortex M0竞争了九年。此外,Cortus认为其“极简主义”的方法是其在新兴的连接设备市场扎根的关键。 在上周二,Cortus发布了一系列新的基于其第二代(V2)指令的产品。这家公司表示,它通过提升指令的密度,可以满足新的连接设备的功耗与体积的要求。 为满足SoC上不断降低的功率消耗的设计需求,Cortus已经开发出一套专门的指令集,用来减少系统的指令内存体积。公司的第一套使用V2指令集的产品APS23,就是针对低功耗且不停机/常接收数据的系统,以及对时钟频率要求更低的系统,例如蓝牙低功率应用。

APS23 Subsystem.(Image: Cortus) Cortus总裁CEO Michael Chapman对《电子工程专辑》表示,他们专注于减少指令内存的体积,他将其称为“系统内最大的单一元件”。通过采用V2指令集,Chapman声称相比采用第一代V1指令集的内核,指令的平均密度改善了16%。 与此同时,Cortus还宣布了APS25 IP核,基于V2指令集的第二代产品系列。这款产品是专为需要支持双核和多核系统的更高性能和更复杂的嵌入式系统设计的。 协处理器的接口和安全性 Tirias Research公司的首席分析师Kevin Krewell认为,Cortus提供的授权“有选择且更灵活”,因此与ARM的一战尚有机会。 Cortus的IP能够提供“一个协处理器的接口和安全性”,因而与其最大的竞争对手ARM完全不同。Kevin说,“与此相反,ARM强烈反对提供一个协处理器的接口,同时又紧紧控制着它的指令集。” 据Cortus说,公司的协处理器接口允许其授权者去添加和设计特定的算法,同时让其完全进入CPU的寄存器。授权者即使是完全没有CPU内部的知识,也可以这样做。 这种区分最好的的例子是在安全上的应用。黑莓的子公司Certicom,采用了Cortus的扩展指令集,为其椭圆曲线Galois多字段加密/解密。 Cortus的IP允许 Certicom公司将其安全代码与CPU紧密整合在一起。Krewell表示,这是Cortus在新兴的物联网市场上的一个重要的区别,这些领域的安全性“同等重要”。 Chapman表示,今天的处理器市场正处于计算设备的第三波浪潮中,之前是主机/PC和移动设备。智能设备和可穿戴设备都是基于非标准的操作系统开发的,它们受成本和功耗所驱动。在这样的环境下,“效率起着重要的作用”。此外,“安全性也同样如此”。 成长历史 Cortus是由一群立志于开发更好的嵌入式的CPU的工程师成立的。在物联网被谈起之前,Cortus的天才们,是被Chapman蛊惑去做蓝牙IP--软件、硬件和有关的接口---将这些设计到一个8位的处理器中。 那个产品没有成功,但它的失败给了他灵感去开发一个小的32位的处理器,用“一个较大的地址空间”来完成工作。那颗小CPU的理念现在已经演变成为“为新一波的智能应用提供更好的CPU”的理想所取代。 迄今为止,Cortus,这家专注于更高硅片能效的32位处理器内核供应商,已经签到了38个授权,芯片出货量已经超过了7亿颗。Cortus处理器内核的设计案例包括了今年7月Atmel收购的Newport Media所做的WiFi芯片, Point Chips、 Imagis和LeadingUI公司的触摸屏控制器芯片,e2v、 Microsemi和NextChip的汽车传感器,StarChip的智能卡,以及Discretix的安全芯片。 Cortus的故事与台湾的晶心科技(Andes)类似,它们的业务都是聚焦于嵌入式市场。晶心科技的CPU核目前应用于触摸屏控制器、WIFI和蓝牙、FM、GPS控制器,现在又瞄准了物联网的Sensor hub。 Krewell认为,这个市场仍然为不同的内核提供着很多的机会。 Krewell认为,尽管Andes公司已经在台湾生态系统上,通过它的努力取得了先发的优势,但Cortus这家欧洲的IP供应商还是有机会在安全方面扩展自己的业务。例如,智能卡业务在欧洲已经发展得很成熟,但在安全IC伙伴已经将6-8个安全操作系统植入到它们的内核中。 举例说, APS25能运行在两个CPU上,一个主CPU和一个检查CPU。在那样的架构下,两个内核可以同步执行同样的代码,如果两个结果不一致,就会激发一个警报。Cortus介绍的另一个应用,是安全执行。最好的方法是将安全软件物理上地一个运行在监控CPU上,而应用代码运行在另一个CPU核上。“这样的检查架构是独一无二的,”Krewell说。它可以让CPU内核“非常地可靠,并且非常地安全”。

Lock-step CPU.(Image: Cortus) 为什么要V2指令集? 对于Cortus来说,开发出V2指令集来对付日益复杂的代码非常有必要。“我们做了一个全面的记录和指令的压缩,因此我们能够减少代码的体积,相比之前,CPU能够更复杂地解码,”Chapman说。 Cortus V2的指令集可以混用16位、24位和32位的代码,而不必切换模式。这个指令集相比上一代的V1,增加了在16位和32位指令的混用场景。 然而,Chapman表示Cortus会持续同时提供V1和V2。V1的产品对于小的固件体积来说更有优势。“这两个指令集在二进制上并不兼容,如果我们在一个英特尔的世界中,这将是一个坏消息。”但在深嵌入式应用中并非如此。这两个指令集在源代码层反而是兼容的。“代码的压缩减少了芯片上非易失性内存的面积,这可以大大地降低成本。” 规格 APS23,基于哈佛架构,提供16个32位的寄存器,一个三阶的管道(pipeline)和一个顺行乘法器。它还支持AXI4-Lite总线的Cortus APS外设。 在运算性能方面,这个内核提供了2.83 DMIPS/MHz,和一个1.44 CoreMarks/MHz。为芯片尺寸优化的情况下,APS23 CPU最小可用性起于9.8 千门。动态功耗在90纳米处理工艺内可达12mw/MHz(Cortus对合成和代工方面不作限制)。 APS25也是哈佛架构,提供16个32位的寄存器,一个五除非的管道(pipeline),和一个并行的乘法器。它支持 AXI4总线和Cortus APS外设。 APS25内核中,最多可增加8个协处理器。Cortus的协处理器接口允许被授权者增加定制的协处理器,例如,一个加速度陀螺仪,或是一个信号处理器,而并不需要了解核内部的细节,该公司表示。协处理器指令可插入到C代码作为函数调用。 |

网友评论