ЛљгкADSP-TS101SЕФРзДяаХКХДІРэЯЕЭГЕФЪЕЯж

ЗЂВМЪБМфЃК2010-6-20 11:11

ЗЂВМепЃКzealot

|

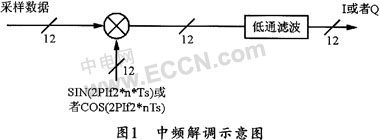

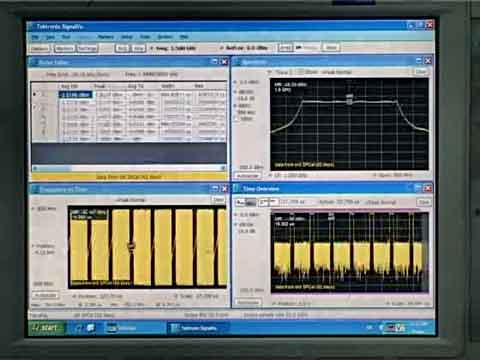

зїЮЊУцЯђЪ§зжаХКХДІРэЕФПЩБрГЬЧЖШыЪНДІРэЦїЃЌDSPОпгаИпЫйЁЂСщЛюЁЂПЩППЁЂПЩБрГЬЁЂЕЭЙІКФЁЂНгПкЗсИЛЁЂДІРэЫйЖШПьЁЂЪЕЪБадКУЕШЬиЕуЁЃРзДяаХКХДІРэЯЕЭГЫљЩцМАЕФжївЊММЪѕАќРЈЪ§ОнжиВЩбљЁЂВЮЪ§ЙРМЦЁЂздЪЪгІТЫВЈЁЂКуащОЏДІРэЁЂТіГхбЙЫѕЁЂздЪЪгІВЈЪјаЮГЩКЭХдАъЖдЯћЕШЃЌЭЈГЃашвЊЭъГЩДѓСПОпгаИпЖШжиИДадЕФЪЕЪБМЦЫуЁЃгЩгкDSPПЩвдРћгУгВМўЫуЪѕЕЅдЊЁЂЦЌФкДцДЂЦїЁЂЙўЗ№змЯпНсЙЙЁЂзЈгУбАжЗЕЅдЊЁЂСїЫЎДІРэММЪѕЕШЬигаЕФгВМўНсЙЙЃЌРДИпЫйЭъГЩFFTЁЂFIRЁЂИДЪ§ГЫМгЁЂЯрЙиЁЂШ§НЧКЏЪ§вдМАОиеѓдЫЫуЕШЪ§зжаХКХДІРэЁЃвђДЫЃЌDSPЗЧГЃЪЪКЯРзДяЪ§зжаХКХДІРэЫуЗЈЕФЪЕЯжЁЃБОЮФЯъЯИЕиНщЩмСЫвЛжжЛљгкADIЙЋЫОИпадФмDSPЁЊADSP-TS101ЕФРзДяаХКХДІРэЯЕЭГЕФОпЬхЪЕЯжЗНЗЈЁЃ 1 ЯЕЭГВПМўМАаХКХДІРэЫуЗЈЕФЪЕЯж БОЯЕЭГЪЧФГРзДяЕФаХКХДІРэЛњЃЌзмЙВга4ПщЕчТЗАхЃЌЗжЮЊФИАхЁЂПЙИЩШХАхЁЂТіГхбЙЫѕАхКЭMTDАхЁЃ 1.1 ФИАх ФИАхжївЊЪЧЮЊЦфЫќШ§ПщЕЅАхЬсЙЉЕчдДЃЌЭЌЪБвВПЩзїЮЊЕЅАхМфаХКХДЋЫЭЕФЧХСКЃЌНЋДІРэЭъЕФЪгЦЕЪ§ОнЫЭЕНЯдЪОЦїЯдЪОЁЃ 1.2 ПЙИЩШХАх ПЙИЩШХАхЕФжївЊЙІФмАќРЈжаЦЕВЩвЊЁЂе§НЛНтЕїгыЕЭЭЈТЫВЈЁЂздЪЪгІХдАъЖдЯћМАХдАъЯћвўЕШЁЃ (1) жаЦЕВЩбљ жаЦЕВЩбљжївЊЪЧЭЈЙ§ADCЖСШЫжаЦЕЪ§ОнЁЃБОЯЕЭГЕФADCВЩгУУРЙњADIЙЋЫОЩњВњЕФ12ЮЛЁЂ40MSPSзЊЛЛЫйТЪЕФИпадФмФЃЪ§зЊЛЛЦїЃЌРДНЋIЁЂQСНТЗФЃФтаХКХвдФГвЛВЩбљТЪзЊЛЛЮЊЪ§зжаХКХЁЃ (2) е§НЛНтЕїгыЕЭЭЈТЫВЈ ИУЙІФмгУгкдкFPGAжаЭъГЩе§НЛНтЕїгыЕЭЭЈТЫВЈЁЃдкИУЯЕЭГжаЃЌFPGAбЁгУЕФЪЧALTERAЙЋЫОЩњВњЕФEP1K100,ЃЌЭМ1ЫљЪОЪЧИУЯЕЭГЕФжаЦЕНтЕїЪОвтЭМЁЃгЩгкЯЕЭГЛсНЋВЩбљаХКХОљзЊЛЛЮЊ1ЃЌ0ЃЌ-1ЃЌ0ЃЌ1ЁЁетбљЕФЪ§зжађСаЃЌЙЪдкЖдВЩбљаХКХНјааНтЕїКѓЃЌЛсЪЙЦфБфЮЊСужаЦЕаХКХЃЌШЛКѓдйЖдЦфзіFIRЕЭЭЈТЫВЈЁЃ (3) здЪЪгІХдАъЖдЯћМАХдАъЯћвў ЪЕЯжЩЯЪіСНЫуЗЈзмЙВвЊгУЕН4ЦЌADSP-TS101SЁЃЮЊСЫМђЛЏЯЕЭГгВМўЁЂМѕЩйDSPЕФЦЌМфСЌЯпЃЌЯЕЭГЕФ4ИіDSPжЎМфгІвдЫЩёюКЯЕФСДТЗЗНЪННјааСДНгЁЃПЩгЩDSP1НЋОЙ§FlRЕЭЭЈТЫВЈКѓЕФСужаЦЕаХКХвдDMAЗНЪНЖСШыЁЃЮЊСЫБЃжЄДІРэЕФЪ§ОнЮЊвЛжЁЭъећЕФЪ§ОнЃЌБОЯЕЭГВЩгУЦЙХвЗНЪНЖСШЫIЁЂQСНТЗЪ§ОнЃЌетбљПЩвдБЃжЄвЛБпЖСЪ§ОнЃЌвЛБпДІРэЃЌЭЌЪБНЋЖЈЕуЪ§ОнзЊЛЛЮЊИЁЕуЪ§ЃЌВЂНЋДІРэНсЙћЫЭЕНDSP2ЁЃDSP2жївЊгУгкМЦЫузюМбХдАъЖдЯћВЮЪ§WIКЭWQЃЌВЂзіХдАъЖдЯћЙЄзїЃЌдйАбДІРэНсЙћЫЭЕНDSP3ЁЃDSP3жївЊИКд№зЊЗЂжїИБЭЈТЗIЁЂQСНТЗЪ§ОнЕНDSP4ЃЌВЂМЦЫужїИБЭЈТЗIЁЂQСНТЗЪ§ОнФЃжЕЕФЙЄзїЃЌЭЌЪБИКд№НЋДІРэНсЙћЫЭЕНDSP4ЁЃDSP4жївЊЭъГЩХдАъЯћвўдЫЫуВЂНЋДІРэНсЙћЗЂЭљТіГхбЙЫѕАхЁЃ

1.3 ТіГхбЙЫѕАх ТіГхбЙЫѕАхжївЊЪЕЯжвдЯТЙІФмЃК (1) ТіГхбЙЫѕ ЭМ2ЫљЪОЮЊТіГхбЙЫѕЕФЪЕЯждРэЭМЁЃТіГхбЙЫѕжївЊНтОіРзДязїгУОрРыгыЗжБцТЪжЎМфЕФУЌЖмЃЌЪЧРзДяЯЕЭГжаНЯЮЊГЩЪьКЭОГЃВЩгУЕФММЪѕЁЃМйШчзмОрРыЕЅдЊЪ§ЮЊ6000ЃЌдђгІНЋЦфВЙЦыжС8192ЕуЃЌШЛКѓзіFFTЁЃашвЊЫЕУїЕФЪЧЃЌетРягУЕНЕФH(k)ЪЧдкMATLABжаЩњГЩКУЕФЃЌШЛКѓДцжќЕНDSPжавдЙЉЦфЕїгУЁЃдкВњЩњH(k)ЪБЃЌВЛЙтвЊВЩгУМгКЃУїДАЕФЗНЗЈЃЌЛЙгІВЩгУЪБгђзлКЯЗЈНјааХдАъвжжЦЁЃОпЬхЫуЗЈПЩВЮМћЯрЙизЪСЯЁЃЦЕгђЯрГЫКѓдйзіIFFTОЭЪЧТіГхбЙЫѕЕФНсЙћЁЃИУЫуЗЈдкDSP1жаЭъГЩКѓЃЌОЭПЩНЋДІРэКѓЕФЪ§ОнЫЭЕНDSP2зіКѓајДІРэЁЃ

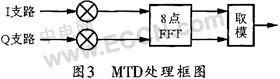

(2) здЪЪгІТЫВЈ здЪЪгІТЫВЈВЩгУздЪЪгІЖўДЮЖдЯћЦїРДвжжЦдЦгъдгВЈЃЌЫќгЩдгВЈВтСПКЭздЪЪгІЖўДЮЖдЯћЦїзщГЩЃЌжївЊдкDSP2жаЭъГЩздЪЪгІТЫВЈВЮЪ§WiКЭWqЕФЙРМЦдЫЫуЃЌВЂзіздЪЪгІТЫВЈЁЃШЛКѓАбДІРэНсЙћЫЭЕНDSP3зіКѓајДІРэЁЃ (3) ЙЬЖЈдгВЈЖдЯћ ЙЬЖЈдгВЈЖдЯћВЩгУЖўДЮЖдЯћЦїЃЌЦфВюЗжЗНГЬЮЊЃК дкDSP3жазіЭъЙЬЖЈдгВЈЖдЯћКѓЃЌОЭПЩНЋНсЙћЫЭDSP4ЁЃ (4) ЯрВЮЛ§Рл ПЩАДЪИСПЯрМгЗНЪНЛ§РлЃЌЛ§РлжЁЪ§ЮЊ16ИіЃЛБОЩшМЦВЩШЁЛЌДАЗНЪНБЃДцБОжЁжмЦкКЭЧА15ИіжЁжмЦкЕФЪгЦЕЪ§ОнЃКЛ§РлКѓГ§вд16ОЭПЩвдШЁЕУЦНОљжЕЁЃDSP4дкзіЭъЯрВЮЛ§РлКѓОЭНЋДІРэЙ§ЕФЪ§ОнЫЭЭљMTDАхзіКѓајДІРэЁЃ 1.4 MTDАх MTDАхЪЕЯжЕФжївЊЙІФмАќРЈMTDДІРэЁЂCFARДІРэКЭЗЧЯрВЮЛ§РлЁЃ (1) MTDДІРэ MTDДІРэжївЊАќРЈ8ЕуFFTГЬађКЭЧѓФЃСНВПЗжЁЃЭМ3ЫљЪОЪЧЦфНсЙЙдРэЭМЃЌЦфжаЧѓФЃПЩВЩгУШчЯТНќЫЦЙЋЪНЃК

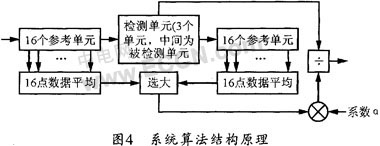

ИУЫуЗЈПЩдкDSP1жаЭъГЩЃЌДІРэНсЙћЫЭШыDSP2ЁЃ (2) CFARДІРэ БОЯЕЭГжаВЩгУЕФЫуЗЈПђЭМШчЭМ4ЫљЪОЃЌCFARДІРэЕФВЮПМЕЅдЊЪ§NЮЊ35ЃЌЧАКѓИї16ИіОрРыЕЅдЊЁЃ

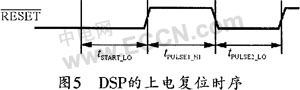

ИУЫуЗЈдкDSP2жаЭъГЩКѓЃЌНЋДІРэНсЙћЫЭЕНDSP3ЁЃ (3) ЗЧЯрВЮЛ§Рл ГЃгУЕФЗЧЯрВЮЛ§РлгаЕЅМЋЕуЛ§РлЦїЁЂЫЋМЋЕуЛ§РлЦїЁЂЛЌДАЛ§РлЦНОљЛ§РлЕШЃЌБОЮФВЩгУМђЕЅЕФЛЌДАЦНОљЛ§РлЃЌЦфжаNs=8ЃЌMrЮЊзмЕуЪ§ЁЃФЧУДЃК ИУЫуЗЈвдМАЯТУцФЃПщжаЕФЧААыВПЗжОљдкDSP3жаЪЕЯжЁЃ (4) ЪфГіФЃПщ ЭЈЙ§ЪфГіФЃПщЯШЭъГЩИЁЕузЊЖЈЕуЃЌдйГЫвдЪЪЕБЯЕЪ§НЋЪ§ОнЗЖЮЇбЙЫѕЕН10ЮЛЃЌШЛКѓАбДѓгкСуЕФеёЗљЪ§ОнЪфГіЕНDЃЏAЕФЪгЦЕЪ§ОнЃЌВЂгУЧАжЁЭЌВНзїЮЊжаЖЯЃЌРћгУDSPЕФDMA0РДНЋЪ§ОнДЋжСFPCAЃЌдйНЋFPGAЫјДцКѓЕФlOЮЛЪгЦЕаХКХЪфГіЕНDACЁЃDACбЁгУОпга10ЮЛгааЇЪ§ОнЮЛЁЂ125MSPSзЊЛЛЫйТЪЕФИпЫйЦїМўAD9750ЃЌНЋЪ§зжаХКХзЊЛЛЮЊФЃФтаХКХКѓЃЌПЩгЩOPA692FдЫЫуЗХДѓЦїЧ§ЖЏЃЌВЂгЩЪгЦЕЕчРТЪфГіЃЌвдЗжБ№НгЕНжїЛњКЭЯдЪОЩшБИЁЃ 2 ЯЕЭГЩшМЦзЂвтЪТЯю 2.1 ЪБжг гЩгкБОЯЕЭГЪЧгЩЖрЦЌADSP-TS101зщГЩЕФЯЕЭГЃЌЫљвдгЩ40 MHzОЇеёВњЩњЕФЪБжгаХКХВЛФмжБНгНгЕНИїDSPКЭFPGAЃЌЖјгІИУЭЈЙ§Ч§ЖЏКѓдйНгЕНИїDSPЃЌЧвЪБжгаХКХЕНИїDSPЕФОрРыгІИУОЁПЩФмНгНќЁЃБОЯЕЭГжаВЩгУЕФЪБжгЧ§ЖЏаОЦЌЮЊIDT49FCT805ЁЃСэЭтЃЌдкPCBВМЯпЪБЃЌгІИУНЋЪБжгаХКХОЁСПВМдкЕиВуЃЌВЂЖдЦфМгвдБЃЛЄЁЃ 2.2 ЕчдД ADSP-TS101гаШ§ИіЕчдДЃЌЦфжаЪ§зж3.3 VгУгкIЃЏOЙЉЕчЃЛЪ§зж1.2 VгУгкDSPФкКЫЙЉЕчЃЛФЃФт1.2 VЮЊФкВПЫјЯрЛЗКЭБЖЦЕЕчТЗЙЉЕчЁЃдЫааЪБвЊЧѓЪ§зж3.3 VКЭЪ§зж1.2 VгІЭЌЪБЩЯЕчЁЃШєЮоЗЈбЯИёЭЌВНЃЌдђгІБЃжЄФкКЫЕчдД1.2 VЯШЩЯЕчЃЌIЃЏOЕчдД3.3 VКѓЩЯЕчЁЃБОЯЕЭГдкЪ§зж3.3VЪфШыЖЫВЂСЊСЫвЛИіДѓЕчШнЃЌЖјдкЪ§зж1.2VЪфШыЖЫВЂСЊСЫвЛИіаЁЕчШнЃЌЦфФПЕФОЭЪЧЮЊСЫБЃжЄ3.3VГфЕчЪБМфДѓгк1.2VГфЕчЪБМфЃЌвдНтОіЩЯЪіЮЪЬтЁЃЯЕЭГгУжїЛњЫЭРДЕФ5 VЕчбЙОЙ§TPS54350ЕУЕН3.3 VКЭ1.2 VЕФЕчбЙЁЃИїЦЌDSPЕФЪ§зж1.2 VЕчдДИїгЩвЛЦЌTPS54350ЙЉИјЁЃ6ЦЌDSPФкВПФЃФт1.2 VдђгЩЭЌвЛDSPаОЦЌЕФVDD (1.2 V)ОТЫВЈЭјТчКѓЬсЙЉЁЃFPGAЕФIЃЏOЕчдДЮЊ3.3 VЃЌПЩгЩЕчдДзЊЛЛКѓжБНгЪЙгУЃЌЦф2.5 VКЫЕчбЙгІИУЕЅЖРгЩвЛЦЌTPS54350РДЪфГіЙЉЕчЁЃ 2.3 ADSPЁЊTS101SЕФИДЮЛ TigerSHARC DSPЕФЩЯЕчИДЮЛНЯЮЊЬиЪтЃЌдкЩшМЦЪБгІГфЗжв§Ц№жиЪгЁЃИУDSPЕФЩЯЕчИДЮЛВЈаЮвЊЧѓШчЭМ5ЫљЪОЁЃетРягІЕБзЂвтЕФЪЧЃЌtstart_LOдкЙЉЕчЮШЖЈжЎКѓЃЌЛЙБиаыДѓгк1 msВХФмНјааВйзїЃКЖјtpulsel_HIдђБиаыДѓгк50ИіЯЕЭГЪБжгжмЦкЧваЁгк100ИіЯЕЭГЪБжгжмЦкЃЛtpulse2_LOБиаыДѓгк100ИіЯЕЭГЪБжгжмЦкЁЃ

ИУDSPЩЯЕчКѓе§ГЃИДЮЛЪБЃЌЕЭЕчЦНГжајЪБМфБиаыДѓгк100ИіЯЕЭГЪБжгжмЦкЁЃБОЯЕЭГВЩгУAlteraЙЋЫОЕФFPGA EPlK100РДВњЩњЩЯЕчИДЮЛВЈаЮКЭЪБађПижЦЁЃгЩгкEPlK100ашвЊвЛИіХфжУаОЦЌЃЌЖјЧвЫќКЭDSPДцдквЛИіЩЯЕчЯШКѓЕФЮЪЬтЁЃвВОЭЪЧЫЕЃЌдкЩЯЕчКѓЃЌШчЙћFPGAаОЦЌдкНјааХфжУЮФМўЕФЖСШыЪБЃЌDSPЩЯЕчШдЮДЮШЖЈЃЌдђгІГфЗжбгГЄtstart_LOЕФЕЭЕчЦНЪБМфЃЌвдБмУтЩЯЕчЮДЮШЖЈЖјFPGAЩЯЕФВЈаЮвбОНсЪјЁЃвђДЫЃЌгІБЃжЄDSPЩЯЕчЮШЖЈЯШгкFPGAаОЦЌХфжУЮФМўЕФЖСШыЃЌДЫЮЪЬтдкЯЕЭГЩшМЦЪБгІгшвдГфЗжжиЪгЃЌЗёдђDSPНЋЮоЗЈе§ГЃЙЄзїЁЃ 3 НсЪјгя БОЮФЯъЯИЕиНщЩмСЫРзДяаХКХДІРэЕФИїжжЫуЗЈдкADSP-TS101жаЕФЪЕЯжЗНЗЈЁЃИУЯЕЭГГфЗжРћгУСЫADSP-TS101SИпЫйЕФдЫЫуФмСІМАЪ§ОнЭЬЭТСПЁЃЮФжаЬжТлСЫDSPгІгУЙ§ГЬжаЕФЪБжгЩшМЦЁЂЕчдДЩшМЦКЭDSPИДЮЛЮЪЬтЃЌвђЖјОпгавЛЖЈЕФЙЄГЬжИЕМвтвхЁЃЪЕМљБэУїЃЌгЩADSPЁЊTS101SЙЙГЩЕФЯЕЭГгВМўНсЙЙМђЕЅЃЌШэМўБраДЗНБуЃЌЖјЧвГЩБОНЯЕЭЁЃФПЧАЃЌИУЯЕЭГвбГЩЙІгІгУгкФГРзДяаХКХДІРэЛњжаЁЃ |

ЭјгбЦРТл