аХКХдкPCBзпЯпжаДЋЪфЪБбг

ЗЂВМЪБМфЃК2014-2-26 15:14

ЗЂВМепЃКeechina

|

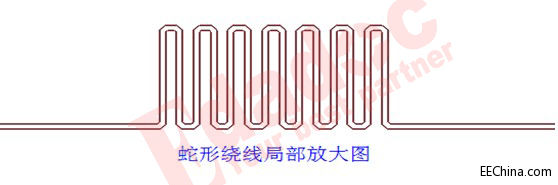

зїепЃКвЛВЉПЦММSIЙЄГЬЪІ еХМЊШЈ еЊвЊЃКаХКХдкУНжЪжаДЋВЅЪБЃЌЦфДЋВЅЫйЖШЪмаХКХдиЬхвдМАжмЮЇУНжЪЪєадОіЖЈЁЃдкPCBЃЈгЁЫЂЕчТЗАхЃЉжааХКХЕФДЋЪфЫйЖШОЭгыАхВФDKЃЈНщЕчГЃЪ§ЃЉЃЌаХКХФЃЪНЃЌаХКХЯпгыаХКХЯпМфёюКЯвдМАШЦЯпЗНЪНЕШгаЙиЁЃЫцзХPCBзпЯпаХКХЫйТЪдНРДдНИпЃЌЖдЪБађвЊЧѓНЯИпЕФдДЭЌВНаХКХЕФЪБађдЃСПдНРДдНЩйЃЌвђДЫдкPCBЩшМЦНзЖЮзМШЗжЊЕРPCBзпЯпЖдаХКХЪБбгЕФгАЯьБфЕФгШЮЊживЊЁЃБОЮФЛљгкЗТецЗжЮіDKЃЌДЎШХЃЌЙ§Пз,ЩпаЮШЦЯпЕШвђЫиЖдаХКХЪБбгЕФгАЯьЁЃ 1.в§бд аХКХвЊФме§ГЃЙЄзїЖМБиаыТњзувЛЖЈЕФЪБађвЊЧѓЃЌЫцзХаХКХЫйТЪЩ§ИпЃЌЪ§зжаХКХЕФЗЂеЙОРњСЫДгЙВЭЌВНЪБжгЕНдДЭЌВНЪБжгвдМАДЎааЃЈserdesЃЉаХКХЁЃдкЕБНёЕФЯћЗбРрЕчзгЃЌЭЈаХЗўЮёЦїЕШаавЕЃЌдДЭЌВНКЭДЎаааХКХеМОнСЫКмДѓЕФБШжиЁЃДЎаааХКХБШШчГЃМћPCIEЃЌSASЃЌSATAЃЌQPIЃЌSFP+ЃЌXUAIЃЌ10GBASE-KRЕШаХКХЃЌдДЭЌВНаХКХБШШчDDRаХКХЁЃ ДЎаааХКХдкЗЂЫЭЖЫНЋЪ§ОнаХКХКЭЪБжгЃЈCLKЃЉаХКХЭЈЙ§БрТыЗНЪНвЛЦ№ЗЂЫЭЃЌдкНгЪеЖЫЭЈЙ§ЪБжгЪ§ОнЛжИДЃЈCDRЃЉЕУЕНЪ§ОнаХКХКЭЪБжгаХКХЁЃгЩгкЪБжгЪ§ОндкЭЌвЛИіЭЈЕРДЋВЅЃЌДЎаааХКХЖдКЭЖджЎМфдкPCBЩЯДЋЪфбгЪБвЊЧѓНЯЕЭЃЌжївЊвРППЫјЯрЛЗЃЈPLLЃЉКЭаОЦЌЕФЪБжгЪ§ОнЛжИДЙІФмЁЃ дДЭЌВНЪБжгжївЊЪЧDDRаХКХЃЌдкDDRЩшМЦжаЃЌDQЃЈЪ§ОнЃЉаХКХВЮПМDQSЃЈЪ§ОнбЁЭЈЃЉаХКХЃЌCMDЃЈУќСюЃЉаХКХКЭCTLЃЈПижЦЃЉаХКХВЮПМCLKЃЈЪБжгЃЉаХКХЃЌгЩгкDQЕФЫйТЪЪЧCMD&CTLаХКХЫйТЪ2БЖЃЌЫљвдDQаХКХКЭDQSаХКХжЎМфЕФДЋЪфбгЪБвЊЧѓБШCMD&CTLКЭCLKжЎМфЕФвЊЧѓИќИпЁЃФПЧАЪаГЁЩЯжїСїЕФЮЊDDR1/ DDR2/ DDR3ЁЃDDR4дЄМЦдк2015ФъНЋГЩЮЊЯћЗбРрЕчзгЕФжївЊЩшМЦЃЌЫцзХDDRаХКХЫйТЪЕФВЛЖЯЬсИпЃЌдкDDR4ЩшМЦжаЬиБ№ЪЧDQКЭDQSжЎМфДЋЪфЪБбгЖдЩшМЦепЬсГіИќИпЕФЬєеНЁЃ дкPCBЩшМЦЕФЪБКђЮЊСЫЪБађЕФвЊЧѓашвЊЖддДЭЌВНаХКХзівЛаЉЕШГЄЃЌвЛаЉЩшМЦЙЄГЬЪІКіТдСЫетИіаХКХЕШГЄЦфЪЕЪЧвЛИіЪБбгЕШГЄЃЌЛђепЫЕЪЧвЛИіЁЎЪБМфЕШГЄЁЏЁЃ 2.ДЋЪфЪБбгМђНщ Time delayгжНаЪБбг(TD)ЃЌЭЈГЃЪЧжИЕчДХаХКХЛђепЙтаХКХЭЈЙ§ећИіДЋЪфНщжЪЫљгУЕФЪБМфЁЃдкДЋЪфЯпЩЯЕФЪБбгОЭЪЧжИаХКХЭЈЙ§ећИіДЋЪфЯпЫљгУЕФЪБМфЁЃ Propagation delayгжНаДЋВЅбгГй(PD)ЃЌЭЈГЃЪЧжИЕчДХаХКХЛђепЙтаХКХдкЕЅЮЛГЄЖШЕФДЋЪфНщжЪжаДЋЪфЕФЪБМфбгГйЃЌгыЁАДЋВЅЫйЖШЁБГЩЗДБШР§ЃЈЕЙЪ§ЃЉЙиЯЕЃЌЕЅЮЛЮЊЁАPs/inchЁБЛђЁАs/mЁБЁЃ ДгЖЈвхжаПЩвдПДГіЪБбг=ДЋВЅбгГй*ДЋЪфГЄЖШ(L) Цфжа v ЮЊДЋВЅЫйЖШЃЌЕЅЮЛЮЊinch/psЛђm/s c ЮЊецПежаЕФЙтЫйЃЈ3X108 m/sЃЉ ІХr ЮЊНщЕчГЃЪ§ PD ЮЊДЋВЅбгГйЃЌЕЅЮЛЮЊPs/inchЛђs/m TD ЮЊаХКХЭЈЙ§ГЄЖШЮЊLЕФДЋЪфЯпЫљВњЩњЕФЪБбг LЮЊДЋЪфЯпГЄЖШЃЌЕЅЮЛЮЊinchЛђm ДгЩЯУцЙЋЪНПЩвджЊЕРЃЌДЋВЅбгГйжївЊШЁОігкНщжЪВФСЯЕФНщЕчГЃЪ§ЃЌЖјДЋВЅЪБбгШЁОігкНщжЪВФСЯЕФНщЕчГЃЪ§ЁЂДЋЪфЯпГЄЖШКЭДЋЪфЯпКсНиУцЕФМИКЮНсЙЙЃЈМИКЮНсЙЙОіЖЈЕчГЁЗжВМЃЌЕчГЁЗжВМОіЖЈгааЇНщЕчГЃЪ§ЃЉЁЃбЯИёРДЫЕЃЌВЛЙмЪЧбгГйЛЙЪЧЪБбгЖМШЁОігкЕМЬхжмЮЇЕФгааЇНщЕчГЃЪ§ЁЃдкЮЂДјЯпжаЃЌгааЇНщЕчГЃЪ§ЪмКсНиУцЕФМИКЮНсЙЙгАЯьБШНЯДѓЃЛЖјДЎШХЃЌЦфгааЇНщЕчГЃЪ§ЪмЦцХМФЃЪНЕФгАЯьНЯДѓЃЛВЛЭЌШЦЯпЗНЪНгааЇНщЕчГЃЪ§ЪмЦфШЦЯпЗНЪНЕФгАЯьЁЃ 3.ЗТецЗжЮіЙ§ГЬ 3.1 ЮЂДјЯпКЭДјзДЯпДЋЪфЪБбг PCBжаЮЂДјЯпЪЧжИзпЯпжЛгавЛИіВЮПМУцЃЌШчЯТЭМ1ЃЛДјзДЯпЪЧжИзпЯпга2ИіВЮПМУцЃЌШчЯТЭМ2.

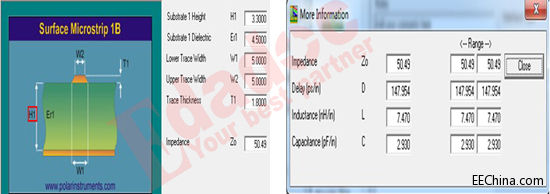

ДјзДЯпгЩгкЕчДХГЁЖМБЛЪјИПдкСНИіВЮПМУцжЎМфЕФАхВФжаЃЌЫљвдзпЯпЕФгааЇНщЕчГЃЪ§ЮЊАхВФЕФНщЕчГЃЪ§ЁЃ ЮЂДјЯпЛсЕМжТВПЗжЕчДХГЁБЉТЖдкПеЦјжаЃЌПеЦјЕФЯрЖдНщЕчГЃЪ§дМЮЊ1.0006ЃЌАхВФШчГЃЙцFR4ЕФНщЕчГЃЪ§ЮЊ4.2ЃЌФЧУДЮЂДјЯпЕФгааЇНщЕчГЃЪ§дк1КЭ4.2жЎМфЃЌПЩвдРћгУЯТУцЕФЙЋЪНМЦЫуЮЂДјЯпЕФгааЇНщЕчГЃЪ§ЁОCollins,1992ЁПЃК ІХe = (ІХr +1)/2 + (ІХr -1)/2ЃЈ1+12H/WЃЉ-1/2 + F -0.217(ІХr -1)T/ЁЬWH 3.1 F = 0.02 (ІХr -1)ЃЈ1-W/HЃЉ2 (W/H < 1) F= 0 (W/H >1) 3.2 ЦфжаЃЌІХe ЮЊгааЇНщЕчГЃЪ§ЃЌ ІХr ЮЊЕчТЗАхВФСЯЕФНщЕчГЃЪ§ЃЌHЮЊЕМЯпИпгкЕиЦНУцЕФИпЖШЃЌWЮЊЕМЯпПэЖШЃЌTЮЊЕМЯпКёЖШЁЃ

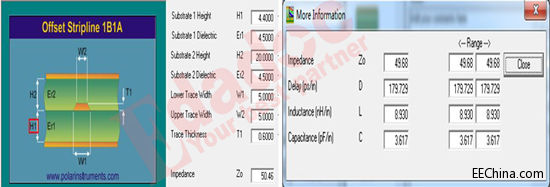

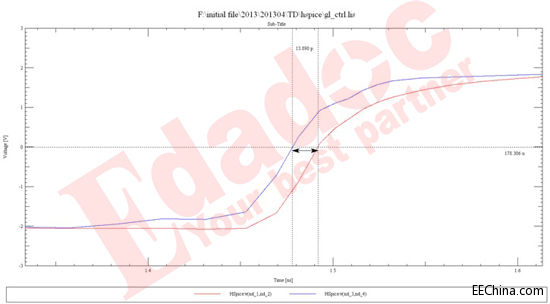

ЭМ4 ЮЂДјЯпВуЕўгыЪБбг

ЭМ5 ДјзДЯпВуЕўКЭЪБбг дкЭМ4КЭЭМ5ЕФВуЕўНсЙЙЯТЃЌ1000milЕФзпЯпЪБбгВю=179.729ps-147.954ps=31.775psЃЌПЩвдПДГіетИіВюОрЪЧЗЧГЃДѓЕФЁЃдкзідДЭЌВНЕФDDRЭЌзщЕШГЄЪБКђжЛПМТЧЮяРэЕШГЄЛсДјРДКмбЯжиЕФ'ЪБМфВЛЕШГЄЁЃ 3.2 зпЯпКЭЙ§ПзДЋЪфЪБбг дкPCBЩшМЦЪБКђЃЌОГЃЛсгіЕНзпЯпЛЛВуЃЌзпЯпЛЛВуБиаыНшжњгкЙ§ПзЁЃЕЋГЄЖШЯрЕШЕФЙ§ПзКЭзпЯпжЎМфЕФЪБбгВЂВЛЯрЕШЁЃЙ§ПзЕФЪБбгПЩвдгУЪН3.3БэЪО TD_via=ЁЬLC 3.3 ЦфжаTD_viaБэЪОаХКХОЙ§Й§ПзЕФЪБбгЃЌLБэЪОЙ§ПзЕФМФЩњЕчИаЃЌCБэЪОЙ§ПзЕФМФЩњЕчШнЁЃДгЪН3.3ПЩвдПДГіМФЩњЕчШнКЭМФЩњЕчИаЖМЛсЕМжТЙ§ПзЕФДЋЪфЪБбгБфДѓЁЃЖјВЛЭЌЙ§ПзНсЙЙМФЩњВЮЪ§вВЛсЗЂЩњИФБфЁЃЯТУцЭЈЙ§ЗТецЗжЮіЙ§ПзЪБбгКЭДЋЪфЯпЪБбгЪБМфЕФЦЋВюЁЃ

ЭМ6 Й§ПзНсЙЙМАМФЩњВЮЪ§ ШчЭМ6ЫљЪОЙ§ПзНсЙЙЪБбгПЩвдИљОнЪН3.3МЦЫуГіЃК TD_via=ЁЬLC=sqrЃЈ0.4021pf*1326.2pHЃЉ=23.1ps ЪН3.4 гЩЪН3.4ПЩвдПДГіЃЌНсЙЙШчЭМ6ЫљЪОЙ§ПзЕФДЋЪфЪБбгЮЊ23.1psЁЃЖјЖдгкЦеЭЈFR4АхВФЕФЮЂДјЯпЃЌ1.6mmзпЯпДЋЪфЪБбгдМЮЊ11psЃЌЖдгкДјзДЯпдМЮЊ12.5psЁЃЭЈЙ§МЦЫуПЩвдПДГіЯрЭЌГЄЖШЕФзпЯпКЭЙ§ПзжЎМфЕФЪБбгЯрВюЪЧЗЧГЃДѓЕФЁЃвђДЫЖдЩшМЦЙЄГЬЪІРДНВЩшМЦЕФЪБКђОЁСПзіЕНвдЯТСНЕуЃК 1ЃЉашвЊзіЕШГЄЕФаХКХвЊОЁСПзпЭЌВуЃЌЛЛВуЪБашвЊзЂвтзмЕФГЄЖШвЊБЃГжЯрЕШВЂЧвУПВузпЯпЖМашвЊЕШГЄЁЃ 2ЃЉ ашвЊЕШГЄЕФаХКХзпЯрЭЌзпЯпВуПЩвдБЃГжЙ§ПзЕФЪБбгвЛжТ,ДгЖјЯћГ§Й§ПзЪБбгВЛвЛжТДјРДЕФгАЯьЁЃ 3.3 ДЎШХЖдаХКХЪБбгЕФгАЯьЁЃ PCBАхЩЯЯпгыЯпЕФМфОрКмНќЃЌзпЯпЩЯЕФаХКХПЩвдЭЈЙ§ПеМфёюКЯЕНЦфЯрСкЕФвЛаЉДЋЪфЯпЩЯШЅЃЌетИіЙ§ГЬОЭНаДЎШХЁЃДЎШХВЛНіПЩвдгАЯьЕНЪмКІЯпЩЯЕФЕчбЙЗљжЕЃЌЭЌЪБЛЙЛсгАЯьЕНЪмКІЯпЩЯаХКХЕФДЋЪфЪБбгЁЃ

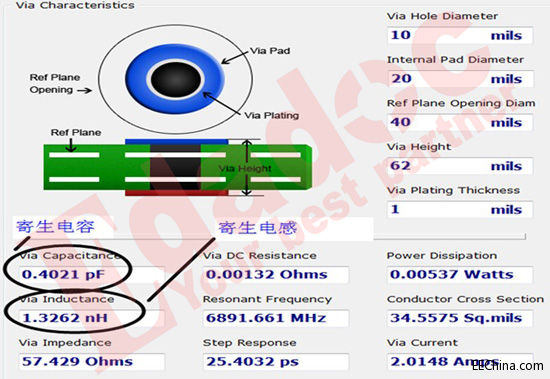

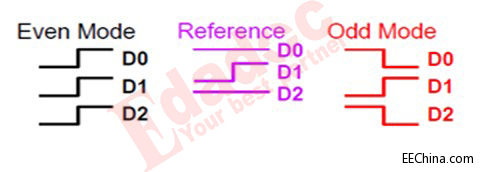

ЭМ7 ДЎШХЭиЦЫЭМ ШчЭМ7ДЎШХЭиЦЫЭМЫљЪО,МйЩшга3ИљЯрЛЅёюКЯЕФДЋЪфЯпЃЌжаМфЕФвЛИљЯпЃЈЭМ8жаD1ЃЉЮЊЪмКІЯпЃЌСНБпЕФЯпЃЈЭМ8жаD0&D2ЃЉЮЊЙЅЛїЯпЁЃЗТецжаЫљМгЕФМЄРјдДЮЊЭМ8ЫљЪОЃЌЗжЮЊШ§жжЧщПіЃК 1ЃЌМйЩшСНБпЕФЙЅЛїЯпжаУЛгааХКХЃЌМДВЛДцдкДЎШХЃЌДЫжжЧщПізїЮЊВЮПМЛљзМЯпЃЈReferenceЃЉЃЛ 2ЃЌМйЩшЙЅЛїЯпКЭЪмКІЯпЧаЛЛзДЬЌвЛжТЃЌДЫжжЧщПіЮЊХМФЃЃЈEven ModeЃЉ 3ЃЌМйЩшЙЅЛїЯпКЭЪмКІЯпЧаЛЛзДЬЌЯрЗДЃЌДЫжжЧщПіЮЊЦцФЃЃЈOdd ModeЃЉ

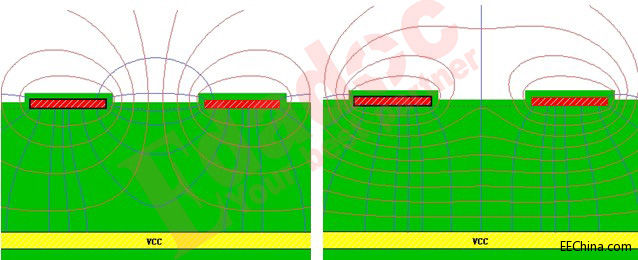

ЭМ8 ДЎШХЗТецжаМЄРј ЦцХМФЃЪНПеМфЕчДХГЁЗжВМЃЈШчЭМ9&ЭМ10ЫљЪОЃЉВЛЭЌЃЌДгЖјЕМжТСЫДЋЪфЯпжмЮЇЕФгааЇНщжЪЕчГЃЪ§ВЛЭЌЃЌгааЇНщЕчГЃЪ§ЕФВЛЭЌзюжеДјРДСЫдкВЛЭЌМЄРјдДЕФЧщПіЯТаХКХДЋВЅЫйЖШВЛЭЌЁЃ

ЭМ9 ЦцФЃЕчДХГЁЗжВМ ЭМ10 ХМФЃЕчДХГЁЗжВМ ЗТецНсЙћШчЯТЭМ11ЫљЪОЃЌЦфжаРЖЩЋЮЊЕквЛжжМЄРјЫљЖдгІЕФВЮПМЛљзМЯпЃЌЦфжмЮЇУЛгаЦфЫќаХКХЯпЕФгАЯьЃЛКьЩЋЯпЮЊЕкЖўжжМЄРјЫљЖдгІЕФНгЪеЖЫВЈаЮЃЛТЬЩЋЮЊЕкШ§жаЧщПіЫљЖдгІЕФНгЪеЖЫВЈаЮЁЃТЬЩЋВЈаЮзюдчЕНДяНгЪеЖЫЃЌЖјКьЩЋЕФВЈаЮзюКѓЕНДяНгЪеЖЫЃЌЪЧгЩгкЦцФЃЕФДЋЪфЫйЖШБШХМФЃПщЁЃ

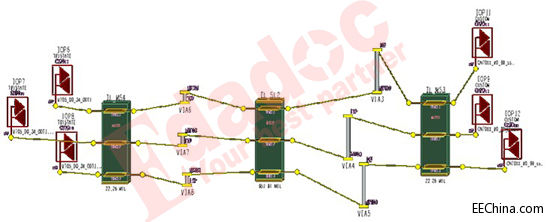

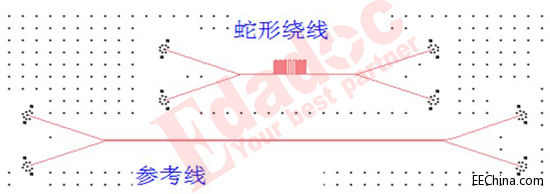

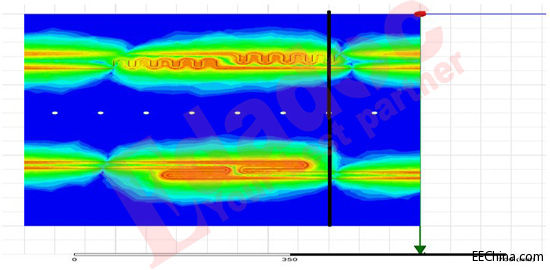

ЭМ11 ДЎШХЗТецНсЙћ ДгЩЯУцЕФЗТецНсЙћПЩвдПДГіаХКХЯпжмЮЇЕФЙЅЛїЯпЛсЖдаХКХЯпЕФДЋЪфЪБбгЕНРДгАЯьЃЌШчЙћЩшМЦДІРэВЛЕБЃЌЕМжТДЋЪфЪБбгЦЋВюНЯДѓзюжеЛсЕМжТЯЕЭГЙЄзїВЛЮШЖЈЁЃдкЩшМЦЕФЪБКђвЊОЁСПМѕаЁетжжгАЯьЃЌПЩвдДгвдЯТМИЕуПМТЧЃК 1ЃЌРДѓЯпМфОрЁЃЯпМфОрдНДѓЃЌЯрСкзпЯпМфЕФгАЯьОЭдНаЁЃЌзпЯпМфОрОЁСПТњзу3WддђЁЃ 2ЃЌЪЙёюКЯГЄЖШОЁСПЖЬЁЃЯрСкДЋЪфЯпЦНаазпЯпГЄЖШдНГЄДЎШХдНДѓЃЌзпЯпЪБКђОЁСПМѕаЁЯрСкЯпЦНаазпЯпГЄЖШЃЛЖдгкЯрСкВузпЯпОЁСПВЩгУЯрСкВуДЙжБзпЯпЁЃ 3ЃЌзпЯпОЁСПзпдкДјзДЯпЁЃЮЂДјЯпЕФДЎШХЯрЖдДјзДЯпНЯДѓЃЌДјзДЯпзпЯпПЩвдМѕаЁДЎШХЕФгАЯьЁЃ 4ЃЌБЃГжЭъећЛиСїЦНУцЃЌБмУтПчЗжИюЃЌзпЯпКЭВЮПМУцОЁСПНєёюКЯЁЃ 3.4 ШЦЯпЗНЪНЖдаХКХЪБбгЕФгАЯь дкPCBЩшМЦЪБКђЃЌгааЉЩшМЦШЫдБЮЊСЫТњзуЕШГЄвЊЧѓЛсЖдзпЯпНјааШЦЯпЃЌКмЩйгаЩшМЦШЫдБЛсПМТЧЕНВЛЧЁЕБЕФШЦЯпвВЛсгАЯьДЋЪфЯпЪБбгЁЃЮЊСЫбщжЄШЦЯпЖдДЋЪфЯпЪБбгЕФгАЯьЃЌЮвУЧЙЋЫОаХКХЭъећадЭХЖгЃЈSIзщЃЉЩшМЦГіВтЪдАхНјааЪЕВтЁЃШчЯТЭМ12ЫљЪОЃЌЩпаЮШЦЯпКЭВЮПМжБЯпзпдкЯрЭЌЕФзпЯпВуЃЌСНепЯпПэЯпМфОрвдМАЮяРэГЄЖШЭъШЋЯрЭЌЃЌЩпаЮШЦЯпЕФОжВПЗХДѓЭМШчЯТЭМ13ЫљЪОЁЃ

ЭМ12 ЩпаЮШЦЯпКЭВЮПМзпЯп

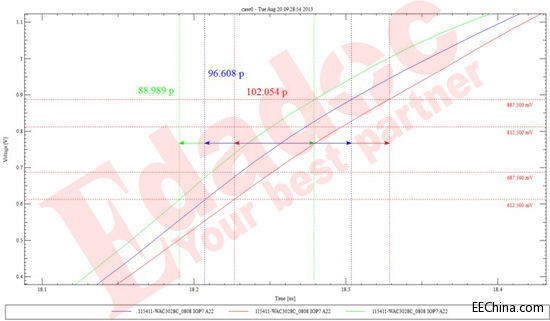

ЭМ13 ЩпаЮШЦЯпОжВПЗХДѓЭМ ЪЕВтНсЙћШчЯТЭМ13ЫљЪОЃЌЦфжаКьЩЋЯпЮЊВЮПМзпЯпЃЌРЖЩЋЕФЯпЮЊЩпаЮШЦЯпЕФзпЯпЃЌДгНсЙћПЩвдПДГіЃЌЩпаЮШЦЯпЕФаХКХДЋЪфЫйЖШЛсБШжБЯпВЮПМЯпЕФЫйЖШвЊПьЃЌСНепЯрВюСЫ13.89psЁЃетЪЧгЩгкЩпаЮШЦЯпППЕФЬЋНќЃЌЦНааЕФёюКЯГЄЖШЬЋГЄЃЌаХКХдкЩпаЮШЦЯпЩЯЕФздёюКЯЕМжТаХКХДЋВЅЫйЖШНЯПьЁЃ

ЭМ13 ЪЕВтНсЙћ ЭЈЙ§3DЕчДХГЁЗТецШэМўвВПЩвдПДГіетжжЩпаЮШЦЯпКЭжБЯпМфДЋЪфЫйЖШВЛЭЌЃЌШчЯТЭМ14ЫљЪОЃКСНжжВЛЭЌЕФШЦЯпЪЧЮяРэЕШГЄЕФЃЌПЩвдПДГіЯТУцвЛжжШЦЯпЗНЪНгЩгкШЦЯпППЕФНЯНєЃЌЖјЧвЦНааёюКЯГЄЖШвВГЄЃЌПЩвдПДГіЯТУцвЛжжШЦЯпЗНЪНаХКХДЋЪфЕФЛсПьвЛЕу

ЭМ14 ЗТецНсЙћ ДгЩЯУцЕФЗТецВтЪдПЩвдПДГіЃЌВЛЭЌШЦЯпЗНЪНЖдаХКХЪБбггАЯьЛЙЪЧБШНЯДѓЕФЃЌЮЊСЫМѕаЁгЩгкШЦЯпДјРДЕФЪБбгЕФгАЯьЃЌПЩвдПМТЧвдЯТМИЕуЃК 1ЃЌдкPCBЩшМЦЪБКђОЁСПМѕЩйВЛБивЊЕФШЦЯпЃЌБШШчДЎаааХКХВюЗжЖдКЭВюЗжЖджЎМфУЛгаБивЊзіЕШГЄЁЃ 2ЃЌдіДѓШЦЯпМфМфОрЃЌОЁСПТњзуЕЅИљШЦЯпМфОрДѓгк5HЃЈHЮЊЯпЕНзюНќВЮПМУцЕФОрРыЃЉЃЌВюЗжШЦЯпДѓгк3HЃЈHЮЊЯпЕНзюНќВЮПМУцЕФОрРыЃЉЁЃ 3ЃЌМѕаЁШЦЯпМфЦНаазпЯпГЄЖШЁЃ 4.аЁНс дкPCBЩшМЦЪБКђвЊНЋЕШГЄЕФЩшМЦЙлФюж№ВНЯђЕШЪБЩшМЦзЊБфЃЌдкЖдЪБађЛђепЕШГЄвЊЧѓИпЕФЩшМЦгШЦфашвЊзЂвтДЎШХЃЌШЦЯпЗНЪНЃЌВЛЭЌВузпЯпЃЌЙ§ПзЪБбгЕШЗНУцЖдЪБађЕФгАЯьЁЃЗсИЛЕФSIЃЈаХКХЭъећадЃЉжЊЪЖКЭе§ШЗЕФЗТецЗНЗЈПЩвдАяжњЩшМЦШЅЦРЙРPCBАхЩЯЕФДЋЪфЪБбгЃЌДгЖјЬсИпЩшМЦЕФжЪСПЁЃ |

ЭјгбЦРТл